热门标签

热门文章

- 1Unity 设置 Text 颜色 #FF7B2A_unity代码修改文字颜色

- 2Sequelize:TimeoutError:ResourceRequest超时_timeouterror: resourcerequest timed out

- 3Java中的浅拷贝与深拷贝_java是深拷贝还是浅拷贝

- 4Poi-tl自定义插件导出word--------动态合并单元格与添加颜色_dynamictablerenderpolicy设置单元格边框颜色

- 5mysql编程C语言vs_mysql

- 6windows系统中,通过LOAD到入csv格式的文件到neo4j中,如何写文件路径_neo4j load csv绝对路径怎么写

- 7Mysql Optimizer_Trace(优化器追踪)_mysql optimizer trace

- 8android读取应用列表权限,Android获取系统应用及安装应用的权限列表

- 9都在讲大模型多么神奇,让更多人用得起才能真正落地

- 10数据库期末考试

当前位置: article > 正文

PCIE收发时序了解_pcie tlp

作者:IT小白 | 2024-05-25 11:32:30

赞

踩

pcie tlp

一、Pcie的发送时序

这里介绍的是Xilinx VIVADO 软件集成的7 Series Integrated Block for PCI Express.硬核,它与用户通信用 AXI4 接口。

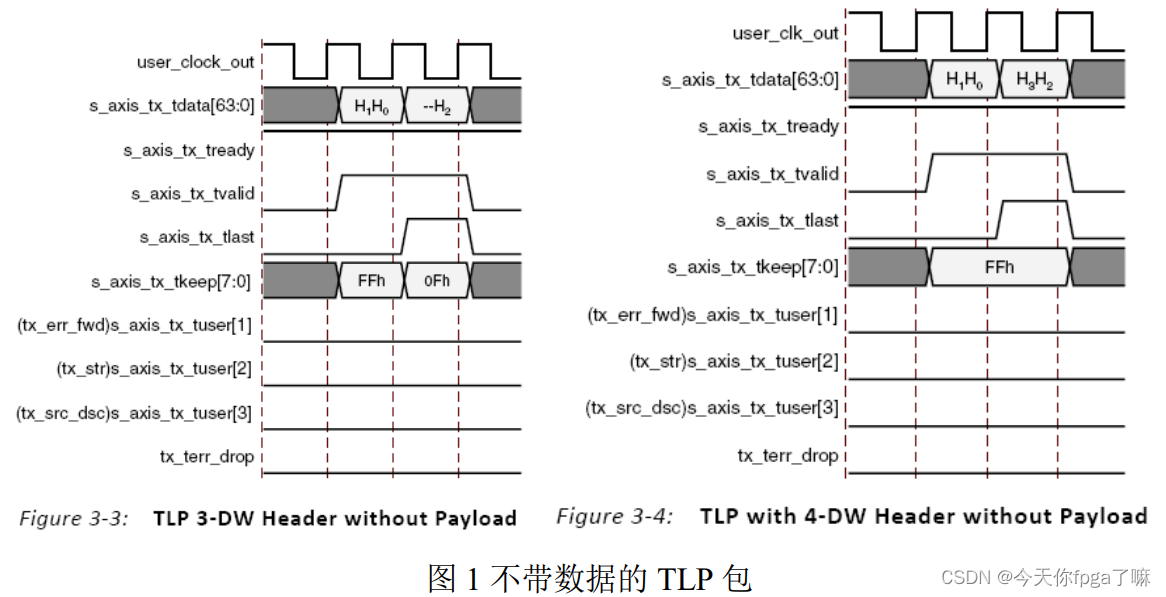

1.1 不带数据的TLP包

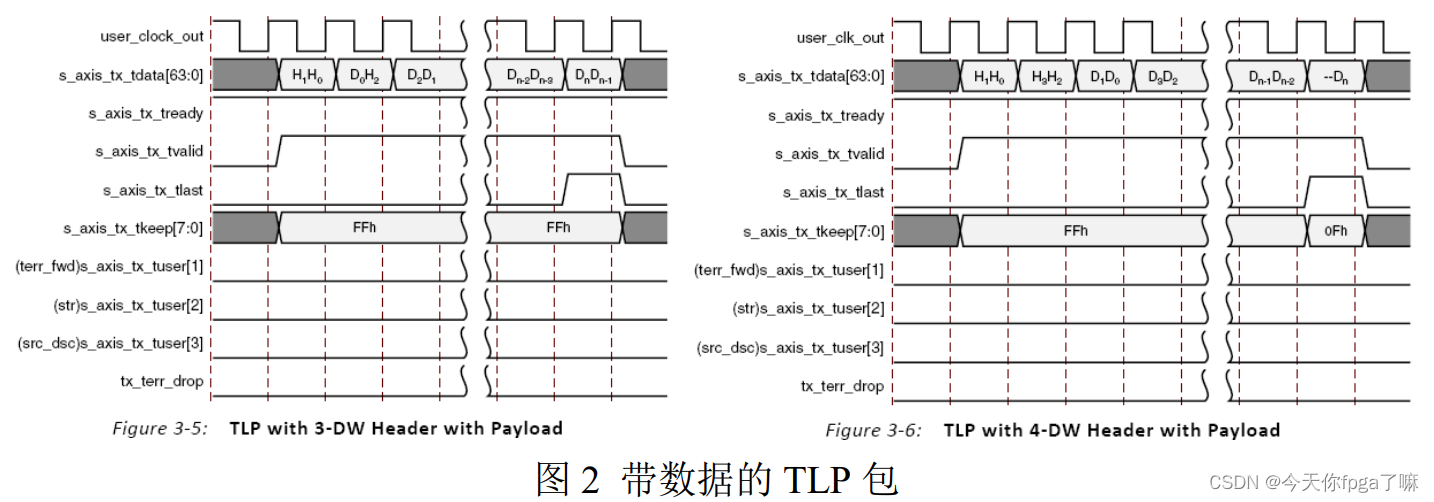

1.2 带数据的TLP包

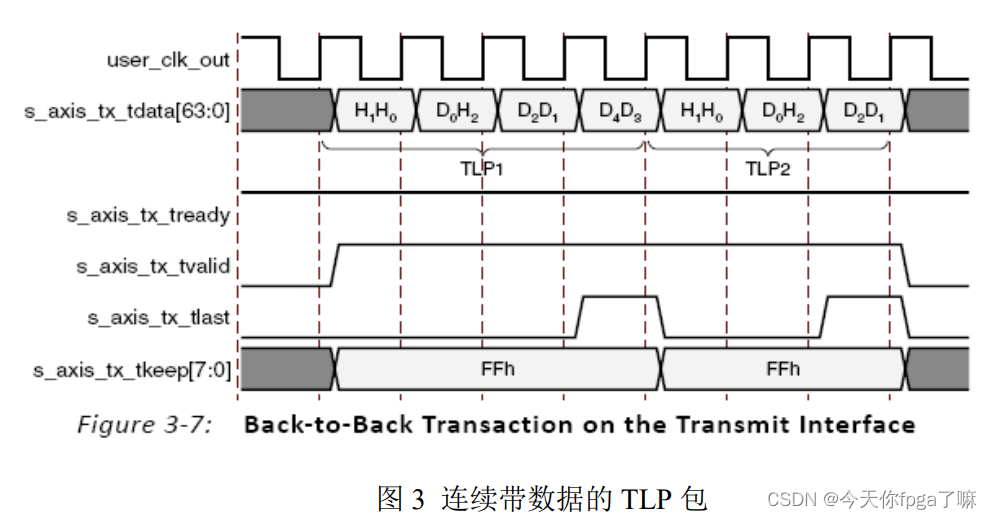

1.3 连续发送数据的TLP包

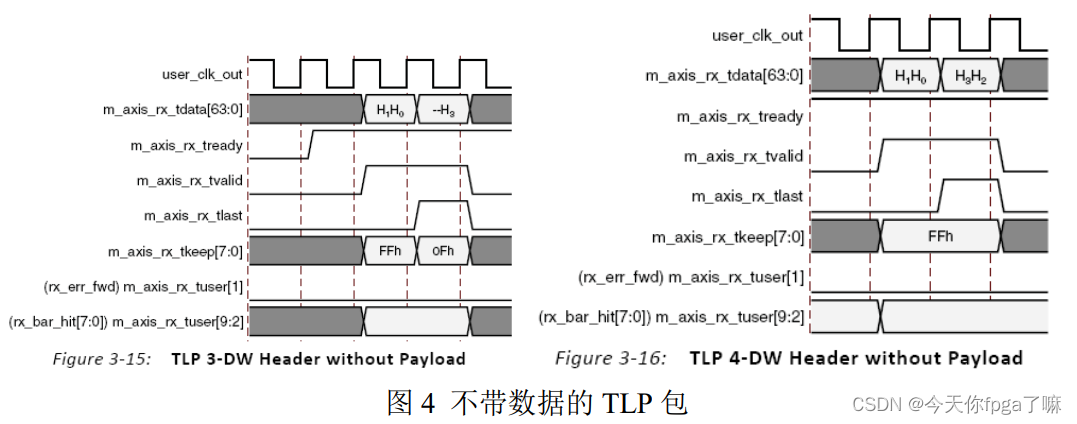

二、Pcie的接收时序

2.1 不带数据的TLP包

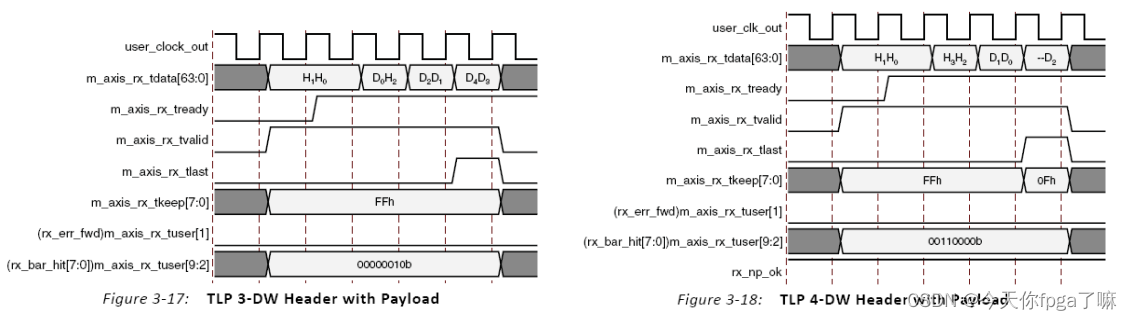

2.2 带数据的TLP包

2.3 连续接收数据的TLP包

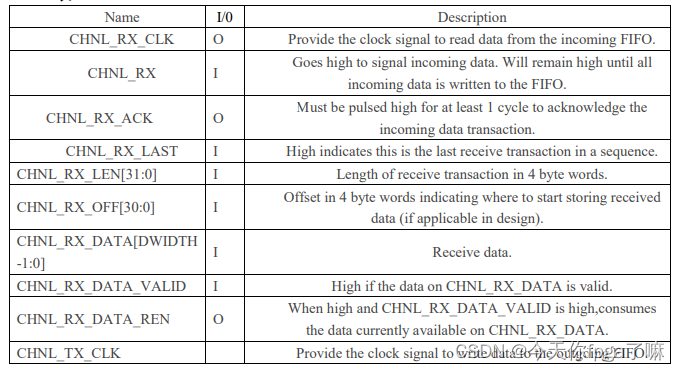

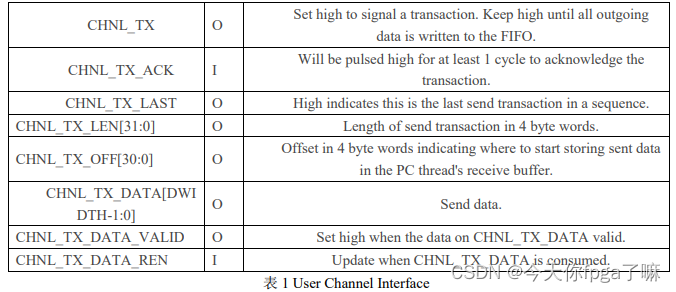

三、riffa框架和用户channel的接口

用户接口是用户与 RIFFA 交互的接口,使用起来非常简单,其端口定义如下表。

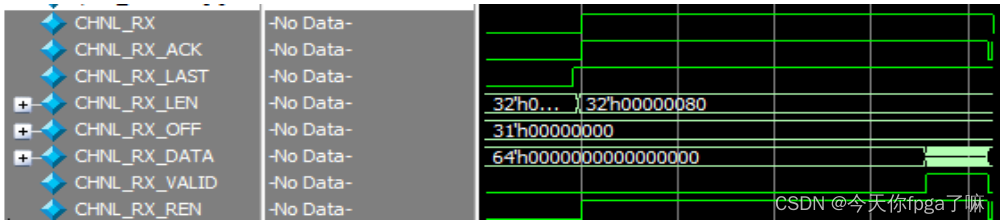

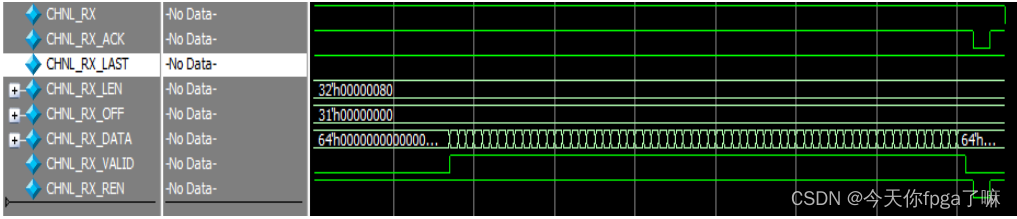

3.1 RX接口波形:

波形细节:

注意:RX接口中CHNL_RX信号不是在接收数据后立刻拉低的,而是会有1~2拍的延时。

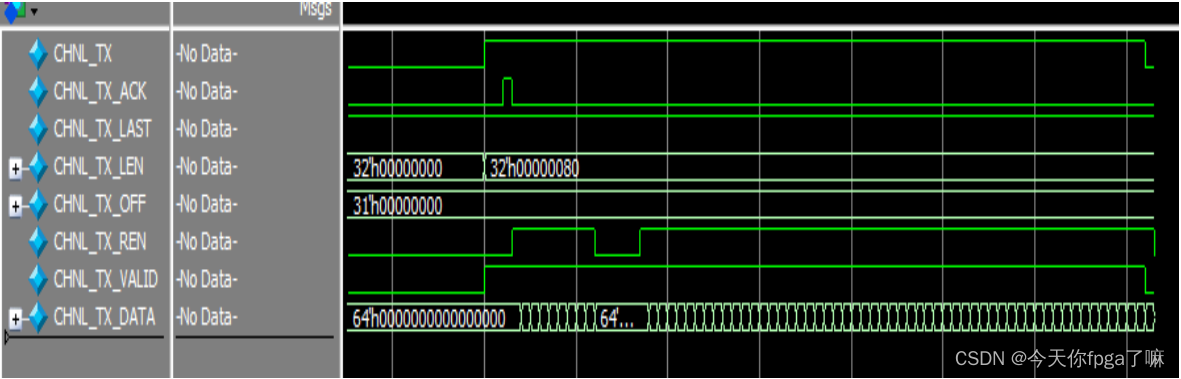

3.2 TX接口波形:

注意:这里CHNL_TX信号会在数据发送完毕后立刻拉低

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/IT小白/article/detail/621897

推荐阅读

相关标签