- 1【教程】Android系统手机 菜鸟扫盲汇总

- 2uniapp 的基础_uniapp在哪看下了什么依赖

- 3【JAVA】通过JAVA实现用户界面的登录_用户登录 java设计

- 4手把手教你搭建MongoDB分片式部署集群+实战_mongodb分片集群部署

- 5python小游戏————兔子_python小兔子代码

- 6Java基础知识解析:从入门到精通_java从入门到精通

- 7最全的 Charles 抓包工具详解

- 8BAT 批处理脚本教程_bat脚本编写教程菜鸟

- 9【自然语言处理】第3部分:识别文本中的个人身份信息_pipeline("ner", grouped_entities=true)的输出是什么

- 10ESP-12F模块使用指南

FPGA笔试题知识点汇总(21~40)_长川科技fpga笔试题

赞

踩

FPGA笔试题知识点汇总

- FPGA笔试题知识点汇总(21~40)

- 前言

- 一、题目及解析?

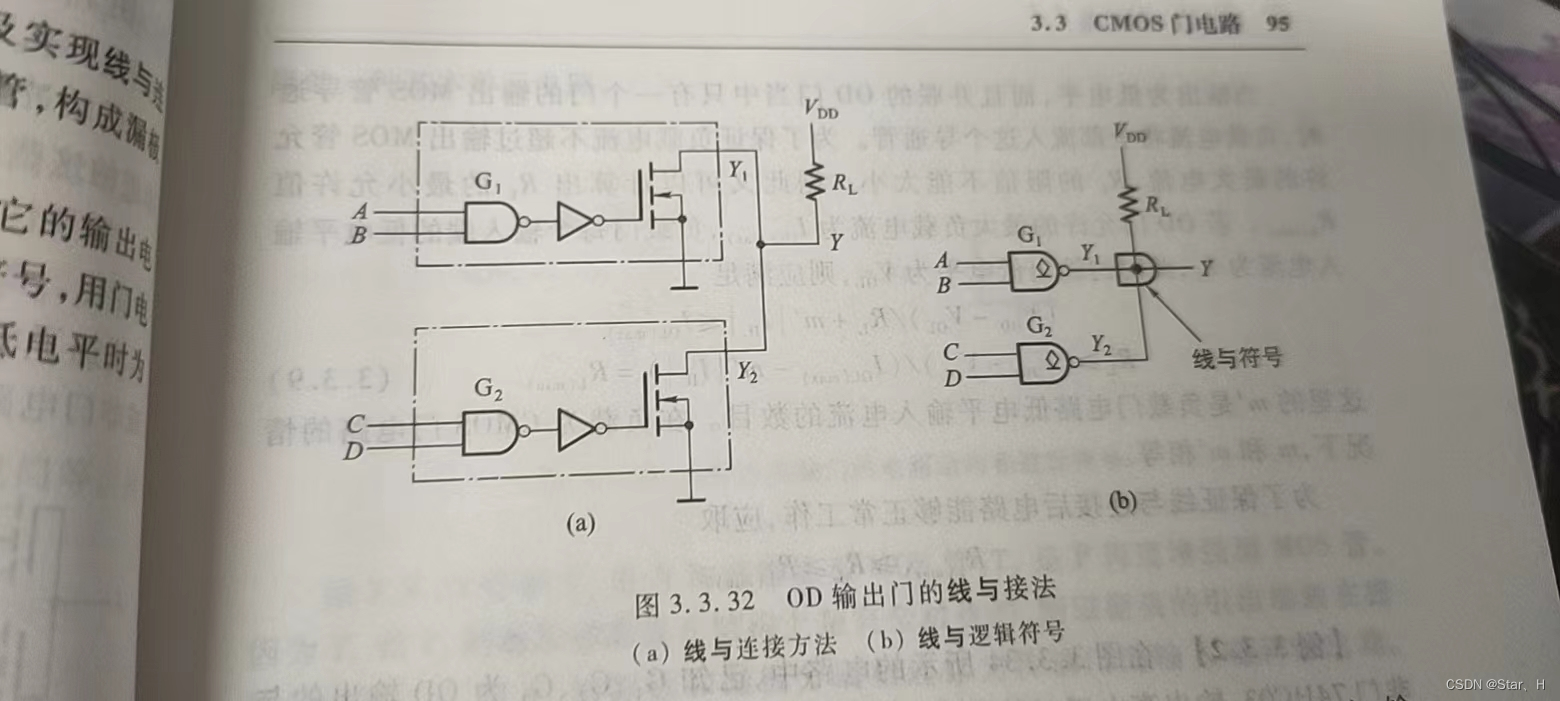

- 1、什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?(汉王笔试)

-

2、什么是竞争与冒险现象?怎样判断?如何消除?(汉王笔试)

- 3、你知道哪些常用逻辑电平?TTL与COMS电平可以直接互连吗?(汉王笔试)

- 4、如何解决亚稳态?(飞利浦-大唐笔试)

- 5、IC设计中同步复位与异步复位的区别?(南山之桥)

- 6、MOORE (摩尔)与 MEELEY(米勒)状态机的特征。(南山之桥)

- 7、多时域设计中,如何处理信号跨时域。(南山之桥)

- 8、给了reg的setup,hold时间,求中间组合逻辑的delay范围。(飞利浦-大唐笔试)

- 9、时钟周期为T,触发器D1的建立时间(这里应该是触发器触发时间Tco)最大为T1max,最小为T1min.组合逻辑电路最大延迟为T2max,最小为T2min.问,触发器D2的建立时间T3和保持时间应满足什么条件?(华为)

- 10、给出某个一般时序电路的图,有Tsetup,Tdelay,Tck->q,还有clock的delay,写出决定最大时钟的因素,同时给出表达式。(威盛VIA 2003.11.06 上海笔试试题)

- 11、说说静态、动态时序模拟的优缺点.(威盛VIA 2003.11.06 上海笔试试题)

- 12、一个四级的Mux,其中第二级信号为关键信号 如何改善timing?(威盛VIA 2003.11.06 上海笔试试题)

- 13、为什么一个标准的倒相器中P管的宽长比要比N管的宽长比大?

- 14、latch与register的区别,为什么现在多用register.行为级描述中latch如何产生的。

- 15、用mos管搭出一个二输入与非门。(扬智电子笔试)

- 16、画出CMOS的图,画出tow-to-one mux gate。(二选一的选择器)(威盛VIA 2003.11.06 上海笔试试题)

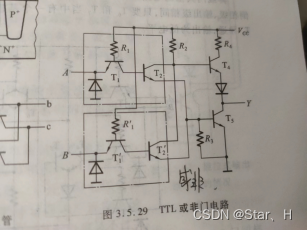

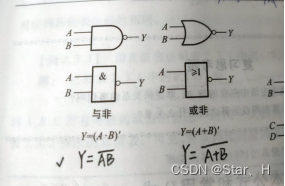

- 17、画出NOT,NAND,NOR的符号,真值表,还有transistor level(晶体管级)的电路。(Infineon笔试)

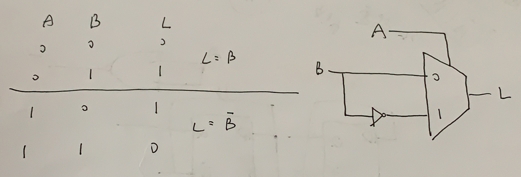

- 18、用一个二选一mux和一个inv(反相器)实现异或。(飞利浦-大唐笔试)

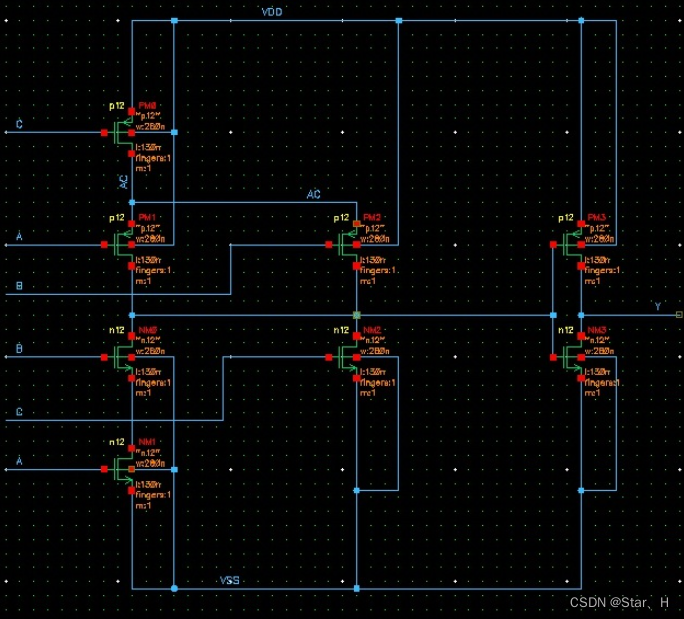

- 19、画出Y=A*B+C的cmos电路图。(科广试题)

- 20、please draw the transistor level schematic of a cmos 2 input AND gate and explain which input has faster response for output rising edge.(less delay time).(威盛笔试题circuit design-beijing-03.11.09)

前言

已经进入秋招的黄金期,面临找工作之际,继上一章,继续汇总一下网上的题目,每日打卡,供自己巩固复习知识点,祝愿自己能找到FPGA工作,如有错误,恳请各位大佬能够批评指正,本人咸鱼FPGA一枚。

一、题目及解析?

1、什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?(汉王笔试)

2、什么是竞争与冒险现象?怎样判断?如何消除?(汉王笔试)

如果逻辑函数在一定条件下可以化简成Y=A+A’或Y=AA’则可以判断存在竞争冒险现象(只是一个变量变化的情况)。

Delay < period - setup – hold

9、时钟周期为T,触发器D1的建立时间(这里应该是触发器触发时间Tco)最大为T1max,最小为T1min.组合逻辑电路最大延迟为T2max,最小为T2min.问,触发器D2的建立时间T3和保持时间应满足什么条件?(华为)

T3setup<=T – Tco(max)-Tdelay(max) , T3hold<=T1min+T2min

Thold>Tclkdelay+Tco+Tdelay;

静态时序分析是采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。它不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少,不仅可以对芯片设计 进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计,因此静态时序分析已经越来越多地被用到数字集成电路设计的验证中。

动态时序模拟就是通常的仿真,因为不可能产生完备的测试向量,覆盖门级网表中的每一条路径。因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题;

12、一个四级的Mux,其中第二级信号为关键信号 如何改善timing?(威盛VIA 2003.11.06 上海笔试试题)

关键:将第二级信号放到最后输出一级输出,同时注意修改片选信号,保证其优先级未被修改。

13、为什么一个标准的倒相器中P管的宽长比要比N管的宽长比大?

和载流子有关,P管是空穴导电,N管电子导电,电子的迁移率大于空穴,同样的电场下,N管的电流大于P管,因此要增大P管的宽长比,使之对称,这样才能使得两者上升时间下降时间相等、高低电平的噪声容限一样、充电放电的时间相等。

14、latch与register的区别,为什么现在多用register.行为级描述中latch如何产生的。

latch是电平触发,register是边沿触发,register在同一时钟边沿触发下动作,符合同步电路的设计思想,而latch则属于异步电路设计,往往会导致时序分析困难,不适当的应用latch则会大量浪费芯片资源。

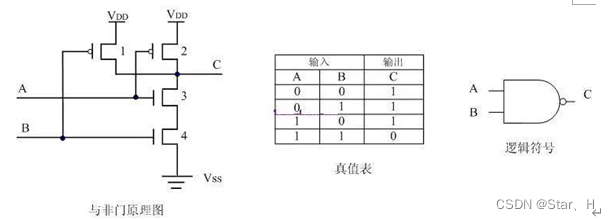

与非门工作原理:

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD一致,输出高电平。

②、A输入高电平,B输入低电时,1、3管导通,2、4管截止,C端电位与1管漏极一致,输出高电平。

③、A输入低电平,B输入高电平时,情况与②同样,也输出高电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地面一致,输出低电平。

Y=SA+S’B 利用与非门和反相器,进行变换后Y=((SA)’*(S’A)’)’,三个与非门,一个反相器。也可以用传输门来实现数据选择器或者是异或门。

Y=A*B+C=((AB)’C’) 一个反相器,两个两输入与非门

20、please draw the transistor level schematic of a cmos 2 input AND gate and explain which input has faster response for output rising edge.(less delay time).(威盛笔试题circuit design-beijing-03.11.09)-请画出cmos 2输入与门的晶体管级原理图,并解释哪种输入对输出上升沿的响应更快。(延迟时间更少)。

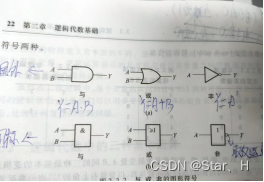

删除上述15与非门、或非门逻辑符号的输出端的小圆圈,成为与门、或门的逻辑符号。实现与、或功能的电路图必须在输出端添加一个反向器,即一对CMOS因此,与门实际上比与非门更复杂,延迟时间也更长,这在电路设计中应注意。

总结

这两天速度比较慢,对数字电路方面的知识点还不是很熟悉,耽搁了一点时间,其中可能还有错误,希望各位大佬批评指正,今天继续投简历,祝自己早日找到FPGA工作。