- 1ELMo动态词向量模型_elmo模型

- 2酱香酒除了茅台还有什么品牌好喝?适合普通消费者_除了茅台酒还有哪种酱香型的比较好

- 3驱动程序无法通过使用安全套接字层(SSL)加密与 SQL Server 建立安全连接问题解决_the server selected protocol version tls10 is not

- 435岁程序员半月4轮面试,全网最新_程序员面试都有几轮

- 5TLS/SSl相关的攻击漏洞及检测方法大杂烩!_cve-2014-8730

- 6Flink窗口理论到实践

- 7angular10 丝滑升级 至angular13或最新版_angular最新版本

- 82024年信息安全与网络安全有什么区别?,2024年最新作为网络安全程序员都应掌握

- 9CCF-GESP 2024 四级T1相似字符串

- 10Mysql 与ES(Elastic Search)对比_es数据库和mysql对比

VHDL数字频率计的设计

赞

踩

-

一.实验目的

-

二.实验内容

-

三.实验设计

-

四.实验步骤

-

五.实验结果

-

一.目的

-

1.学习Quartus Ⅱ/ISE Design Suite软件的基本使用方法。

2.熟悉GW48系列或其他EDA实验开发系统的基本使用方法。

3.学习VHDL基本逻辑电路的综合设计应用。

-

二.内容

-

设计并调试好8位十进制数字频率计,并用GW48系列或其他EDA实验开发系统进行硬件验证,具体包括系统结构设计、VHDL程序设计、程序仿真与分析、逻辑综合分析、硬件逻辑验证等内容。

-

三.设计

-

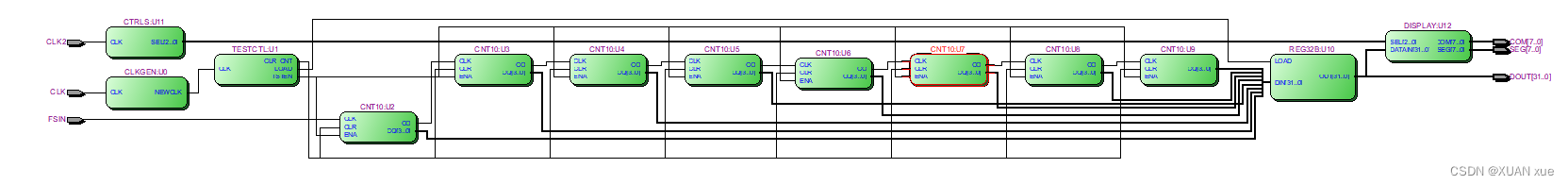

总体设计:设计一个8位十进制数字频率计,编写底层文件十进制计数器的源程序CNT10.VHD,编写分频器的源程序CLKGEN.VHD,动态扫描的源程序CTRLS.VHD,动态计数的源程序DISPLAY.VHD,寄存器源程序REG32B.VHD,以及计数使能信号源程序TESTCTL.VHD,由模块构成顶层电路数字频率计的源程序FREQ.VHD,其中底层和顶层电路均采用VHDL文本输入。

设计思路:数字频率计数器其功能是测出某个频率的大小。

频率 = 上升沿脉冲个数 / T , 当T等于1s时候,则频率=上升沿脉冲个数,故测出上升沿脉冲个数,此实验通过一个分配器的操作来达到输出的周期时间为1S。当TSTEN高电平时,允许计数;低电平时,停止计数,并保持其所计的数。在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进32位锁存器REG32B中,由外部的7段译码器译出并稳定显示。锁存信号之后,必须有一清零信号CLR_CNT对计数器进行清零,为下一秒钟的计数操作做准备。为了产生这个时序图,需首先建立一个由D触发器构成的二分频器,在每次时钟CLK上沿到来时其值翻转。其中,控制信号时钟CLK的频率取1Hz,而信号TSTEN的脉冲恰好为1s,可以用作阀门信号,此时,根据测频的时序要求,可得出信号LOAD和CLR_CNT的逻辑描述

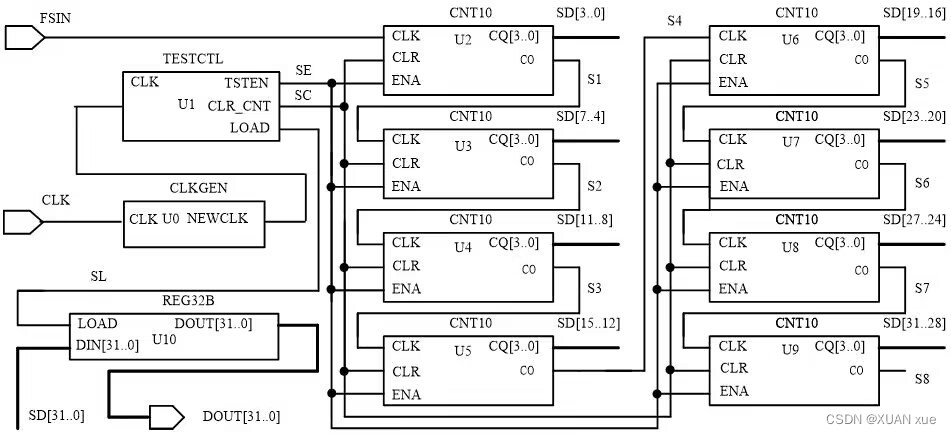

1、用8个CNT10来表示数字进位,利用分频器进行分频

图1基本方案演示

2、CLKGEN分频器分析,这里注意的是我选择的时钟是内部时钟50M,为了产生1s的时钟周期,我需要对其进行5M分频,但是为了能够波形仿真,所以还使用了一个分频常数小的分频器。利用动态扫描和动态计数的方式在数码管上显示,可以动态的显示数字变化,达到频率计的功能。

图2 原理图

四 .步骤

- 分析:利用quartus软件编写底层源程序:编写底层文件十进制计数器的源程序CNT10.VHD,编写分频器的源程序CLKGEN.VHD,动态扫描的源程序CTRLS.VHD,动态计数的源程序DISPLAY.VHD,寄存器源程序REG32B.VHD,以及计数使能信号源程序TESTCTL.VHD,由模块构成顶层电路数字频率计的源程序FREQ.VHD,其中底层和顶层电路均采用VHDL文本输入。

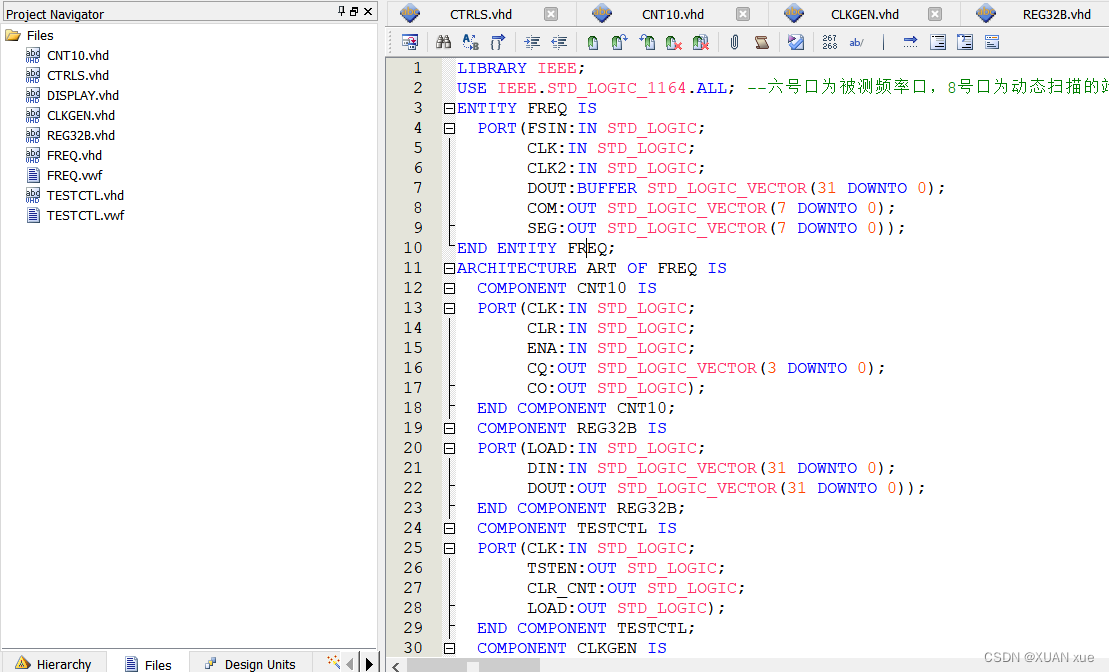

2、文件及工程的建立,用VHDL文件编辑好各个模块的源程序,工程编译观察工程是否实现

图5.1 编译程序结果图

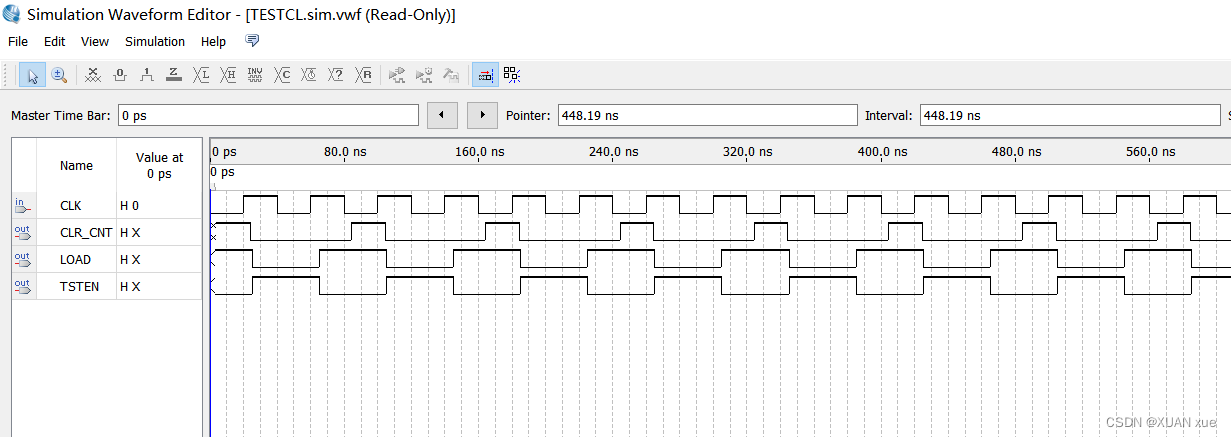

3、工程仿真,建立仿真文件,观察仿真结果

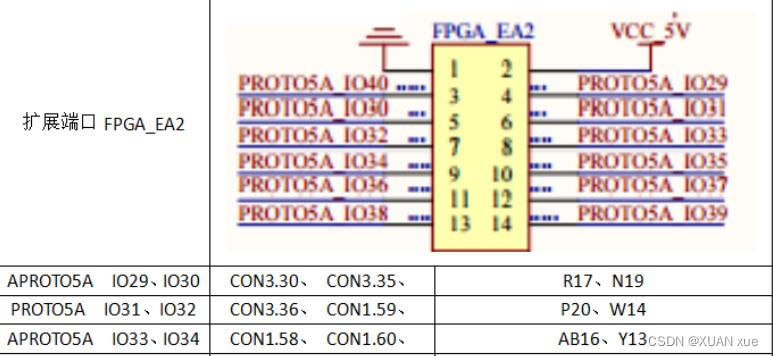

对TESTCTL仿真:

图5.2 TESTCTL波形仿真图

TESTCTL是计数使能信号,控制计数器,锁存器及清零何时工作。TSTEN和LOAD的波形是相反的,由于计数器在工作的时候锁存器并不工作,而计数器不工作的时候,LOAD为1代表锁存器开始工作,也可以看到CLR清零信号在TSTEN和CLK为0的时候来到一个上朓沿,代表进行清零,其中CLK有部分时间的延迟证明了信号的延迟特性。

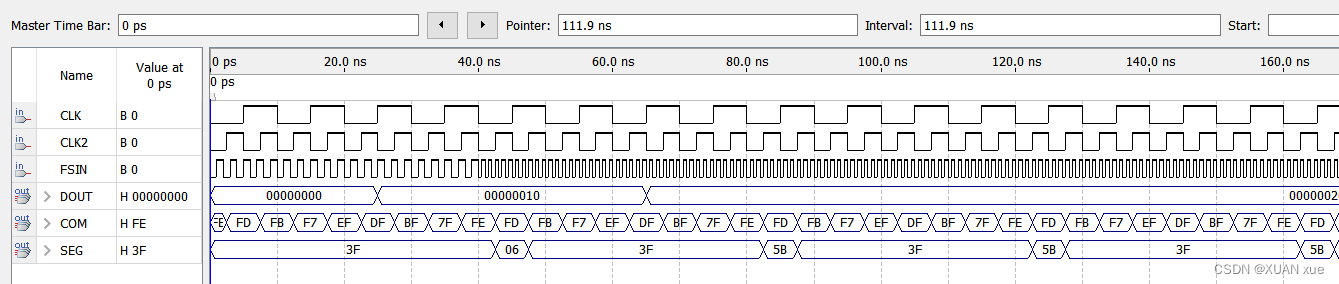

对FREQ进行波形仿真:

图5.3 FREQ波形仿真图

为了能够让波形能够显示出来,除了将DOUT设为可读之外,还需要将分频常数减小,为了达到测评的效果,将测试频率FSIN设置为2种不同的频率,通过GOUT得出被测频率的大小,其中COM为数码管的公共端,依次动态点亮,其中DOUT的数值对应SEG中数码管的八段管显示。

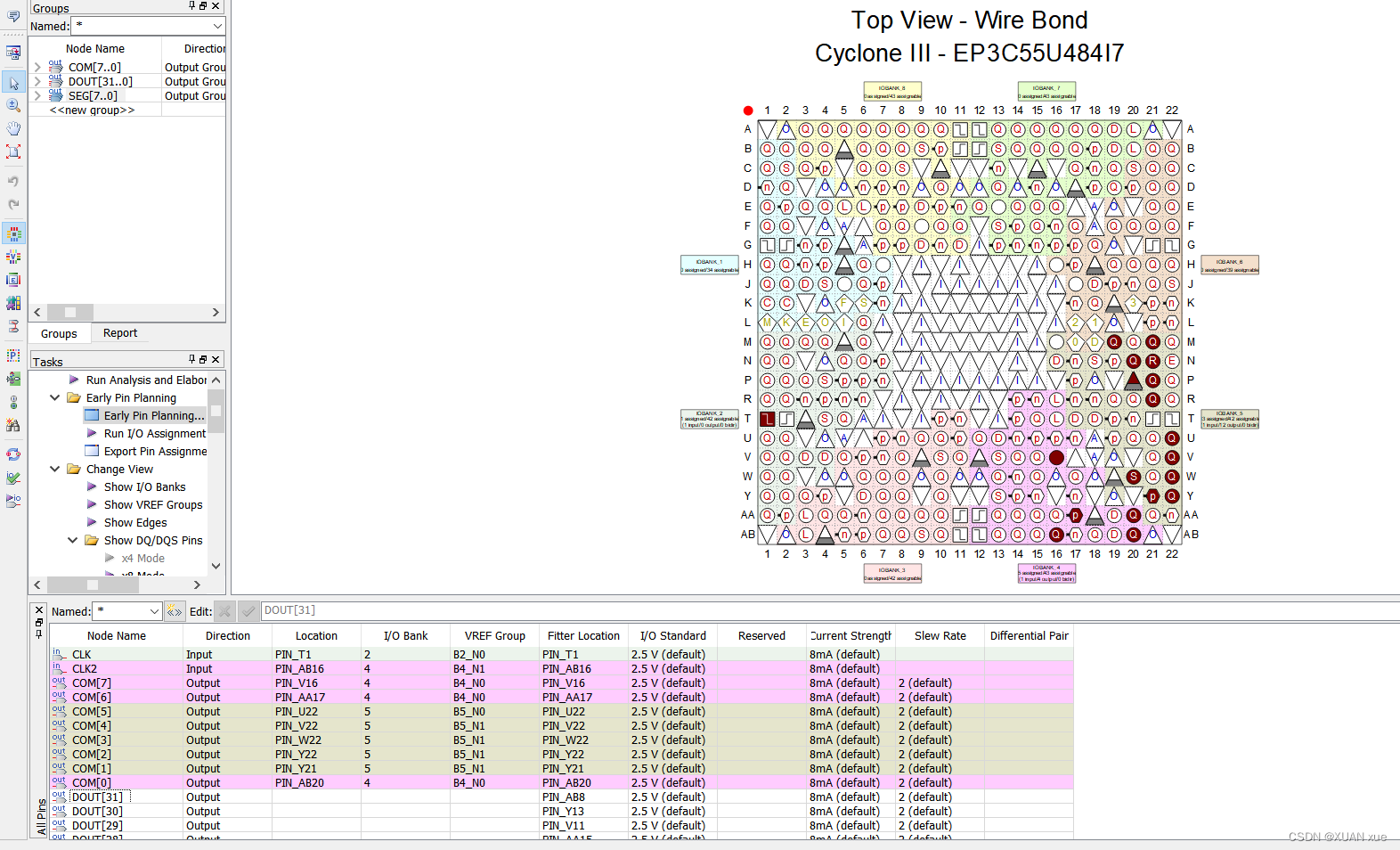

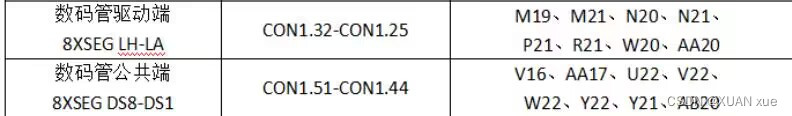

4、芯片管脚的锁定:

选择硬件相关的芯片EP3C55F484并对程序进行引脚锁定,对应给的常用的引脚锁定图进行锁定。选择好按键和时钟的引脚锁定,其数码管以常用的进行锁定。

图5.4 引脚锁定图

管脚锁定依照图5.5

图5.5管脚锁定依据图

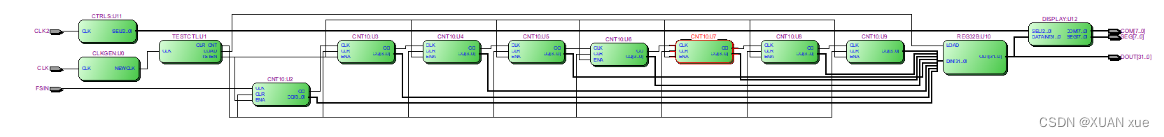

- 逻辑综合结果,查看程序RTL仿真图,熟悉整体电路状态。

图5.6 程序RTL视图

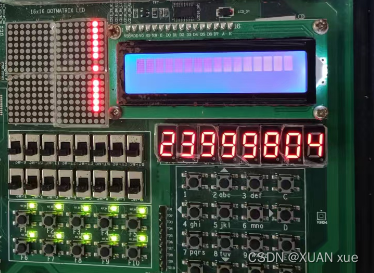

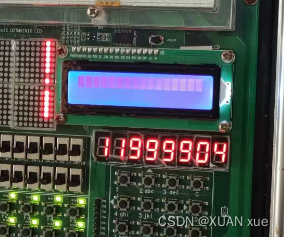

- 编程下载及验证,硬件验证功能是否实现

图5.7 硬件验证

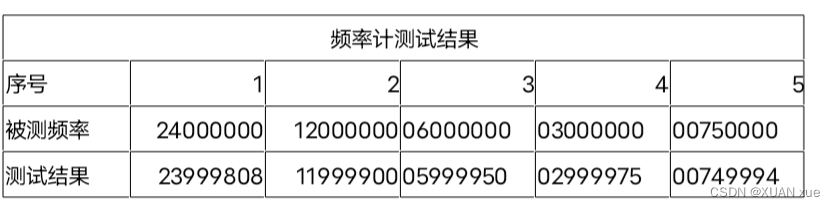

五.结果分析

可以看出测试结果与被测频率之间有一定的误差,其主要原因是硬件存在信号的传输,所以有一定的延迟特性。

图6. 7 频率计测频结果

2. 源代码分析

--CLKGEN的源程序

--CLKGEN

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CLKGEN IS

PORT(CLK: IN STD_LOGIC;

NEWCLK: OUT STD_LOGIC);

END ENTITY CLKGEN;

ARCHITECTURE ART OF CLKGEN IS

--SIGNAL CNT: INTEGER RANGE 0 TO 10#49999999#;

SIGNAL CNT: INTEGER RANGE 0 TO 10#1#;

BEGIN

PROCESS(CLK) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

--IF CNT=10#49999999# THEN CNT<=0;

IF CNT=10#1# THEN CNT<=0;

ELSE CNT<=CNT+1;

END IF;

END IF;

END PROCESS;

PROCESS(CNT) IS

BEGIN

--IF CNT=10#49999999# THEN NEWCLK<='1';

IF CNT=10#1# THEN NEWCLK<='1';

ELSE

NEWCLK<='0';

END IF;

END PROCESS;

END ARCHITECTURE ART;

-- REG32B的源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG32B IS

PORT(LOAD:IN STD_LOGIC; --为1时候代表锁存器工作

DIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0); --DIN是计数结果

DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END ENTITY REG32B;

ARCHITECTURE ART OF REG32B IS

BEGIN

PROCESS(LOAD,DIN)IS

BEGIN

IF(LOAD'EVENT AND LOAD='1')THEN

DOUT<=DIN;

END IF;

END PROCESS;

END ARCHITECTURE ART;

-- TESTCTL的源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TESTCTL IS

--其中clk信号由分配器产生

PORT(CLK: IN STD_LOGIC;

TSTEN: OUT STD_LOGIC; --输出时钟信号,用于控制计数器

CLR_CNT: OUT STD_LOGIC; --清零信号,用于清除计数器数据

LOAD: OUT STD_LOGIC); --用于发送给寄存器用于存储数据,其中电平波形于TSTEN相反

END ENTITY TESTCTL;

ARCHITECTURE ART OF TESTCTL IS

SIGNAL DIV2CLK : STD_LOGIC; --2分频时钟信号

BEGIN

PROCESS(CLK) IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

DIV2CLK<= NOT DIV2CLK; --进行一个翻转

END IF;

END PROCESS;

PROCESS(CLK,DIV2CLK) IS

BEGIN

IF CLK='0'AND DIV2CLK='0' THEN

CLR_CNT<='1';

ELSE CLR_CNT <='0';

END IF;

END PROCESS;

LOAD<=NOT DIV2CLK;

TSTEN <= DIV2CLK;

END ARCHITECTURE ART;

-- FREQ的源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; --六号口为被测频率口,8号口为动态扫描的端口

ENTITY FREQ IS

PORT(FSIN:IN STD_LOGIC;

CLK:IN STD_LOGIC;

CLK2:IN STD_LOGIC;

DOUT:BUFFER STD_LOGIC_VECTOR(31 DOWNTO 0);

COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY FREQ;

ARCHITECTURE ART OF FREQ IS

COMPONENT CNT10 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO:OUT STD_LOGIC);

END COMPONENT CNT10;

COMPONENT REG32B IS

PORT(LOAD:IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END COMPONENT REG32B;

COMPONENT TESTCTL IS

PORT(CLK:IN STD_LOGIC;

TSTEN:OUT STD_LOGIC;

CLR_CNT:OUT STD_LOGIC;

LOAD:OUT STD_LOGIC);

END COMPONENT TESTCTL;

COMPONENT CLKGEN IS

PORT(CLK: IN STD_LOGIC;

NEWCLK: OUT STD_LOGIC);

END COMPONENT CLKGEN;

COMPONENT CTRLS IS

PORT(CLK:IN STD_LOGIC;

SEL:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT CTRLS;

COMPONENT DISPLAY IS

PORT(SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

DATAIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0);

COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END COMPONENT DISPLAY;

SIGNAL SD:STD_LOGIC_VECTOR(31 DOWNTO 0);

--SIGNAL DOUT:STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL S0,S1,S2,S3,S4,S5,S6,S7,S8,SC,SE,SL:STD_LOGIC;

SIGNAL S9:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

U0:CLKGEN PORT MAP(CLK=>CLK,NEWCLK=>S0);

U1:TESTCTL PORT MAP(CLK=>S0,TSTEN=>SE,CLR_CNT=>SC,LOAD=>SL);

U2:CNT10 PORT MAP(FSIN,SC,SE,SD(3 DOWNTO 0),S1);

U3:CNT10 PORT MAP(S1,SC,SE,SD(7 DOWNTO 4),S2);

U4:CNT10 PORT MAP(S2,SC,SE,SD(11 DOWNTO 8),S3);

U5:CNT10 PORT MAP(S3,SC,SE,SD(15 DOWNTO 12),S4);

U6:CNT10 PORT MAP(S4,SC,SE,SD(19 DOWNTO 16),S5);

U7:CNT10 PORT MAP(S5,SC,SE,SD(23 DOWNTO 20),S6);

U8:CNT10 PORT MAP(S6,SC,SE,SD(27 DOWNTO 24),S7);

U9:CNT10 PORT MAP(S7,SC,SE,SD(31 DOWNTO 28),S8);

U10:REG32B PORT MAP(SL,SD(31 DOWNTO 0),DOUT);

U11:CTRLS PORT MAP(CLK2,S9);

U12:DISPLAY PORT MAP(S9,DOUT,COM,SEG);

END ARCHITECTURE ART;