热门标签

热门文章

- 1vue-resource拦截器interceptors使用_vueresource 拦截器

- 2大学生如何选择人生第一份工作

- 3自然语言处理3——玩转文本分类 - Python NLP高级应用_python 文本分类

- 4hadoop集群搭建篇(伪分布,完全分布)_hadoop从伪分布式模式怎么切换到完全分布式模式怎么操

- 5docker安装教程(详解)

- 6【MySQL】MySQL表设计的经验(建议收藏)_数据库表设计

- 7SQL语法之LIKE 操作符_sql like 占位符

- 8mysql error 1142_mariadb 1142

- 9【docker】Docker的基本指令和HTML/PYTHON/C++的简单创建示例

- 10机器学习/深度学习/NLP-7-准确率acc、精确率P、召回率R、F1、交叉熵_深度学习 acc函数

当前位置: article > 正文

Verilog设计流水灯(一)

作者:凡人多烦事01 | 2024-05-27 05:40:18

赞

踩

Verilog设计流水灯(一)

今天刚忙完大挑的策划,又到了更新博客的时候了,为了方便各位发烧友对Verilog_FPGA应用的学习,今天我想写一篇关于流水灯设计的文章,虽然很简单,但是这也是FPGA设计基础的重中之重,模块化设计!

初始流水灯,很傻,很天真。

这是我学习Verilog数字系统设计时悟出的真理,看着流水灯很神秘,其实往深处学习,很简单,很简单。

- 1

- 2

- 3

话不多说,先上一个模块,FPGA Verilog设计的重中之重就是模块化设计了,理清输入输出端口,将其封装,可以省去很多麻烦。

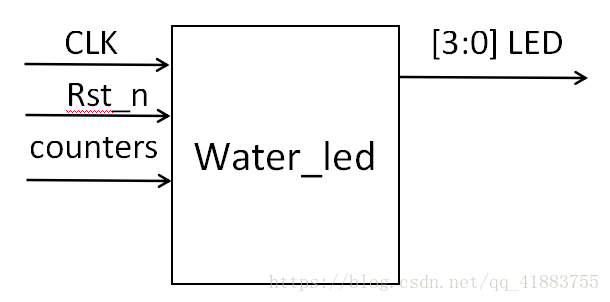

通过设计,我们自然可以得到它的输入输出端口:

这里,我们需要给它一个输入时钟,还有一个复位键,以及计数用到的计时器,然后FPGA给我们返回一个四位的LED,这里我们默认选择有四个LED(六个,八个,同理),我们摸清了它的输入与输出端口,然后我们可以开始我们的Verilog数字系统设计了。

先附上Verilog代码:顶层模块

module water_led(

input clk,rst_n;

input[31:0] counters; //这里的计数部分,我们可以选择其为寄存器,或者输入端口

output [3:0] led;

);

endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

流水灯逻辑部分:

module run_led(

input clk,rst_n;

output [3:0] led;

);

reg [31:0] counters;

reg [3:0] state;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

counter<=0;

led<=4'b0000;

state<=4'b0000;

end

else beign

case(state):

4'd0001:begin //第一个灯亮

led<=4'b0001;

if(counters<=24999_999) //产生延时 通过改变counters的值,可以改变灯亮灭的速度

counters<=counters+1;

else begin

state<=4'b0010;

counters<=0;

end

end

4'd0010:begin //第二个灯亮

led<=4'b0010;

if(counters<=24999_999)

counters<=counters+1;

else begin

state<=4'b0100;

counters<=0;

end

end

4'd0100:begin //第三个灯亮

led<=4'b0100;

if(counters<=24999_999)

counters<=counters+1;

else begin

state<=4'b1000;

counters<=0;

end

end

4'd1000:begin //第四个灯亮

led<=4'b10000;

if(counters<=24999_999)

counters<=counters+1;

else begin

state<=4'b0001;

counters<=0;

end

end

defualt: state<=4'd0001;

end

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

modelsim测试代码如下:

module run_led_tb();

reg clk,rst_n;

wire [3:0] led;

initial begin

clk=0;

forever #10 clk=~clk; //产生一个50MHZ时钟

end

initial begin

rst_n=0;

#20 rst_n=1; // 激励

end

run_led u1( //例化逻辑设计模块

.clk(clk),

.rst_n(rst_n),

.led(led));

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

通过改变我们要计数延时的counters,我们可以把流水灯设计成跑马灯,以及频率更慢的led指示灯。

其实,FPGA设计最难的部分还是在于输入输出端口的选择,逻辑设计很简单,FPGA处理数据很快。通过这篇文章的模块化设计思想,我们可以更清晰地设计出我们想要的数字电路。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/凡人多烦事01/article/detail/630116

推荐阅读

相关标签