热门标签

热门文章

- 1一文带你了解小米汽车投资布局

- 2[eNSP]建立IPSec隧道_ensp ipsec

- 3STM32 姿态传感器mpu6050的使用_mpu6050 stm32f103rc

- 4dhclient的基本命令_dhclient命令

- 5SQLynx发布3.0.0版本:带来更流畅便捷的SQL开发体验_sqlyns3.0

- 6【教程】网络安全(黑客)全阶段学习路线

- 7C语言字符串安全,关于安全性:C中的字符串处理实践

- 82023最新包你说语音口令红包小程序源码+运营版/修复BUG完全开源_密码红包源码

- 92022年全栈开发者需要熟悉了解的知识列表

- 10微信小程序使用npm包、全局数据共享和分包_npm 能不能让 所有包放到一起

当前位置: article > 正文

开发者分享|在Vitis中通过 PSU DDR 执行 MicroBlaze 应用_program device microblaze vitis

作者:小丑西瓜9 | 2024-04-12 02:58:09

赞

踩

program device microblaze vitis

MicroBlaze™ CPU 是可修改的拖入式预设 32 位/64 位 RISC 微处理器配置系列。

MicroBlaze 处理器能满足众多多样化的应用程序的不同需求,惠及工业、医疗、汽车、消费品和通信市场。MicroBlaze 使用哈佛 (Harvard) 架构,此架构的 PL 内通常包含双 LMB BRAM。但在本篇博文中,我们将探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用。

退出复位时,MicroBlaze 将从 MicroBlaze 配置中的 C_BASE_VECTORS 参数内指定的存储器地址提取其指令。在本例中,此 C_BASE_VECTORS 将设置为 PSU DDR 内的某个区域。

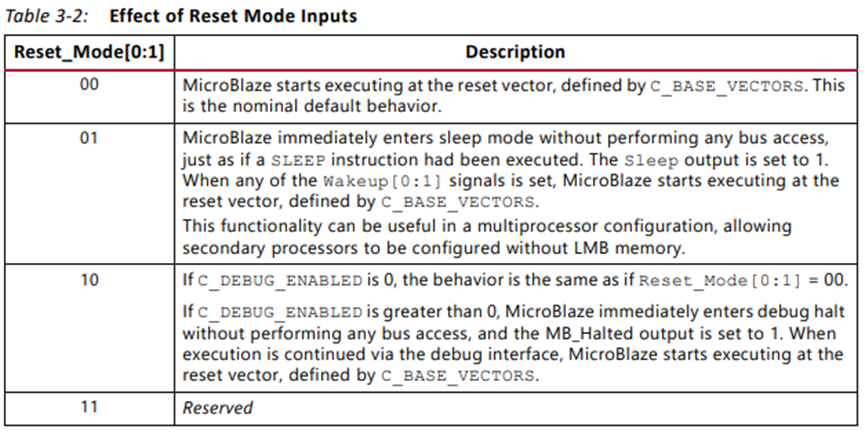

但根据采用的启动流程,这样可能导致潜在问题,即 PSU DDR 可能无法先于 PL 完成配置。这可能导致 MicroBlaze 挂起。为避免此现象,我们可以使用 MicroBlaze 上的“Reset Mode”(复位模式)信号。

在上表中,可以看到各种 reset_mode 配置。最适合我们的用例的配置为“01”,其中 MicroBlaze 将保持处于复位状态,直至我们准备就绪为止。我们将在 PSU 上通过 EMIO 来使用 GPIO 对 MicroBlaze 进行解复位。

创建硬件:

Vivado IP integrator 块设计如下所示:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小丑西瓜9/article/detail/408863

推荐阅读

相关标签