- 1Redis Scan 原理解析与注意点_redis sscan

- 2SQL优化最干活总结 (建议收藏)!!

- 3ubuntu16.04安装wordpress

- 4淘宝-天猫商品API:实时数据获取与安全隐私保护的指南

- 5转载:Python库_pyfiglet库的包

- 6OSError: [WinError 1455] 页面文件太小,无法完成操作。_oserror: [winerror 1455] 页面文件太小,无法完成操作

- 7MySQL系列之索引

- 8某阿里p7感叹:35岁的坎真实存在!出去面试,35岁的要求比34岁拔高一大截,刷了200多道leecode,依然没有offer!...

- 9k8s怎么监听资源的变更

- 10云计算、大数据、人工智能、物联网、虚拟现实技术、区块链技术(3)

FPGA(6)--7段显示译码器的加法计数器_fpga七段显示译码器波形图

赞

踩

一、实验目的

在上次加法计数器仿真实验的基础上,掌握端口的引脚配置、实验箱的接线及程序的下载、调试等。

二、实验内容

1.在上次实验的基础上,编译、仿真可以进行0-99加法计数功能的计数器,其中输入端口包括时钟、清零、使能,输出端口包括个位、十位的七段译码输出,以及输出进位信号。

2. 在Quartus II上进行输入、输出端口的引脚配置。并根据引脚配置完成接线,下载至FPGA芯片中,在实验箱上完成验证。

三、实验设计与结果

1.修改上一次实验实现的“进行0-99加法计数功能的计数器“的VHDL描述,其中输入端口包括时钟、清零、使能,输出端口包括个位、十位的七段译码输出,以及输出进位信号。并将其封装成一个元件。其代码及封装后的元件如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL ;

USE IEEE.STD_LOGIC_UNSIGNED.ALL ;

ENTITY cnt10 IS

PORT ( clk, rst, en, load : IN STD_LOGIC ;

data : IN STD_LOGIC_VECTOR ( 3 DOWNTO 0 ) ;

dout : OUT STD_LOGIC_VECTOR ( 3 DOWNTO 0 ) ;

cout : OUT STD_LOGIC ) ;

END ENTITY cnt10 ;

ARCHITECTURE bhv OF cnt10 IS

BEGIN

PROCESS (clk,rst,en,load)

VARIABLE q : STD_LOGIC_VECTOR ( 3 DOWNTO 0 );

BEGIN

IF rst = '0' THEN q := ( OTHERS => '0') ;

ELSIF clk 'EVENT AND clk = '1' THEN

IF en = '1' THEN

IF ( load = '0') THEN q := data ; ELSE

IF q < 9 THEN q := q+1;

ELSE q := ( OTHERS => '0') ;

END IF ;

END IF ;

END IF ;

END IF ;

IF q = "1001" THEN cout <= '1' ;

ELSE cout <= '0' ;

END IF ;

dout <= q;

END PROCESS ;

END ARCHITECTURE bhv ;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

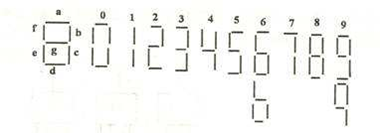

2.其中的“输出端口包括个位、十位的七段译码输出”,需要修改上一次实验的七段译码的VHDL描述,并将其封装成一个元件。代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL ;

use Ieee.std_logic_unsigned.all;

entity led7s is

port (a: in std_logic_vector(3 downto 0);

d: out std_logic_vector(6 downto 0)

);

end entity led7s;

architecture bhv of led7s is

begin

process (a)

begin

case (a) is

when "0000" => d<= "0111111" ;

when "0001" => d<= "0000110" ;

when "0010" => d<= "1011011" ;

when "0011" => d<= "1001111" ;

when "0100" => d<= "1100110" ;

when "0101" => d<= "1101101" ;

when "0110" => d<= "1111101" ;

when "0111" => d<= "0000111" ;

when "1000" => d<= "1111111" ;

when "1001" => d<= "1101111" ;

when others => null;

end case;

end process;

end architecture bhv;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

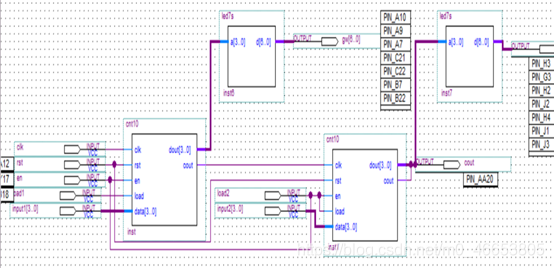

3.如下图将以上封装好的元件连接成可以实现功能的原理图,让其可以实现0-99加法计数功能,其中输入端口包括时钟、清零、使能,输出端口包括个位、十位的七段译码输出,以及输出进位信号。

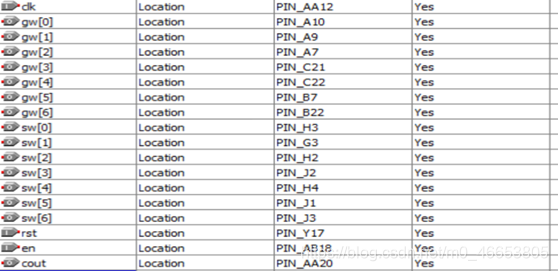

4.进行输入、输出端口的引脚配置。注意配置引脚位置的合理性。如下图为相关的配置信息。

clk外接一个频率合适的时钟信号,使能端信号则由外接的上下推动的开关决定,而进位信号的输出则用一个外接的发光二极管指示灯表示。两个七段数码管则根据相关引脚信息给出。

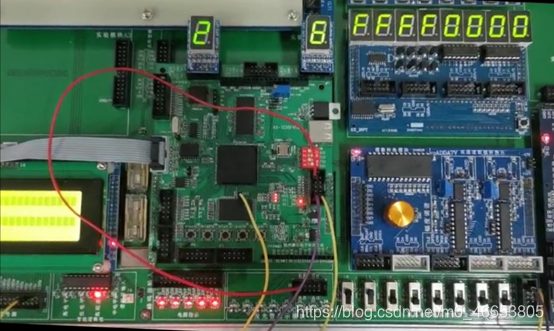

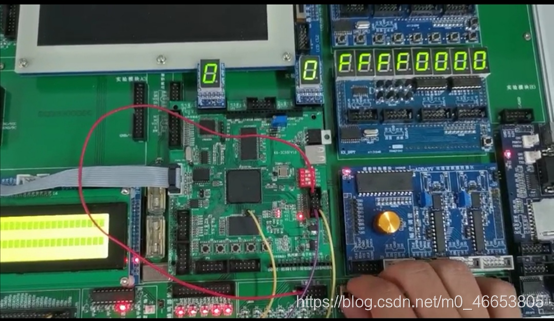

5.根据引脚配置完成接线,下载至FPGA芯片中,在实验箱上完成验证。如下图为相关的实验验证。

四、实验思考与小结

七段数码管有直流驱动和动态显示驱动两种。直流驱动:是指每个数码管的每一个段码都由一个单片机的I/O端口进行驱动,或者使用如BCD码二-十进制译码器译码进行驱动。优点是编程简单,显示亮度高,缺点是占用I/O端口多。动态显示驱动:是将所有数码管通过分时轮流控制各个数码管的的COM端,就使各个数码管轮流受控显示。将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O线控制,当单片机输出字形码时,所有数码管都接收到相同的字形码,但究竟是那个数码管会显示出字形,取决于单片机对位选通COM端电路的控制,所以我们只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。