- 1adb install 时 日志输出Performing Streamed Instal 一直卡着不动,处理方法_performing streamed install

- 2【STM32+HAL+Proteus】系列学习教程---串口USART(DMA 方式)定长,不定长收发。

- 3Java常用实现八种排序算法与代码实现_java排序算法代码

- 4【Vue】Vue 入门学习文档_vue文档

- 5达梦数据库安装超详细教程(小白篇)

- 6Linux Centos7 修改yum源镜像_centos7修改yum镜像

- 7三十分钟理解博弈论“纳什均衡” -- Nash Equilibrium

- 8stm32知识记录

- 9【重磅开源】一款可以生成SpringBoot+Vue代码的轻量级项目

- 10精选Axure原型设计模板,RP原型组件库(PC端移动端元件库及Axure函数及运算符说明)_大饼pc端产品设计标准设化模板原型

学习笔记——VLSI测试方法学和可测性设计_vlsi测试方法学与可测性设计

赞

踩

VLSI测试方法学和可测性设计-雷绍充 著

本周开始复习集成电路测试与可测性设计,参考教材为VLSI测试方法学和可测性设计。

Chapter0 概述

第一部分:构造准确的失效模型、对原型设计的模型生成高效率的测试代码、进行测试结果分析

第二部分:电路模拟方法、组合电路和时序电路的确定性生成方法

第三部分:可测性分析。电路是否容易测试、电路功能正确、是否容易在输入端是假信号、输出端观察电路响应

第四部分:可测性设计。BIST结构(内建自测试)

1.研究意义

测试时VLSI设计中费用最高、难度最大的一个环节 ;随着开发周期变短,测试对产品的上市时间、开发周期影响越来越大;SoC的核测试复用问题难以自动检测每一个核的可测性。

2.章节安排

Chapter1 电路测试和可测性基础知识

Chapter2 模拟方法在电路测试和分析中的作用

Chapter3 组合电路测试生成

Chapter4 时序电路测试生成

Chapter5 可测性设计的专用设计技术

Chapter6 扫描路径法、电平敏化法等减少复杂性的方法

Chapter7 内建自测试生成基础,随机/伪随机电路理论

Chapter8 边界扫描法

Chapter9 内建自测试

Chapter10 电流测试法

Chapter11 存储器的故障模型和测试方法

3.常用术语

被测电路:Circuit Under Test,CUT

测试生成:对被测电路生成测试数据的方法和过程

测试图形:产生的测试数据

测试响应:测试图形施加后被测电路的输出

ATE:自动测试装置,Automatic Test Equipment

BIST:内建自测试,Built-In Self Test

电路测试流程:产品测试、故障模型

4.辨析

4.辨析

错误:被测电路不嗯能够正常工作

故障:电路的设计和制造无错误切工作条件正常:无故障 反之:有故障

缺陷:制造中加工条件的不正常和工艺设计有误从而造成电路不正常的物理结构

5.测试效率

高质量的测试应该是用尽可能少的测试图形检测出尽可能多的故障->故障覆盖率(fault converage)

故障覆盖率:对于给定的故障模型,测试图形能够检测到该类型故障的数目与电路中可能存在的所有该类型故障数目之比,用百分比表示。

100%->完全测试集

6.测试类型

测试生成方式:穷举测试、伪穷举测试、伪随机测试、确定性测试

测试施加方式:片外测试、片上测试

图形施加时间:离线测试、在线测试

穷举测试:测试图形包含了原始所有输入可能的排列组合,也全部施加到被测电路。优点:测试矢量容易生成,100%故障覆盖率 缺点:只对小规模的纯组合电路

伪穷举测试:测试集是穷举的,但测试矢量施加时序上具有随机性。

伪随机测试:测试图形的每位字都是随机的,这样产生测试矢量的成本最少,一般故障覆盖率可达85%。许多用商用ATPG工具随机产生测试图形。

确定性测试:基于故障类型生成测试图形。优点:测试图形非常短,难点是测试生成方法非常复杂,测试生成时间非常长。

测试施加:有ATE和内建自测试施加方式,模拟时通过在EDA环境下施加测试图形。

在线测试:需要专门代码,检验装置和复用技术,优点是可以测试顺便故障;

离线测试:测试施加电路在非工作情况下运行。

自动测试设备(ATE):由夹具、硬件和软件组成。分为数字、存储器、模拟测试仪

夹具:固定被测IC

硬件:大容量计算机(存储测试图形和理想响应)

软件:算法生成测试数据

Chapter3 组合电路测试

1.所有算法包含4个操作:激活、敏化、确认和蕴含。

2.异或法进行测试生成:过程直观但计算过程冗长,对于重聚的扇出电路无法进行测试生成

何时故障不可检测?存在故障冗余的电路,该电路存在且只存在一条线,当这条线被去掉并用适当的逻辑常数(0/1)代替时,它所实现的功能不变。

在组合电路中,重聚的扇出分支或路径上的均存在不可测故障

3.路径敏化法:从故障源处到原始输出之间寻找一条路径,沿着这条路径,故障效应可从源处传播到原始输出,即故障效应可观。

敏化路径是否成功要看激活故障后再原始输出观察到的值域电路无故障时原始输出是否相同

4.激活:激活某条线上的故障就是该线的逻辑值为鼓掌逻辑值的反,等效于把故障信号置于该线上。

敏化(传播):选择一条路径,沿此路径可把故障信息从源处传播到原始输出。

确认:根据敏化路径上元器件的输入输出逻辑关系,对敏化路径上的其他线赋值,以确定这些线的逻辑值。

蕴含:通过已确认的线逻辑值,寻找非敏化路径上门的输出或输入值的过程(向后追踪)

5.D算法-非冗余组合逻辑电路寻找测试图形

奇异立方:逻辑函数除最小项以外的其他表示项,称奇异立方。任意逻辑函数都可以用若干奇异立方表示。即函数真值表的压缩表示法。

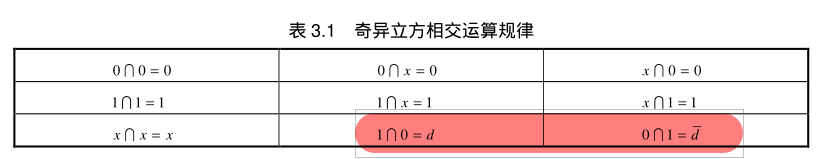

d立方:5值系统 0,1,x,d,d/

5.1原始d立方应该满足:

5.1原始d立方应该满足:

(1)确定吧故障效应传播到输出的输入信号值,输入信号应该使得故障在源处激活+传播到输出

(2)输出应出现符号d或d/

d表示电路无故障输出为1,有故障输出为0

d/表示电路无故障输出为0,有故障输出为1

5.2传播d立方:将输入端的故障效应传播到元器件输出端的最小输入条件。表明建立敏化路径的条件,也是对被测电路的结构描述。

5.3d驱赶(d drive):逐级将故障信号从故障源处敏化至原始输出的过程

5.4 D算法基本步骤:

建立原始D立方(PDCF,Primitive D-Cube for Failure)激活故障;

选择敏化路径

沿敏化路径传播PDCF(驱赶)

如果原始输入出现d或d/,驱赶成功,否则选择其他敏化路径。

一致性检查,若成功则确定测试图形,否则则无测试生成。

6.PODEM算法

D算法不适用于又重聚的扇出电路(奇偶检测电路、表决电路、误码校正、检测电路)

PODEM:Path Oriented Decision Making对激活的故障向后追踪到原始输入,搜索所有可能的原始输入赋值,只要找到一个符合要求的即可视作测试图形,算法结束。

先初始化输入值,随后通过“分支-判决树”穷举完成输入赋值的改变

无测试的两种情形:故障没有激活,故障的传播路径没有得到敏化

Chapter4 时序电路测试

1.时序电路:存储元件(触发器)和组合逻辑电路(组和逻辑门)组成,电路输出不仅与当前输入有关,还与电路历史状态有关。因此测试生成更加复杂。

特点:

(1)初始化时序电路所需矢量可能不止一个,而且矢量施加顺序至关重要。

(2)需要考虑设置时间和保持时间。器件延迟可能导致冒险和竞争。

2.时序电路测试方法:

(1)功能测试法,验证时序电路是否按状态表工作.无需电路集体结构,但不适用于VLAI

(2)将时序电路转化为一系列组合电路,使用基于故障的确定性方法进行测试生成。细分为:时间向前法,时间向后法,组合方法。

(3)可测性设计方法

3.9值系统(1,0,x,d,d/)+(G0,G1,F0,F1)(Good zero,good one,faulty 0,faulty 1)

时序电路的间插序列:输入序列+观察序列。分别进行状态初始化和状态跳变。

输入序列:同步序列、引导序列、鉴别序列和变迁序列。

同步序列:将时序电路置为已知状态的输入序列

引导序列:时序电路引导到已知状态的输入序列

饯别序列:生成输出序列的输入序列

变迁序列:引起时序电路状态变化的输入序列

4.时序电路功能测试步骤

5.时序电路的确定性测试生成

同步时序电路:Huffman模型 组合逻辑电路(CC)+存储单元(S)

测试序列作用:使被测电路进入适当的状态和在此状态检测给定故障。

完成:状态初始化+故障效应传播

因此实际测试中对一给定故障施加的测试序列其顺序不应改变。

5.1向后驱赶算法(EBT)

Extented Back-Trace

时间逆向处理方法:第一个生成的测试矢量最后一个施加,最后生成的测试矢量第一个施加。相邻的矢量成为:当前矢量(CV,把故障效应传播到原始输出)和第二个的先前矢量(PV)

5.2FASTEST算法

5.2FASTEST算法

FASTEST基于PODEM算法、9值逻辑、时间向前处理测试生成与状态的初始化

优点:PODEM算法比路径敏化算法效率更高,测试长度保持最小

特点:试探 3中不同方法的试探,用于向后追踪

(1)从原始输入进行简单的长度分析

(2)静态可控性计算-类似于组合电路的可控性度量SCOAP

(3)动态可控性计算-每当对一节点赋一次值,就重新计算可控性值以反映变化

5.3CONTEST算法

基于模拟的测试生成方法,对选定的初始矢量在模拟结果的基础上计算成本函数。如果成本函数减少,试探矢量就是下一个矢量,否则修改原始矢量,直到成本函数降到阈值以下。

三种不同的成本函数

(1)一组故障的测试生成

每一个故障的成本函数是故障效应及原始输出之间敏化路径上门的个数。

(2)单故障测试生成

故障激活成本函数+故障效应成本函数

优点:试探方式 缺点:有时会生成较多的测试矢量

Chapter5 专用可测性设计

1.可测性设计

在IC设计(前端)阶段就进行结构化设计,解决复杂的测试问题,设计出容易测试的电路,这就是可测性的主要内容。

两方面要求:一是电路内的故障是否可以用有限的测试图形来检测或定位;二是故障效应观察的难易程度(检测故障所需的测试图像的长度、生成时间、施加时间的长短)

评价指标:可测性度量值

系统化技术可测性设计:路径扫描、内建自测试、边界扫描技术成为VLSI可测性设计和应用的主流

扫描设计:时序电路可测性设计,将电路内部信号“一出来”或输入信号“移入”电路。如电平敏化扫描设计(LSSD)

2.可测性分析-度量标准

可控性:电路中节点置为预定逻辑值的难易程度

可观性:电路中任意节点的值在原始输出可观察的难易程度

2.1可控性值

CC0/CC1:将节点N的值置为组合逻辑值0/1需要对相关节点赋组合逻辑值的最少赋值次数

SC0/SC1:将节点N的值置为时序值0/1需要对相关节点赋组合逻辑值的最少赋值次数

相关计算公式参见P101

2.2可观性值

CO:把节点N的信息传播到原始输出,所需最少的组合逻辑值赋值次数叫做节点N的组合可观性值

SO:把节点N的信息传播到原始输出,所需最少的时序逻辑值赋值次数叫做节点N的组合可观性值

相关计算参见P103

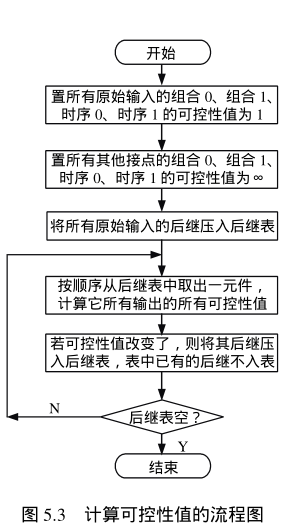

3.SCOAP算法

设置一个先进先出的排队表(后继表),每次计算按照顺序从后继表中取出原件进行可控性数值的计算。直至后继表空;而可观性计算通过先进先出的排队表(前趋表)进行计算。

通过可测性值度量电路可测性的难易程度,反映了故障是否可以用有限的测试图形来检测和定位,以及反映了测试图形的长度和生成时间的长短;

通过可测性值度量电路可测性的难易程度,反映了故障是否可以用有限的测试图形来检测和定位,以及反映了测试图形的长度和生成时间的长短;

可控性反映了电路中节点设置为预定逻辑值的成本,节点深度增加成本也增加。

二者同等重要,一个可观的节点并非都是可控的,而除非节点是可控的否则单纯提高可观性也是没有意义的。

4.可测性改善方法

结构化可测性设计技术出来之前,对专用可测性设计技术的优化:时序电路测试前先初始化,插入观察点,控制点,改善电路可测性。

4.1测试点插入

控制点:CP用于改善电路可测性的原始输入,比如更容易设为预定的逻辑值。

观察点:OP用于改善电路可观性的原始输出

注意:插入控制点会影响节点的可控性和可观性,往往时序电路需要较多的测试点插入;内建自测试中插入测试点十分重要,因为电路存在抗随机测试故障,是难以用随机图形测试的。

4.2电路分块

电路的可测性是深度的函数,电路越小越容易测试。

硬件分块:通过MUX进行电路之间的隔离

敏化分块:对测试数据敏化,将N输入的电路划分为M块,每块具有K个原始输入,从而减轻测试复杂性。

验证测试:适用于每一个原始输出只是原始输入子集的函数的电路。

容易测试的电路

一般是结构上有规律的电路,如RAM,FPGA,阵列复选电路等。单元结构可能是组合电路也可能是时序电路。

迭代的逻辑阵列(ILAS)Iterative Logic Arrays-C可测性,常数测试图形,格式和代码固定

5.组合电路的可测性设计

对数字电路插入门的逻辑可以改善电路的可控性和可观性质,从而降低电路测试和诊断的复杂程度。

Reed-Muller:任何一个组合逻辑均可用异或门实现,虽然电路结构比原先复杂但测试十分简单,仅需确定的测试图形即可检测所有的单故障。参见P121.硬件用双输入异或门的串联作为基础结构

Saluia&Reddy:任意一个n输入的门可用(n+1)个测试图形完全测试。设计过程中要求每一个量输入门对其输入信号的响应需要对后续的门完全测试。

6.时序电路可测性设计

需要关注以下问题:位初始化设计、元件时延效应、不可测的故障冗余、不合法状态、振荡电路

一般先用逻辑模拟器寻找输入序列,直到时序电路的未知状态最小化。(未知状态的触发器的个数)

6.1最小化时间延迟

由于时间延迟导致的竞争会影响测试生成,因为有可能测试生成过程中忽略了两条或以上敏化路径具有不同的延迟时间,测试一般基于零延迟,使得初始化与故障船舶序列依据不正确的状态生成。

解决方案:(1)引入额外的时钟信号;(2)相邻图形每次只改变1位

而异步电路中延迟导致的冒险容易对记忆原件产生假信号。

6.2逻辑冗余问题

逻辑冗余一般不会影响电路逻辑功能,但却会导致测试故障覆盖率低甚至影响其他故障的测试生成。

前文提到,故障冗余一般存在于重聚的扇出节点上,可用计数方案检测逻辑冗余但由于逻辑冗余导致的不可测问题,目前还没有完全可行的解决方案。

最好的办法就是设计时在电路中避免冗余,即使不可避免引入冗余,也应在文件中表明,计算故障覆盖率时排除这些故障。

6.3避免设计中的非法状态

即无用的状态,触发器相关

6.4增加逻辑以控制震荡

振荡:异步反馈环路的电路中,加入一些输入序列可能导致振荡:即某些信号不断改变逻辑值,使得电路不进入已知的稳定状态,测试生成不可完成。->增加额外的逻辑

Chapter6 扫描路径法

背景:对于时序电路的测试生成:测试生成复杂且施加时间长,难以对电路内部节点设置逻辑值,电路内部状态难以观察。

1.扫描路径:增加敏化测试图形的测试方法。使得电路初始化容易,电路可测性得到改善,减少了时序电路的测试生成过程。同步时序电路可工作在两种方式:正常方式和测试方式

正常方式:电路按原始设计连接

测试方式:所有的触发器从电路断开,形成移位寄存器结构。所有移位触发器的输出变成电路的伪原始输入

2.扫描路径设计-全串行扫描设计

时序电路中所有存储单元假定为触发器。每一个触发器前面接入二输入MUX,MUX的输入之一为前触发器的输出,另一个输入为原始设计中所接的信号。控制线决定触发器处于测试状态还是工作状态。

串行扫描设计:电路硬件增加所,扫描路径长,测试时间和路径延迟增加多

串行扫描设计:电路硬件增加所,扫描路径长,测试时间和路径延迟增加多

3.部分扫描设计

只选择部分触发器置于扫描路径上,其他触发器还是用时序电路的测试生成和施加方法。

关键:扫描路径上触发器的选择问题,应该使DFT结构成本最小。

即电路面积尽可能增加的少,触发器放置产生的互连尽可能少,延迟减小。

根据扫描对象的不同,还有:触发器不在正常数据路径的隔离的串行扫描设计、扫描的是可寻址的存储器单元的非串行扫描设计

4.扫描路径的测试方法

扫描路径将时序电路转化为组合电路,分别对组合电路部分和不再扫描路径上的触发器进行测试生成,并且触发器的测试方法和测试图形是固定的。

组合电路部分:确保没有异步信号(包括触发器的置位、复位信号),确保测试生成时信号传输结束点时触发器的一个输入端;验证结束是触发器的一个输出端

测试施加:先测试触发器再测试组合电路部分,Example参见P137

5.扫描路径的结构

关注:扫描路径上的存储单元、设计存储单元

使得触发器能够在正常方式下独立工作,能够在测试方式下成为移位寄存器。

存储单元:爽口触发器、电平敏化锁存器、随机编址的存储单元。

电平敏化扫描设计:LSSD Level-Sensitive Scan Design

基于电平敏化锁存器,靠电平所存而不是边沿触发;可读可写。使用双锁存设计

随机编址的存储单元:

随机编址的存储单元:

允许独立的对每个存储单元的状态进行设置、重置和检查。结构包括译码器、地址锁存器

6.小结

扫描路径法-牺牲电路面积、时间换测试生成

优点:把时序电路转化为组合电路,极大降低了时序电路测试的复杂程度

缺点:需要额外增加电路面积和IO引脚,串行扫描移入移出的方式导致测试时间长

扫描深度:扫描路径上移位触发器的长度,是扫描路径设计的主要特征值。

Chapter7 边界扫描法

背景:板级、系统级的测试不仅是对单个IC或模块的测试,还包括IC之间、PCB之间的连接的测试。

因此将扫描路径法扩展到整个板级或系统级->边界扫描法。

1.边界扫描法

boundry scan逐渐从板级扩展到电路级。是一个对数字及混合集成电路的数字部分提供规范化测试存取端口和边界扫描结构的一个规范。

2.基本结构

(1)具有4或5个引脚的测试存取通道(Test Access Port,TAP)-元器件与外部通信的信号(如测试数据输入输出、测试方式选、测试时钟等)

(2)寄存器链-一组边界扫描寄存器、指令寄存器(接受、解释指令)和数字寄存器

(3)一个TAP控制器

如果系统包含多核元器件或模块,所有边界扫描单元串联起来

工作流程:TAP获取时钟和指令信息,把信息传递给选择的指令寄存器或数据寄存器,边界扫描寄存器根据指令选择操作。

正常操作:边界扫描寄存器是透明的,允许输入和输出信号自由地通过测试单元。

(1)测试存取通道

(1)测试存取通道

TAP是访问元器件内嵌入式测试支持功能的通用端口,TAP所有的输入输出都必须是专用的。

测试时钟、测试方式选择、串行测试数据输入、串行测试数据输出、测试系统复位

(2)TAP控制器

同步状态机,将测试时钟、测试方式选择信号译码,产生所需要的控制序列。在遇到TCK上升沿、TRST信号变为逻辑0、上电时才会改变状态

(3)寄存器链

指令寄存器+数据寄存器

测试逻辑结构中至少包含两种测试数据寄存器:旁路寄存器和边界扫描寄存器,可选择的还有:器件标志寄存器。每一个命名的寄存器的长度都是固定的,可由一个或多个指令访问。

旁路寄存器:提供一位的串行连接用于将当前不进行测试的IC的扫描链短接起来使得扫描路径最短化,

边界扫描寄存器BSR:最重要,最复杂。允许器件内测试数据的输入、输出等操作,也允许对器件外电路的测试。每一个边界扫描寄存器单元至少有两个数据段子、一定数目的时钟输入和控制输入,每一个单元内包含一个单级的移位寄存器,提供一个并行输入活人一个人并行输出。

器件标志寄存器DIR:32位标准寄存器,包含了器件版本号、器件型号、制造厂商等。主要用于标注器件制造厂商、系统诊断。

3.指令详解

3.指令详解

指令寄存器允许指令串行进入测试逻辑。TAP控制器使用的指令有两类:公用指令和专用指令。

公用指令

即用户可使用的指令。如旁路指令、采样指令、预装指令和外测试指令。外测试指令主要用于测试IC或PCB之间的互连或边界扫描设计以外的逻辑。

专用指令

是器件测试者或生产商专门设计的。

4.外测试

测试器件间互连是边界扫描测试的主要 目的之一

5.边界扫描描述语言

BSDL,Boundry-Scan Description Language是超高速集成电路硬件描述语言(VHDL)中的一个子集。主要基于器件知识描述完成设计的器件。分为:主体(entity)、组件(package)和组件体(package body)。

Chapter8 随机测试和伪随机测试

1.数字电路测试中测试生成的两种途径:

基于故障的确定性测试生成方法-测试图形长苏端,但生成过程复杂、试驾过程困难

生成符合随机特征的数据的测试生成方法-微处理器的测试软件算法生成随机或伪随机测试图形,通常故障覆盖率还比较高。缺点就是一般要增加额外的硬件,以及一些故障难以用随机的方法检测到。

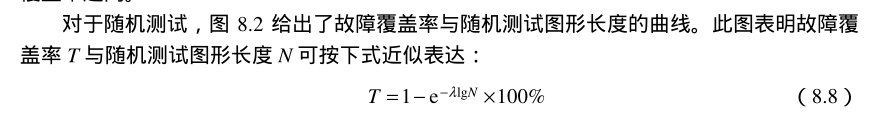

2.故障检测率

为了达到满足要求的故障覆盖率,测试图形的长度应该取多长->由两个并发事件的概率确定:故障在源处再现及故障传播到电路的一个输出端。

(1)测试图形长度:与测试施加时间成正比,满足覆盖率的测试长度一般不会超过1000。

(2)输入变量的优化:为了取得最小长度的测试图形

(2)输入变量的优化:为了取得最小长度的测试图形

3.伪随机序列

方法:复现关系;用无输入的线性反馈移位寄存器构成的伪随机序列生成电路,所生成的序列只与寄存器的初始状态和反馈方式有关

伪随机测试序列生成电路(PRSG)最常用的结构是线性反馈移位寄存器(LFSR),由一系列触发器组成,他们都是根据M序列理论设计及工作的。

外接形PRSG

内接型PRSG

混合连接型PRSG

Chapter9 内建自测试

1.自建内测试

BIST,Built-In Self Test:在电路内部建立测试生成、施加、分析和测试控制结构,使得电路能够测试自身。

BIST可分为两类:在线BIST和离线BIST。

在线BIST:测试在电路的正常功能条件下进行,不把被测电路置于测试方式,包括并发和非并发的方法。

离线BIST:测试不在电路的正常功能条件下进行,可以应用在系统级、板级和芯片级测试,也可以用在制造、现场和操作级测试,但不能测试实时故障。分为功能性离线BIST和结构性离线BIST。

BIST所用的测试图形生成器(TPG)常见的形式有两种:一种是使用多输出线性反馈移位寄存器的伪随机图形生成器(PRPG-并行)另一种是移位寄存器图形生成器(SRPG-串行)采用的单输出的自动方式线性反馈移位寄存器。

BIST所用的输出响应分析器也有两种:多输入特征分析寄存器(MISR)和单输入特征分析寄存器(SISR),均采用线性反馈移位寄存器。

2.内建自测试结构

包括:测试生成电路(激励)、数据压缩电路、比较分析电路、理想结果存储电路(ROM)和测试控制电路。

测试生成电路->测试图形->被测电路CUT->相应数据压缩,转换为特征符号->给出结果

被测电路:组合电路、时序电路、存储器和其他类型的电路,也可以是电路模块(核)。

3.测试生成

3.测试生成

方法:穷举测试、伪穷举测试、伪随机测试、适应测试生成

穷举测试:对电路的每一个状态及所有的状态转换都予以确认。适用于组合电路不适合于时序电路

伪随机测试:采用多个具有随机特性的测试图形来测试电路,但这些测试图形的生成是确定的,因此具有重复性。

加权测试生成:LFSR的固有属性使得产生的测试图形上每一位的0和1的概率基本相等,为了用尽可能少的测试图形来取得高的故障覆盖率,许多电路的测试图形的0,1的分布概率不同。

4.相应数据压缩

为了减少测试相应数据所用的空间并易于分析,常常把测试相应数据进行压缩。压缩成单个数值,称为特征符号。

但数据压缩会引起原有信息的丢失,这种情况被称为混淆。

4.1测试响应数据压缩的方法:

奇偶测试、“1”计数、跳变次数压缩、症候群计算、特征分析

5.BIST具体结构

内建自测试:被测电路CUT,用于测试生成的ALFSR,用于响应压缩的MISR、存储参考符号的ROM以及所需控制电路

自动测试:电路分为各种子电路,通过添加多路复用结构或路径敏化来实现,每一块电路可独立测试。

循环自建内测试

循环自建内测试

基于寄存器的测试,电路中的主要单元为自测试移位寄存器(STSR),其他不用于测试的寄存器用SR表示。

5.1内建逻辑块观测器

5.1内建逻辑块观测器

为了使得电路中触发器总数目最小,可以对电路中只完成逻辑功能的寄存器进行再设计,使得再具有测试生成和特征符号分析功能,这种寄存器结构成为内建逻辑块观测器。

5.2随机测试组合块

RTS,Random-Test Socket结合了扫描路径和BIST的特点,测试电路位于CUT外部,包括:PRPG伪随机测试生成电路,MISR多输入特征符号移位寄存器,SRSG串行输出伪随机生成电路,SSA单输入特征分析电路。

Chapter10 电流测试

1.Why we need 电流测试:功能测试是基于逻辑电平的故障检测,逻辑电平值通过测量原始输出的电压来确定,因此功能测试实际上是电压测试。但较大电路电压测试由于测试图形的生成相当复杂且较长,而电流测试的测试集相当短,对于固定型故障也有效。

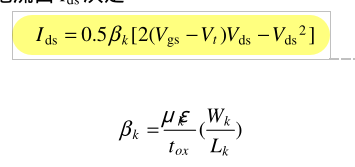

而CMOS电路低功耗,静态条件下由泄漏电流引起的功耗可以忽略,仅在转换期间电路存在较大电流。IDDQ可用来表示MOS电路静态时从电源获取的电流。

2.IDDQ测试:可以在测试成本非常低的前提上从根本找出电路的缺陷所在,以及即使电路功能正常,IDDQ仍可检测出桥接、短路、栅氧短路等物理缺陷。

常作为辅助性测试,不足:需要选择合适的测量手段,而且深亚微米技术静态电路已高的不可取分。

3.测试机理:检测CMOS电路静态时的漏电流,存在缺陷时静态电路大得多。采用静态电流分布曲线+计算均值来计算。

因此需要在每一个IDDQ测试图形施加后再等待一段时间才进行测量,因此测试速度比较慢。

IDDQ测试基本过程:

测试图形施加->等待瞬变过程消失->检查静态IDDQ是否超过阈值

难点:测试结构可能对被测量的数值有影响,因此需要采取额外措施排除影响。

4.

4.

IDDQ片外测试结构:供电电源增加一旁路电容,抑制电源和地回路之间造成的比较大的涌流。

IDDQ片内测试结构:嵌入式电流传感器:被测电路CUT,电流检测单元、比较器和参考电压Vref,将测的VIDD与Vref进行比较。

前提是分压器件是线性器件。

下图为被测电流与测量器件电压的关系:

5.故障检测

5.故障检测

IDDQ测试可用于检测固定故障和恒定通故障。以及:桥接、栅氧、开路故障、泄露故障、延迟故障

泄露故障:必要条件是存在泄露故障的两节点的逻辑值必须相反并且具有驱动能量

延迟故障:时间延迟的变化和静态电流的变化之间相关性极强,任何改变信号路径而造成电流增大的缺陷都会造成信号上升时间和下降时间的改变。因此可以从正常转换时间和有故障时的转换时间之差检测出延迟故障。

6.测试图形生成

电流测试的测试图形生成有两种方法:一种是基于电路级模型的另一种是泄露故障模型的。

Chapter 11 存储器测试

1.存储器包含数量众多、结构有规律的存储单元阵列,内部还有大量的模拟器件:存储电容、电压电路和敏感放大器(读电路)

SRAM测试方法包括扩:BIST、可测性结构、敏感图形测试 以上方法有的需要过多测试时间,有的需要过多的芯片面积

2.存储器模型:根据不同的设计层次,有物理级、逻辑级和系统级存储器电路模型。

2.1功能模型:存储阵列+存储器地址寄存器+译码器+读写电路+控制和存储数据寄存器

存储单元:在逻辑级可用一个D触发器描述,如常用的SRAM单元由两个交叉耦合的反相器组成,DRAM通过MOS电容存储位信息,写操作与SRAM写操作相似

影响存储器测试图形生成的重要因素有两个:一个是阵列结构一个是存储器所处的环境。

3.存储器的缺陷和故障模型

缺陷:材料的丢失、杂质的出现,栅氧断裂等以及干扰和噪声、单粒子翻转(SEU)

阵列故障类型:

故障检测第一步是确认缺陷处于阵列单元中还是处于周边电路中(周边电路=姨妈典礼、写驱动电路、敏感放大器、寄存器)

故障模型:固定故障、桥接故障、保持故障、变迁故障、耦合故障、图形敏感故障

固定故障:使得存储单元恒定存储0/1 简称SAF

变迁故障:当某个存储单边不能从0状态变迁到1状态 是SAF的一种特殊形式

耦合故障:其中一个单元的值可能因为其他单元状态的改变而变化,主要由于短接或寄生效应。有3种形式:反相、同势、桥接/状态

图形敏感故障:单元因阵列中其他单元的不同操作导致状态不正确。邻居图形敏感故障、

4.存储器测试类型

参数测试(DC+AC),功能测试、动态测试、IDDQ测试

功能测试包括测试图形的生成、对ATE的测试施加和测试结果分析

参数测试包括电压、电流和频率的测量

特征测试确定电路工作的限定条件

性能测试:测试产品参数,检查参数是否达到设计要求

5.存储器测试算法

两大类:一是当一些存储单元内容发生特定变化后,读出所有的存储单元;另一类是只读出内容已经变化的存储单元

测试效率:用尽可能少的测试图形检测到尽可能多的故障

MSCAN算法:

形式固定的存储器扫描序列(固定图形)然后读所有的存储单元

GALPAT算法:1(0)漫游或乒乓测试,可以检测SAF故障、变迁故障、译码电路的故障、一些状态耦合故障

6.各种存储器测试算法的对比

6.存储器测试方法

6.存储器测试方法

存储器直接存取测试:直接存取测试的原理图,核心是增加逻辑,提供测试设备对RAM的地址选择、数据输入、数据输出和测试控制的存取结构

存储器内建自测试

宏测试:测试设备把模块级/宏级的测试图形转换成芯片级的测试图形,利用电路内部的扫描路径进行测试施加,适合对性能妖气比较高的存储阵列。

7.存储器的冗余和修复

嵌入式存储器修复采用内建自修复(BISR),可以提高存储器的成品率从而提高整个系统的成品率。

硬修复:采用熔丝、阻熔丝和激光编程来熔断所有故障的行列,采用备用的行或列

软修复:采用地址映射程序旁路有故障的地址,将所有失效的地址分别存储起来然后地址映射程序把他们映射为无故障的地址

Chapter 12 SoC测试

1.SoC:单个硅片上集合多个系统,如微处理器核、存储器、锁相环电路、接口电路、逻辑电路、模数和数模电路

嵌入式核按照来源:核提供者,核用户

对SoC核的测试除了对不同类型器件的ASIC测试方法,还需要:嵌入式核的测试存取、测试控制、测试观察、测试开发语言等

需要——规范化核测试复用

2.SoC测试的基本问题

硬核、已经优化并映射到特定工艺的可复用模块

软核、以可综合的RTL级描述

固核:通过了布局布线对面积和性能进行了结构上的优化的可复用模块。

3.存取、控制和隔离

3.存取、控制和隔离

存取(access):核的输入设计施加好的激励信号然后在核的输出获取测试响应,与可测性和可控性相同

控制(control):使得某种方式的测试功能起作用或不起作用

隔离(isolation):把核的输入、输出端口与连接到这些端口的其他逻辑(或核)进行电分离,主要目的是避免被测试的核相对邻电路产生负面影响,也是为了测试相邻电路时保护核。

4.概念性的SoC测试结构:

包括测试源和测试收集、测试存取机构、测试壳

测试策略:

核的非边界扫描测试:因为边界扫描结构需要增加过多的面积,受到扫描深度的影响,难以实现高速测试

核的边界扫描测试:需要集成对内扫描、边界扫描、内建自测试和仿真特征

优点是结构好、通信协议标准化、易于理解

缺点是每一个核与核之间的互连测试都要经过边界扫描,测试时间非常长,不适合用于高速测试

5.SoC测试其他探索方向

(1)优化的DFT/BIST设计特征的结合

(2)TAM测试策略的研发

(3)SoC测试的集成和优化

(4)高级测试综合

(5)层次化测试结构复用