Xilinx公司提供了大量的存储器资源,包括了内嵌的块存储器、分布式存储器以及16位的移位寄存器。利用这些资源可以生成深度、位宽可配置的RAM、 ROM、FIFO以及移位寄存器等存储逻辑。其中,块存储器是硬件存储器,不占用任何逻辑资源,其余两类都是Xilinx专有的存储结构,由FPGA芯片的查找表和触发器资源构建的,每个查找表可构成16 1位的分布式存储器或移位寄存器。一般来讲,块存储器是宝贵的资源,通常用于大数据量的应用场合,而其余两类用于小数据量环境。

1.块存储器的组成和功能介绍

在Xilinx FPGA中,块RAM是按照列来排列的,这样保证了每个CLB单元周围都有比较接近的块RAM用于存储和交换数据。与块RAM接近的是硬核乘加单元,这样不仅有利于提高乘法的运算速度,还能形成微处理器的雏形,在数字信号处理领域非常实用。例如,在Spartan 3E系列芯片中,块RAM分布于整个芯片的边缘,其外部一般有两列CLB,如图4-120所示,可直接对输入数据进行大规模缓存以及数据同步操作,便于实现各种逻辑操作。

图4-120 Spartan3E系统芯片中块RAM的分布图

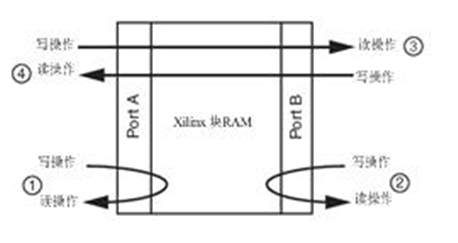

块RAM几乎是FPGA器件中除了逻辑资源之外用得最多的功能块,Xilinx的主流 FPGA芯片内部都集成了数量不等的块RAM硬核资源,速度可以达到数百兆赫兹,不会占用额外的CLB资源,而且可以在ISE环境的IP核生成器中灵活地对RAM进行配置,构成单端口RAM、简单双口RAM、真正双口RAM、ROM(在RAM中存入初值)和FIFO等应用模式,如图4-121所示。同时,还可以将多个块RAM通过同步端口连接起来构成容量更大的块RAM。

图4-121 块RAM组合操作示意图

1)单端口RAM模式

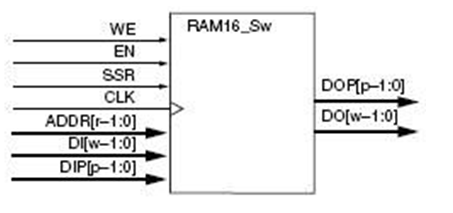

单端口RAM的模型如图4-122所示,只有一个时钟源CLK,WE为写使能信号,EN为单口RAM使能信号,×××为清零信号,ADDR为地址信号,DI和DO分别为写入和读出数据信号。

图4-122 Xilinx单端块RAM的示意模型

单端口RAM模式支持非同时的读写操作。同时每个块RAM可以被分为两部分,分别实现两个独立的单端口RAM。需要注意的是,当要实现两个独立的单端口RAM模块时,首先要保证每个模块所占用的存储空间小于块RAM存储空间的1/2。在单端口RAM配置中,输出只在 read-during-write模式有效,即只有在写操作有效时,写入到RAM的数据才能被读出。当输出寄存器被旁路时,新数据在其被写入时的时钟上升沿有效。

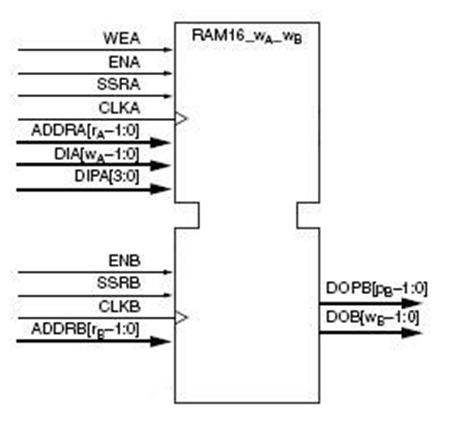

2)简单的双端口RAM

简单双端口RAM模型如图4-123所示,图中上边的端口只写,下边的端口只读,因此这种RAM也被称为伪双端口RAM(Pseudo Dual Port RAM)。这种简单双端口RAM模式也支持同时的读写操作。

图4-123 Xilinx简单双端口块RAM的示意模型

块RAM支持不同的端口宽度设置,允许读端口宽度与写端口宽度不同。这一特性有着广泛地应用,例如:不同总线宽度的并串转换器等。在简单双端口RAM模式中,块RAM具有一个写使能信号wren和一个读使能信号rden,当rden为高电平时,读操作有效。当读使能信号无效时,当前数据被保存在输出端口。当读操作和写操作同时对同一个地址单元时,简单双口RAM的输出或者是不确定值,或者是存储在此地址单元的原来的数据。

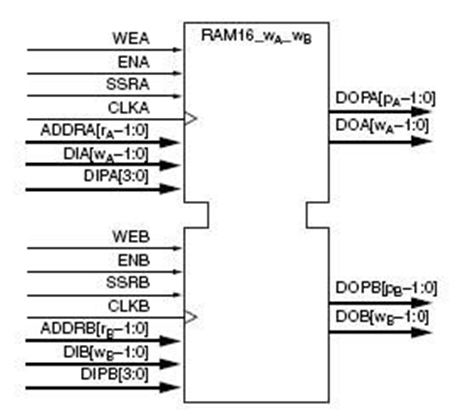

3)真正双端口RAM模式

真正双端口RAM模型如图4-124所示,图中上边的端口A和下边的端口B都支持读写操作,WEA、WEB信号为高时进行写操作,低为读操作。同时它支持两个端口读写操作的任何组合:两个同时读操作、两个端口同时写操作或者在两个不同的时钟下一个端口执行写操作,另一个端口执行读操作。

图4-124 Xilinx真正双端口块RAM的示意模型

真正双端口RAM模式在很多应用中可以增加存储带宽。例如,在包含嵌入式处理器MiroBlaze和DMA控制器系统中,采用真正双端口RAM模式会很方便;相反,如果在这样的一个系统中,采用简单双端口RAM模式,当处理器和DMA控制器同时访问RAM时,就会出现问题。真正双端口RAM模式支持处理器和DMA控制器同时访问,这个特性避免了采用仲裁的麻烦,同时极大地提高了系统的带宽。

一般来讲,在单个块RAM实现的真正双端口RAM模式中,能达到的最宽数据位为36比特*512,但可以采用级联多个块RAM的方式实现更宽数据位的双端口RAM。当两个端口同时向同一个地址单元写入数据时,写冲突将会发生,这样存入该地址单元的信息将是未知的。要实现有效地向同一个地址单元写入数据,A 端口和B端口时钟上升沿的到来之间必须满足一个最小写周期时间间隔。因为在写时钟的下降沿,数据被写入块RAM中,所以A端口时钟的上升沿要比B端口时钟的上升沿晚到来1/2个最小写时钟周期,如果不满足这个时间要求,则存入此地址单元的数据无效。

4)ROM模式

块RAM还可以配置成ROM,可以使用存储器初始化文件(.coe)对ROM进行初始化,在上电后使其内部的内容保持不变,即实现了ROM功能。

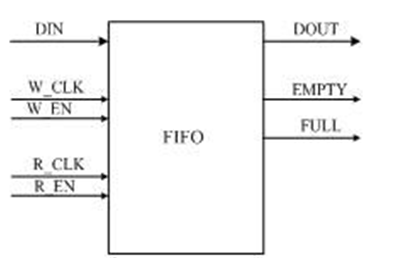

5)FIFO模式

FIFO即先入先出,其模型如图4-125所示。在FIFO具体实现时,数据存储的部分是采用简单双端口模式操作的,一个端口只写数据而另一个端口只读数据,另外在RAM(块RAM和分布式RAM)周围加一些控制电路来输出指示信息。FIFO最重要的特征是具备“满(FULL)”和“空(EMPTY)”的指示信号,当FULL信号有效时(一般为高电平),就不能再往FIFO中写入数据,否则会造成数据丢失;当EMPTY信号有效时(一般为高电平),就不能再从FIFO中读取数据,此时输出端口处于高阻态。

图4-125 Xilinx FIFO模块的示意模型

2.块RAM IP Core的使用

块RAM已在本书第3章有过介绍,这里就不再赘述。

3.ROM存储器IP Core的使用

对于ROM模块,主要是生成相应的.coe文件。下面以一个实例介绍如何借助MATLAB生成ROM的.coe文件。

例4-8 生成定点正余弦波形数值,形成.coe文件并加载到块ROM中。

整体过程主要分为下面的3步。

首先,利用MATLAB计算出正余弦波形的浮点值,并量化16比特的定点波形数值:

x= linspace(0,6.28,1024); //在区间[0,6.28]之间等间隔地取1024个点

y1=cos(x); //计算相应的正余弦值

y2=sin(x);

//由于正余弦波形的值在[0,1]之间,需要量化成16比特,先将数值放大

y1=y1*32678;

y2=y2*32768;

//再将放大的浮点值量化,并写到存放在C盘的文本中

fid = fopen('c:/cos_coe.txt', 'wt');

fprintf(fid, '%16.0f\n', y1); //在写文件的时候量化成16比特

fclose(fid)

fid = fopen('c:/sin_coe.txt', 'wt');

fprintf(fid, '%16.0f\n', y2);

fclose(fid)

其次,生成coe文件。在C盘根目录下,将cos_coe.txt和sin_coe.txt的后缀改成.coe,打开文件,把每一行之间的空格用文本的替换功能换成逗号“,”,并在最后一行添加一个分号“;”。最后在文件的最开始添加下面两行:

memory_initialization_radix=10;

memory_initialization_vector =

然后保存文件退出。

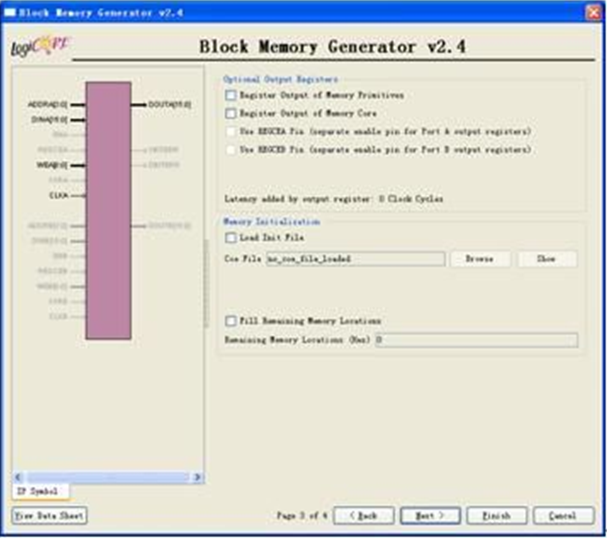

最后,将coe文件加载到BLOCKROM所生成的ROM中。新建一个BLOCKRAM的IP core,其位置为“Memories & Storage Elements RAMs & ROMS Block Memory Generator v2.4”,在第一页选择single port rom,在第二页选择位宽为16、深度为1024,在第三页下载coe文件,如图4-126所示,然后双击“Finish”,完成IP core的生成。如果coe文件生成的不对,图中用椭圆标志之处是红色的,coe文件错误的类型主要有数据基数不对和数据的长度不对这两类。

图4-126 块ROM加载coe文件的用户配置界面