- 1vivo 在离线混部探索与实践

- 2[数据集][目标检测]鸟类检测数据集VOC+YOLO格式11758张200类别_鸟类识别的数据库

- 3zabbix自定义监控_zabbix自定义监控 csdn

- 4Navicat 系列软件闪退、崩溃_navicat11装完闪退

- 5立可得_第2章_新零售_重构人、货、场_立可得项目数据导入

- 6Linux学习笔记——进程间通信_在linux中进程间通信

- 7华为EMUI8/9刷机直通车:一篇文章拿下安卓13_potatonv

- 8Mac下查看公网以及内网IP地址_macos看内网ip

- 9深入理解fork、进程状态(9)_fork进程

- 10面试官,你再问我滑动窗口问题试试?我有解题模板,不怕!

3D封装技术发展_三维叠层封装的分类

赞

踩

长期以来,芯片制程微缩技术一直驱动着摩尔定律的延续。从1987年的1um制程到2015年的14nm制程,芯片制程迭代速度一直遵循摩尔定律的规律,即芯片上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。但2015年以后,芯片制程的发展速度进入了瓶颈期,7nm、5nm制程的芯片量产进度均落后于预期。全球领先的晶圆代工厂台积电3nm制程芯片量产遇阻,2nm制程芯片的量产更是排到了2024年后,芯片制程工艺已接近物理尺寸的极限1nm,芯片产业迈入了后摩尔时代。

在后摩尔时代,芯片的发展逐渐演化出了不同的技术方向。其中之一的“More Moore”方向,主要是研发新方法沿着摩尔定律的道路继续向前推进,不断缩小芯片制程。而另一个方向则是“More than Moore”(超越摩尔),主要是发展之前摩尔定律演进过程中未开拓的技术方向。先进封装便是超越摩尔技术方向的一种重要实现路径。

1 三维(3D)封装技术的研究

1.1 3D封装技术的种类

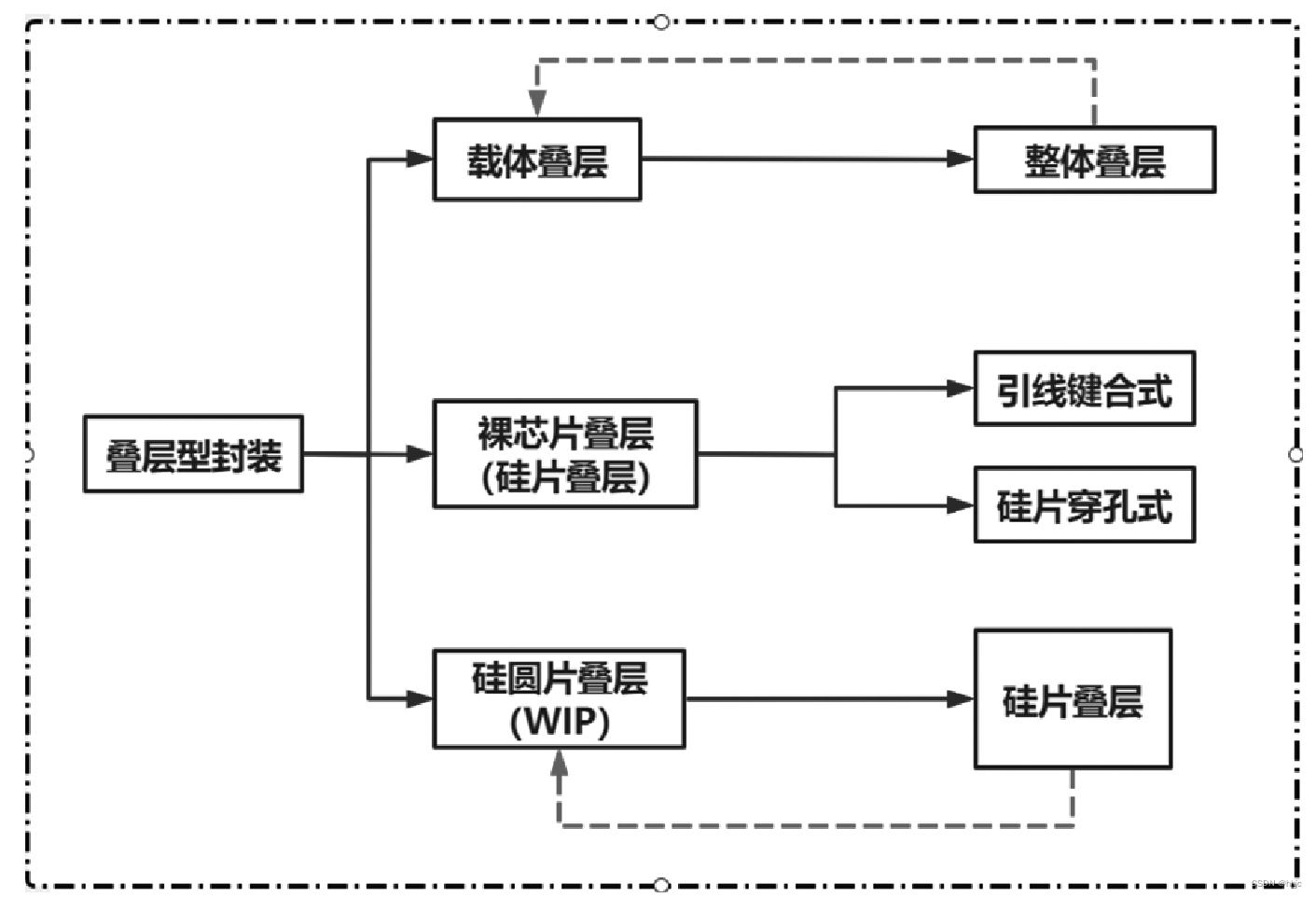

目前该技术主要有三种:叠层型3D封装(POP)、硅圆片规模 集成封装(WSI)以及埋置型3D封装。如图1所示。 目前,在所有3D封装技术中发展最为迅速的是叠层型3D封装, 其主要优势如下:

●采用“叠装互连”的封装方法,推动封装的体积向小型化发展;

●相比之下,叠层型3D封装具有更好的兼容性,易于进行规 模化的生产;

●3D封装技术功耗小,可使3D元件以更快的转换速度运转, 提高工作效率。

1.2 叠层型3D封装技术的研究

1.2.1 叠层型3D封装技术的工作机理

在2D平面电子封装的基础上,利用高密度的互连技术,让芯 片在水平和垂直方向上获得延展,在其正方向堆叠2片以上互连的 裸芯片封装,实现高带宽、低功耗,如今3D封装已从芯片堆叠发 展到封装堆叠。

1.2.2 叠层型3D封装技术的类型

叠层型3D封装分为三大类:载体叠层、裸芯片叠层(硅片叠 层)、硅圆片叠层(WIP)。如图2所示。 其中的裸芯片叠层(硅片叠层)安装互连技术分为两种:

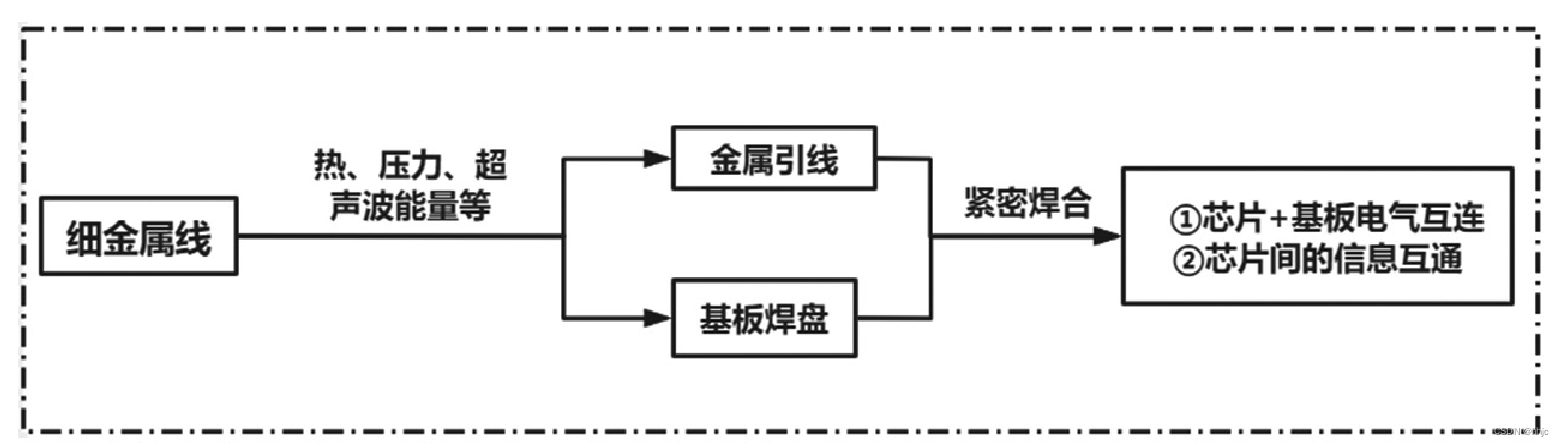

(1)引线键合式:是一种使用细金属线,使芯片的I/O端与对应 的封装引脚或基板上布线焊区互连,再此基础上利用加热、加压、 超声波能量等营造塑性变形,使金属引线与基板焊盘紧密焊合。由 此实现芯片与基板间的电气互连和芯片间的信息互通。如图3所示。

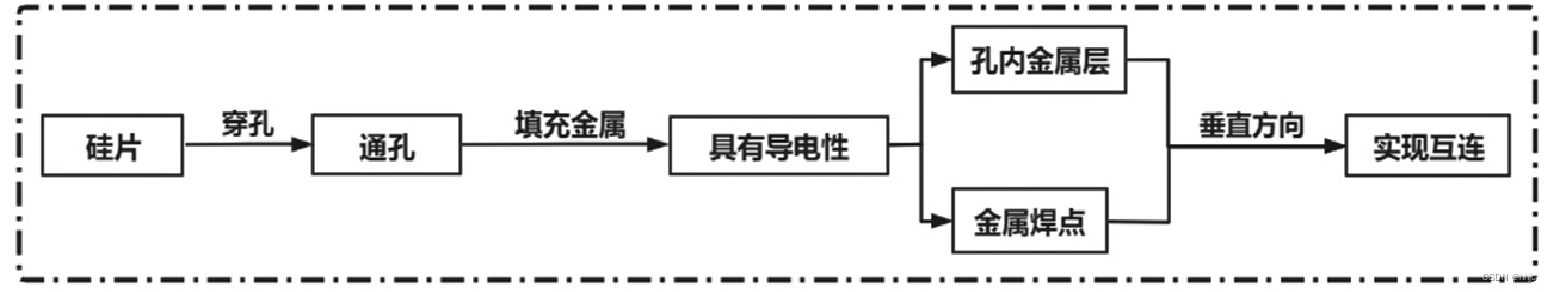

(2)硅片穿孔式:在硅片穿孔后形成的通孔中填充金属,在元件具有导电性的基础下即可实 现孔内金属焊点和金属层在垂直 方向的互相连通,由此完成硅片 穿孔过程。

1.2.2 叠层型3D封装技术的应用

一方面,由于该技术具有体 积小、多功能性、集成度高的优 势,因此其在便携式电子产品领 域具有极为广泛的应用,例如: 移动端设备、mp3、数码相机等 小型电子产品。 另一方面,在我国不断推进 芯片技术的过程中,阻碍其发展 的一大因素是芯片的数据传输速度。随着芯片工作时间的增加,组成芯片的各元件寿命降低,会 导致芯片间的数据传输速度变慢。而叠层型3D封装技术具有高效 率、规模化程度高的特点,则可以在降低生产成本的同时,提高 芯片运转过程的工作速度。

2 微电子3D封装的未来发展趋势

目前3D封装技术在芯片中的应用是一大发展趋势,芯片技术 作为衡量国家科技实力的核心技术,要实现质的飞跃必然需要在研 究方法中寻求创新。该技术在芯片中的应用具有以下特点: ●由二维到三维,从平面型封装转为立体型封装; ●单芯片转为多芯片发展; ●独立芯片封装转为系统集成封装。 不仅如此,近年来在移动便携设备的需求量激增和大众对功能 丰富的电子产品的狂热追求下,立体封装和系统集成封装成为主 流封装趋势,致力于将电子设备最小化的同时保留其完整的功能 性。在将设备性能、综合工艺、封装空间、封装性价比等优势资 源整合后,微电子3D封装技术已达到规模化生产的标准,为未来 电子信息市场打下了坚实的基础。

图1 3D封装技术种类及其工作原理

图2 叠层型封装的类型和结构

图3 引线键合工作原理

图4 硅片穿孔式工作简图