- 1当学习《创新创业执行力》课程遇到困难,我们该……_创新创业执行力 农大课程

- 2python中的字典(Dictionary)_python 字典

- 3AI写作速成:如何用人工智能轻松提升文案品质?

- 4【机器学习(11)】决策树模型:CART分类及回归树可视化_决策树回归可视化

- 5【Kafka】kafka-eagle几个指标含义_kafka-eagle 几个指标含义

- 62024年度最佳大型语言模型(LLMs)汇总_2024已存在的大型语言模型有哪些

- 7PyTorch中文教程 | (10) 对抗性示例生成_torchattacks cdsn

- 8Python循环语句_for循环_python for循环

- 9C# FileStream类的文件流、文件读取写入操作_filestream读取文件

- 10语言模型srilm(一) 基本用法_语言模型 插值合并

I.MX6ULL_Linux_基础篇(6) soc资源介绍_i.mx6ull芯片

赞

踩

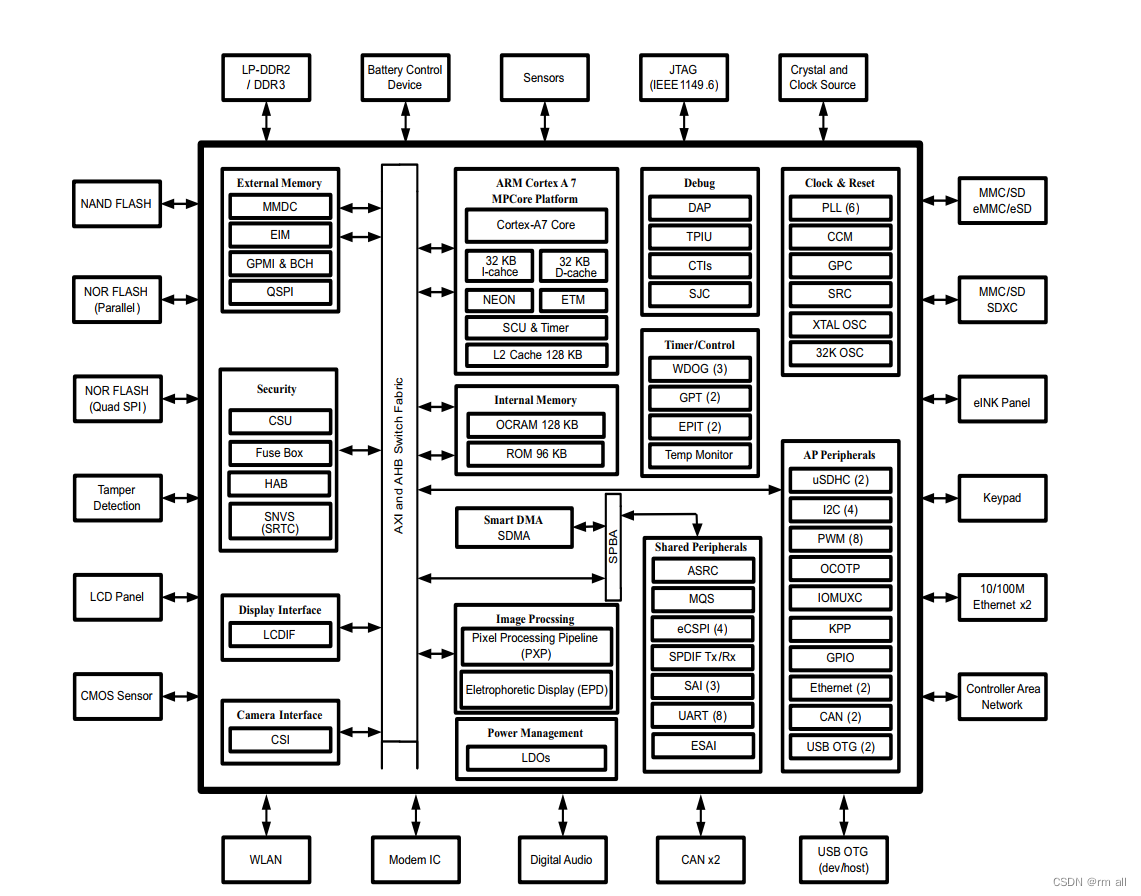

要学嵌入式 Linux 驱动开发肯定需要一个硬件平台,也就是开发板,本系列使用的是正点原子出品的 I.MX6U-Mini 开发板。 ALPHA 是全功能开发板, Mini 是精简版。这两款都是以 NXP 的 I.MX6ULL 为核心的 Cortex-A7 开发平台,板载资源丰富,非常适合以前学过Cortex-M 内核单片机(比如 STM32)的工程进阶嵌入式 Linux 开发。开发板是全功能也好,精简版也好,本系列的文章主要是打基础,熟框架,对系统分析到位,对驱动编写熟知。

SOC

i.MX 6ULL处理器代表了恩智浦在集成多媒体产品方面的最新成就,该产品提供高性能处理和高度功能集成,面向不断增长的连接设备市场。i.MX 6ULL是一个高性能、超高效的处理器系列,采用恩智浦先进的单Arm Cortex®-A7内核,其工作速度高达792 MHz。i.MX 6ULL包括集成电源管理模块,可降低外部电源的复杂性并简化电源排序。该系列中的每个处理器提供各种存储器接口,包括LPDDR2、DDR3、DDR3L、Raw和Managed NAND闪存、NOR闪存、eMMC、Quad SPI以及用于连接外围设备的各种其他接口,如WLAN、蓝牙™, GPS、显示器和摄像头传感器。

i.MX 6ULL处理器特别适用于以下应用:

•远程通信 •音频播放 •连接的设备 •物联网网关 •访问控制面板 •人机界面(HMI)•便携式医疗保健 •IP电话 •智能电器 •电子阅读器

i.MX 6ULL处理器的功能包括:

•单核Arm Cortex-A7-单核A7提供了经济高效的解决方案。

•多级存储系统处理器的多级存储系统基于L1指令和数据缓存、二级缓存以及内部和外部存储器。处理器支持许多类型的外部存储设备,包括DDR3、低电压DDR3,LPDDR2、NOR闪存、NAND闪存(MLC和SLC)、OneNAND™, Quad SPI和托管NAND,包括eMMC版本4.4/4.41/4.5。

•智能速度技术在整个集成电路中实现电源管理多媒体功能和外围设备,以活动和各种低功耗消耗最小功率电源模式。

•动态电压和频率缩放通过缩放电压来提高设备的功率效率以优化性能。

•多媒体处理器的多媒体性能通过多级增强缓存系统,NEON™ MPE(媒体处理器引擎)协处理器,可编程智能DMA(SDMA)控制器、异步音频采样率转换器、电泳

显示器(EPD)控制器和像素处理流水线(PXP)以支持2D图像处理,包括颜色空间转换、缩放、alpha混合和旋转。

•2个以太网接口—2个10/100 Mbps以太网控制器。

•人机界面每个处理器支持一个数字并行显示界面。

•接口灵活性每个处理器支持与多种接口的连接:两个带PHY的高速USB,多个扩展卡端口(高速MMC/SDIO主机两个12位ADC模块,具有多达10个总输入通道和两个CAN端口。

•高级安全处理器提供硬件支持的安全功能,使安全电子商务、数字版权管理(DRM)、信息加密、安全引导、AES-128加密、SHA-1、SHA-256硬件加速引擎和安全软件下载。这个i.MX 6ULL安全参考手册(IMX6ULLSRM)中讨论了安全功能。集成电源管理处理器集成线性调节器并在内部生成不同域的电压电平。这大大简化了系统电源管理结构有关i.MX 6ULL功能的全面列表。

| Part Number | Feature | Package | Junction Temperature |

| MCIMX6Y2CVM08AA MCIMX6Y2CVM08AB | Features supports: • 792 MHz, industrial grade for general purpose • Basic security • With LCD/CSI • CAN x2 • Ethernet x2 • USB OTG x2 • ADC x2 • UART x8 • SAI x3 • ESAI x1 • Timer x4 • PWM x8 • I2C x4 • SPI x4 | 14 x 14 mm, 0.8 pitch MAPBGA | -40 to +105 |

模块列表

| 模块名称 | 模块名解释 | 子系统 | 说明 |

| ADC1 ADC2 | 模数转换器 | — | ADC是一个12位通用模数转换器。 |

| Arm | Arm 内核 | Arm | Arm Core平台包括1x Cortex-A7内核。它还包括相关的子块,如2级缓存控制器、SCU(Snoop Control Unit)、GIC(General Interrupt Controller)、专用定时器、看门狗和CoreSight调试模块。 |

| ASRC | 异步采样率转换器 | 多媒体外设 | 异步采样率转换器(ASRC)将与输入时钟相关联的信号的采样率转换为与不同输出时钟相关的信号。ASRC支持大约-120dB THD+N的多达10个信道的并行采样率转换。每个通道的采样率转换与一对输入和输出采样率相关联。ASRC最多支持三个采样率对。 |

| BCH | 二进制BCH ECC处理器 | 系统控制外围设备 | BCH模块为NAND闪存控制器(GPMI)提供多达40位ECC加密/解密 |

| CCM GPC SRC | 时钟控制模块, 通用电源控制器, 系统重置控制器 | 时钟、重置和电源控制 | 这些模块负责系统中的时钟和复位分配,还负责系统电源管理。 |

| CSI | 并行CSI | 多媒体外围设备 | CSI IP提供并行CSI标准摄像机接口端口。CSI并行数据端口最多24位。它被设计为支持24位RGB888/YUV444、CCIR656视频接口、8位YCbCr、YUV或RGB,以及8位/10位/16位bayer数据输入。 |

| CSU | 中央安全单元 | 安全 | 中央安全单元(CSU)负责在i.MX 6ULL平台内制定全面的安全政策。 |

| DAP | 调试端口 | 系统控制外围设备 | DAP为调试器提供实时访问,而无需停止内核: •系统内存和外围寄存器 •所有调试配置寄存器 DAP还提供对JTAG扫描的调试器访问链。DAP模块位于Cortex-A7核心平台内部。 |

| DCP | 数据协处理器 | 安全 | 该模块支持通常用于安全功能的通用加密和哈希函数。因为它的基本工作是从 内存到内存,它还结合了内存复制(memcopy)功能,用于调试和作为比基于DMA的方法更有效的在内存块之间复制数据的方法。 |

| eCSPI1 eCSPI2 eCSPI3 eCSPI4 | 可配置SPI | 连接外围设备 | 全双工增强型同步串行接口,数据速率高达52 Mbit/s。它可配置为支持主/从模式,四芯片选择支持多个外设。 |

| EIM | NOR闪存/PSRAM接口 | 连接外围设备 | EIM NOR-FLASH/PSRAM提供: •支持16位(仅在多路复用IO模式下)PSRAM存储器(同步和异步操作模式),频率较慢 •支持16位(仅在多路复用IO模式下)NOR闪存,频率较慢 •多芯片选择 |

| ENET1 ENET2 | 以太网控制器 | 连接外围设备 | 以太网媒体访问控制器(MAC)设计为支持10/100 Mbit/s以太网/IEEE 802.3网络。需要外部收发器接口和收发器功能来完成与媒体的接口。该模块具有支持IEEE 1588标准的专用硬件。有关详细信息,请参阅参考手册的ENET章节。 |

| EPDC | 电泳式电子纸面板显示控制器(墨水屏) | 多媒体外围设备 | EPDC是一种功能丰富、低功耗、高性能的直接驱动有源矩阵EPD控制器。它专门设计用于驱动E-INKTM EPD面板,支持各种TFT背板。 |

| EPIT1 EPIT2 | 增强型周期中断计时器 | 计时器外围设备 | 每个EPIT都是一个32位“设置并忘记”计时器,在软件启用EPIT后开始计数。它能够以最小的处理器干预,以规则的间隔提供精确的中断。它有一个12位预分频器,用于分频输入时钟频率,以获得中断发生所需的时间设置,计数器值可以随时编程。 |

| ESAI | 增强型串行音频接口 | 连接外围设备 | 增强型串行音频接口(ESAI)提供了一个全双工串行端口,用于与各种串行设备(包括工业标准编解码器、SPDIF收发器和其他处理器)进行串行通信。 ESAI由独立的发射机和接收机部分组成,每个部分都有自己的时钟发生器。所有串行传输都与时钟同步。附加的同步信号用于描绘字帧。正常操作模式用于以周期性速率(每个周期一个字)传输数据。网络模式也适用于定期传输;然而,它支持每个周期最多32个字(时隙)。该模式可用于构建时分复用(TDM)网络。相反,按需模式用于非周期性数据传输,并在数据可用时以高速串行传输数据。 ESAI具有12个引脚,用于与外部设备的数据和时钟连接 |

| FLEXCAN1 FLEXCAN2 | 灵活的控制器局域网 | 连接外围设备 | CAN协议最初(但不仅如此)被设计为用作车辆串行数据总线,满足该领域的具体要求:实时处理、车辆电磁干扰(EMI)环境中的可靠操作、成本效益和所需带宽。FlexCAN模块是CAN协议规范2.0 B版的完整实现,支持标准和扩展消息帧。 |

| GPIO1 GPIO2 GPIO3 GPIO4 GPIO5 | 通用I/O模块 | 系统控制外围设备 | 用于外部IC的通用输入/输出。每个GPIO模块支持32位I/O。 |

| GPMI | 通用存储器接口 | 连接外围设备 | GPMI模块支持多达8个NAND设备和NAND闪存控制器(GPMI2)的40位ECC加密/解密。GPMI支持每个NAND设备的单独DMA通道。 |

| GPT1 GPT2 | 通用定时器 | 计时器外围设备 | 每个GPT都是一个32位“自由运行”或“设置并忘记”模式定时器,带有可编程的预分频器和比较和捕获寄存器。计时器计数器值可以使用外部事件来捕获,并且可以被配置为在输入脉冲的前沿或后缘触发捕获事件。当定时器被配置为在“设置并忘记”模式下运行时,它能够以最小的处理器干预以规则的间隔提供精确的中断。计数器具有输出比较逻辑,以提供比较时的状态和中断。此计时器可以配置为运行 在外部时钟或内部时钟上。 |

| LCDIF | LCD接口 | 连接外围设备 | LCDIF是一种通用显示控制器,用于驱动各种尺寸和性能不同的显示设备。LCDIF设计为支持傻的(同步24位并行RGB接口)和智能(异步并行MPU接口)LCD设备。 |

| MQS | 中等质量声音 | 多媒体外围设备 | MQS用于通过两个标准数字GPIO引脚生成2通道中等质量的类似PWM的音频。 |

| PWM1 PWM2 PWM3 PWM4 PWM5 PWM6 PWM7 PWM8 | 脉冲宽度调制 | 连接外围设备 | 脉宽调制器(PWM)具有16位计数器,并被优化为从存储的样本音频图像生成声音。它使用16位分辨率和4x16数据FIFO来生成声音。 |

| PXP | 像素处理管道 | 显示器外围设备 | 一种高性能像素处理器,能够实现1像素/时钟性能,用于组合操作,如颜色空间转换、阿尔法混合、伽马映射和旋转。PXP增强了专门用于灰度应用的功能。此外,PXP支持静态图像和视频处理应用程序的传统像素/帧处理路径,允许其与集成EPD接口。 |

| RNGB | 随机数生成器 | 安全 | 随机数生成模块。 |

| QSPI | 四线SPI | 连接外围设备 | 四SPI模块充当外部串行闪存设备的接口。本模块包含以下功能: •灵活的序列引擎,支持各种闪存供应商设备 •单线/双线/四线操作模式 •单数据速率/双数据速率操作模式 •并行闪存模式 •DMA支持 •对连接的闪存设备的内存映射读取访问 •多主机访问,每个主机具有优先级和灵活可配置的缓冲区 |

| SAI1 SAI2 SAI3 | — | — | SAI模块提供了一个同步音频接口(SAI),支持具有帧同步的全双工串行接口,如I2S、AC97、TDM和编解码器/DSP接口。 |

| SDMA | 智能直接内存访问 | 系统控制外围设备 | SDMA是多通道灵活的DMA引擎。它通过卸载动态数据路由中的各种内核,帮助最大化系统性能。它具有以下特点: •由16位指令集微RISC引擎驱动 •多通道DMA支持多达32个时分复用DMA通道 •48个事件,完全灵活地触发任何信道组合 •内存访问,包括线性、FIFO和2D寻址 •Arm和SDMA之间的共享外设 •非常快速的上下文切换,基于2级优先级的抢占式多任务 •具有自动刷新和预取功能的DMA单元 •针对DMA传输的灵活地址管理(增量、减量以及源地址和目标地址无地址更改) •DMA端口可以处理单元定向和双向流(复制模式) •最多8字缓冲区,用于EMIv2.5的可配置突发传输 •支持字节交换和CRC计算 •脚本和API库可用 |

| SJC | 系统JTAG控制器 | 系统控制外围设备 | SJC向内部逻辑提供符合JTAG TAP标准的JTAG接口。i.MX6ULL处理器使用JTAG端口进行生产、测试和系统调试。此外,SJC提供符合IEEE1149.1和IEEE1149.6标准的BSR(边界扫描寄存器)标准支持。在平台初始实验室启动期间,JTAG端口必须可访问,用于制造测试和故障排除,以及授权实体的软件调试。i.MX 6ULL SJC包含三种安全模式,用于防止未经授权的访问。通过eFUSE配置选择模式。 |

| SNVS | 安全非易失性存储 | 安全 | 安全非易失性存储,包括安全实时时钟、安全状态机、主密钥控制以及违规/篡改检测和报告。 |

| SPDIF | Sony Philips数字互连格式 | 多媒体外围设备 | 一种标准音频文件传输格式,由索尼和菲利普斯公司联合开发。具有发射器和接收器功能。 |

| System Counter | — | — | 系统计数器模块是一个可编程系统计数器,它为Cortex -a系列内核提供共享时基,作为Arm通用计时器架构的一部分。它适用于计数器始终通电并支持多个无关时钟的应用。 |

| TSC | 触摸屏 | 触摸控制器 | 带有触摸控制器,支持4线和5线电阻式触摸面板。 |

| TZASC | 信任区域地址空间控制器 | 安全 | TZASC(TZC-380 by Arm)提供预期应用所需的安全地址区域控制功能。它用于DRAM控制器的路径 |

| UART1 UART2 UART3 UART4 UART5 UART6 UART7 UART8 | UART接口 | 连接外围设备 | 每个UARTv2模块支持以下串行数据传输/接收协议和配置: •7或8位数据字、1或2个停止位、可编程奇偶校验(偶数、奇数或无) •可编程波特率高达5 Mbps。 •Tx上的32字节FIFO和Rx上的32个半字FIFO支持自动波特率 |

| uSDHC1 uSDHC2 | SD/MMC和SDXC增强型多媒体卡/安全数字主机控制器 | 连接外围设备 | i.MX6ULL特定SoC特性:所有四个MMC/SD/SDIO控制器IP都是相同的,并且基于uSDHC IP。他们是: •完全符合多媒体卡系统规范v4.5/4.2/4.3/4.4/4.4/1中定义的MMC命令/响应集和物理层,包括高容量(大小>2 GB)卡HC MMC。 •完全符合SD存储卡规范v3.0中定义的SD命令/响应集和物理层,包括高达2 TB的高容量SDXC卡。 •完全符合SDIO卡规范第E1部分3.0版中定义的SDIO命令/响应集和中断/读取等待模式。两个端口支持: •高达UHS-I SDR104模式(最大104 MB/s)的SD和SDIO卡的1位或4位传输模式规范 •1位、4位或8位传输模式规格,适用于SDR和DDR模式下最高52 MHz的MMC卡(最高104 MB/s) •HS200模式下高达200 MHz的eMMC芯片的4位或8位传输模式规范(最大200 MB/s)但是,SoC级集成和I/O复用逻辑将功能限制在以下方面: •实例#1和#2主要用作板载外设的接口。这些端口配备有“卡检测”和“写入” 保护”垫,不支持硬件重置。 •所有端口均可使用1.8 V和3.3 V卡。在四位配置(SD接口)中,端口#1和#2有两个完全独立的I/O电源域。 |

| USB | 通用串行总线2.0 | 连接外围设备 | USBO2(USB OTG1和USB OTG2)包含: •两个高速OTG 2.0模块,集成HS USB PHY •支持八个发送(TX)和八个接收(Rx)端点,包括端点0 |

| WDOG1 WDOG3 | 看门狗 | 计时器外围设备 | 监视计时器在每个计数期间支持两个比较点。每个比较点都可配置为触发Arm核心的中断,第二个点触发WDOG线上的外部事件。 |

| WDOG2 (TZ) | 看门狗(TrustZone) | 计时器外围设备 | TrustZone看门狗(TZ WDOG)计时器模块通过提供一种逃离正常模式并强制切换到TZ模式的方法来防止TrustZone饥饿。TZ饥饿是指正常操作系统阻止切换到TZ模式的情况。这种情况是不可取的,因为它会危及系统的安全性。TZ WDOG模块激活后,必须由TZ软件定期维护。如果未进行维修,计时器将超时。超时后,TZ WDOG断言一个TZ映射中断,该中断强制切换到TZ模式。如果仍然没有服务,TZ WDOG将向CSU发出安全违规信号。TZ WDOG模块不能通过正常模式SW编程或停用。 |

Power Modes

i.MX 6ULL具有以下电源模式:

•运行模式:CPU处于活动状态,芯片的某些部分可以是时钟门控或电源门控。支持多个电压/频率缩放设置点,以实现节能;

•低功耗模式:CPU处于WFI状态或电源门,芯片的某些部分可以关闭以节省电源。暂停、低功耗空闲、系统空闲被视为RUN模式的子模式;

•SNVS模式:只有RTC和篡改检测逻辑激活,12个GPIO处于低功耗状态保持模式;

•关闭模式:所有电源轨均关闭。

下表总结了所有电源模式下的外部电源状态。

| Power Rail | RUN | Low Power | SNVS | OFF |

| VDD_SOC_IN | ON | ON | OFF | OFF |

| VDD_HIGH_IN | ON | ON | OFF | OFF |

| VDD_SNVS | ON | ON | ON | OFF |

| USB_OTG1_VBUS USB_OTG2_VBUS | ON / OFF | ON / OFF | OFF | OFF |

| NVCC_DRAM_2P5 | ON | ON | OFF | OFF |

| VDDA_ADC_3P3 | ON / OFF | ON / OFF | OFF | OFF |

| NVCC_DRAM | ON | ON | OFF | OFF |

| NVCC_XXX | ON / OFF | ON / OFF | OFF | OFF |