热门标签

热门文章

- 1人工智能概念

- 2七天入门大模型 :提示词工程 Prompt Engineering,最全的总结来了!_大模型 提示工程

- 3CRNN:文本序列识别

- 4Proxmox ve(PVE)更换国内源_pve8 替换国内源

- 52022年(23届)电子信息/通信工程夏令营保研/考研复试经验贴(吉林大学通信工程学院篇)_吉林大学信通保研

- 6mac下提示MAC电脑GIT提交代码到GITHUB提示GIT-CREDENTIAL-OSXKEYCHAIN 验证解决方案

- 7Linux I2C 驱动_linuxiic设备

- 8CDH大数据平台 27Cloudera Manager Console之superset之Python相关包安装(markdown新版一)

- 9Linux系统中对SSD硬盘优化的方法_ext4针对 ssd优化

- 10CUDA kernel errors might be asynchronously reported at some other API call,so the stacktrace below m

当前位置: article > 正文

XILINX DRP接口时序_xilinx gtx 用drp接口配置linerate的计算表格

作者:Cpp五条 | 2024-03-11 17:14:54

赞

踩

xilinx gtx 用drp接口配置linerate的计算表格

详细说明见UG480文档第63页。

DRP全称Dynamic Reconfiguration Port,也就是动态重配置端口。

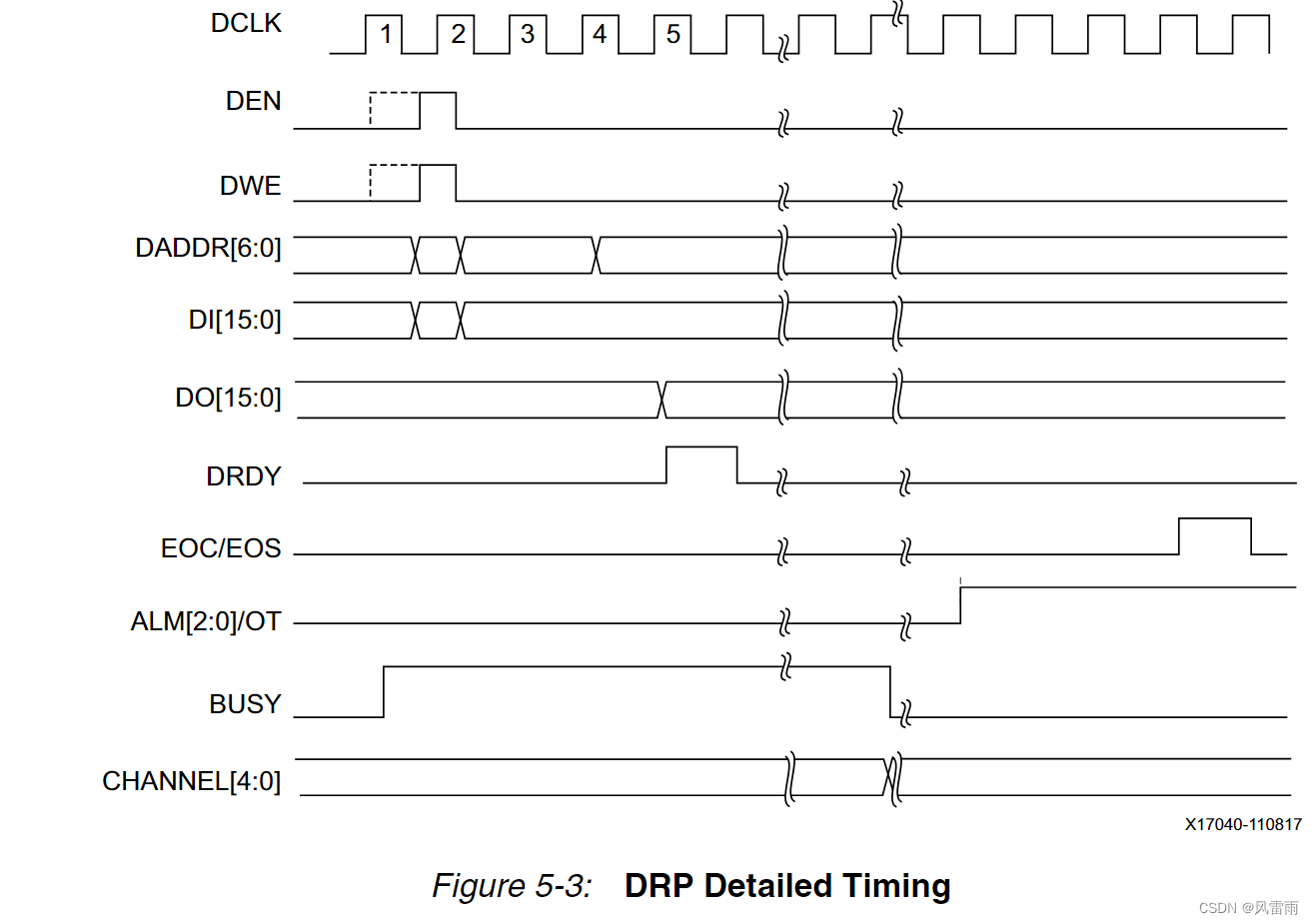

下图所示为DRP的读写时序:

DRP支持读写操作,在DEN为高电平(应该只保持一个DCLK时钟周期)的时候,在DCLK的上升沿锁存DWE(写使能)、DADDR(DRP地址)信息。

DRDY为低电平的时候才能读写DRP端口。

写操作:DEN、DWE信号为高电平(7系列要求只保持一个时钟周期的高电平)、DI、DADDR在DCL看上升沿被采集,DRDY拉高后标识数据被成功写入DRP寄存器。

读操作:DWE为低电平,读数据在DRDY为高的时候,在DO上有效输出。DRDY应该被用来抓取DO信号。

应用中要配置GTH、GTX接口的时候,就需要用到该时序,其相应的寄存器列表则在UG476的“DRP Address Map of the GTX/GTH Transceiver”部分。

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Cpp五条/article/detail/220005

推荐阅读

相关标签