- 1软件测试之-软件缺陷管理 _bug处理流程图

- 2关于MPU6050姿态解算的一阶互补滤波方法(从原理到代码实现)_互补滤波系数公式

- 3简单易懂的Docker下载安装教程:快速上手容器化应用

- 4GPU在外卖场景精排模型预估中的应用实践_大模型训练场景gpu需求量如何评估

- 5报告 | 腾讯知文,从0到1打造下一代智能问答引擎【CCF-GAIR】

- 6Mybatis中对象关系映射_mybatis映射对象

- 7【WSN定位】基于chan算法、fang算法、taylor算法和最小二乘定位算法lsm实现目标定位matlab源码_chan算法和最小二乘法

- 8LDA主题模型及Python实现_python lda模型主题分析

- 9using-aws-s3-buckets-cloudfront-distribution-with-craft-cms_yxokd

- 10在群晖NAS部署_开源在线项目任务管理工具【dooTask】

VIVADO中MIG应用仿真(一)_mig仿真

赞

踩

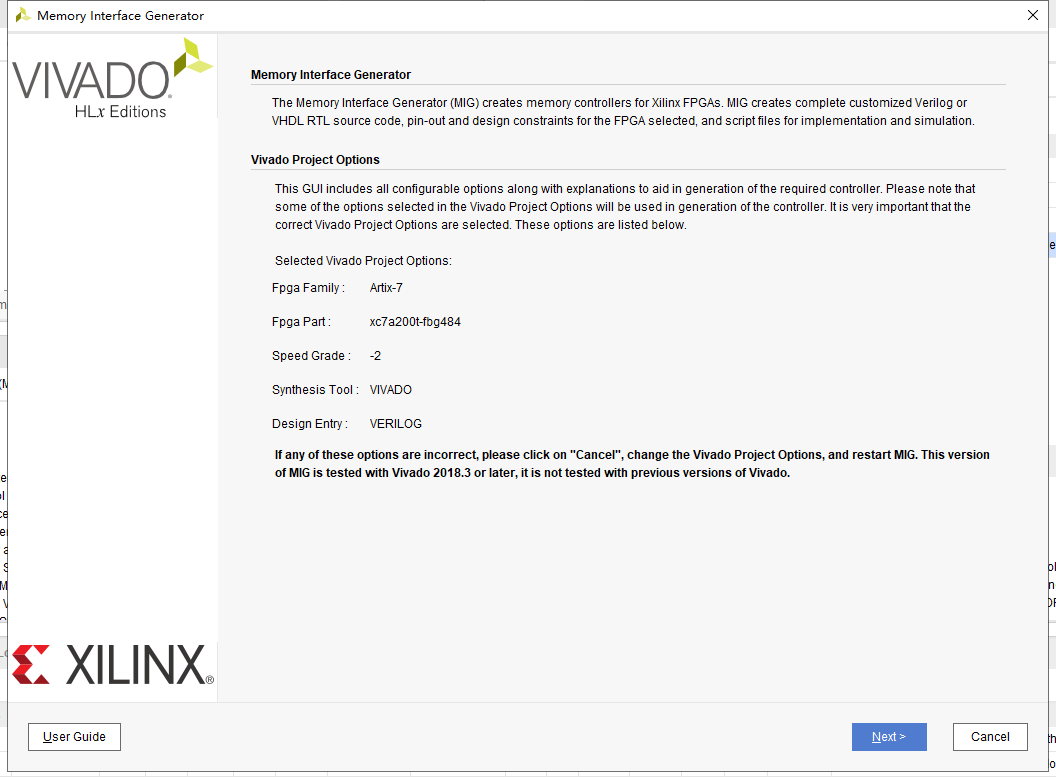

本章节主要调用官方的MIG控制器,并使用官方的MIG控制器进行仿真,开发环境vivado2020.1

鉴于很多童鞋无法仿真自己新建的DDR工程,即使使用modelsim仿真也仿真失败,本例程着重于在vivado中,对自己新建的带DDR3的工程进行仿真。

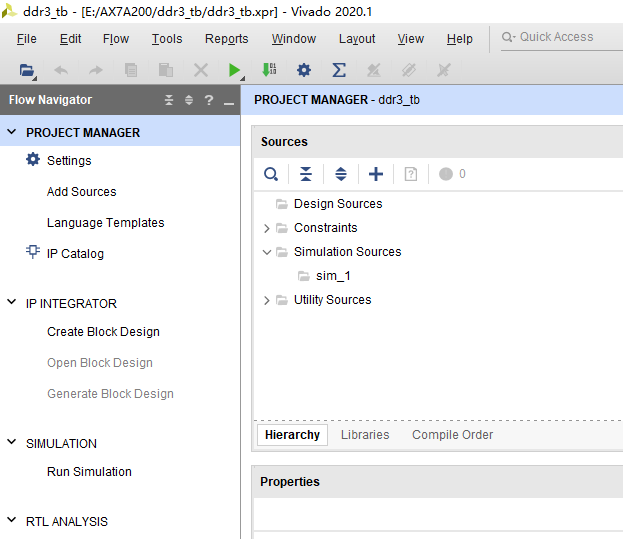

新建DDR3工程,ddr3_tb工程

调用MIG控制器

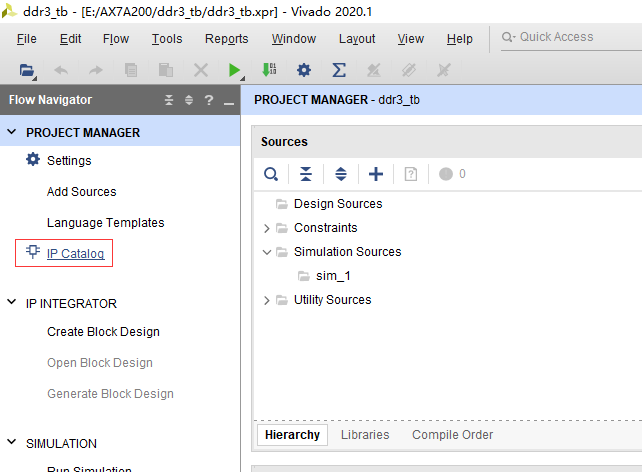

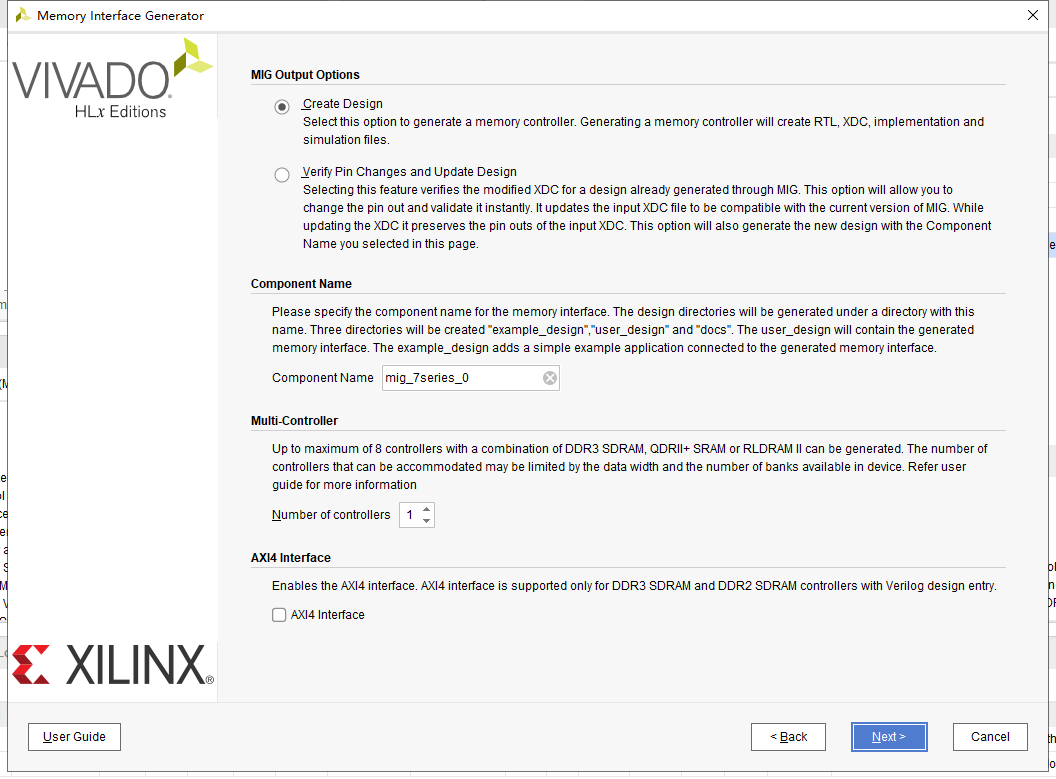

点击IP Catalog打开ip搜索栏

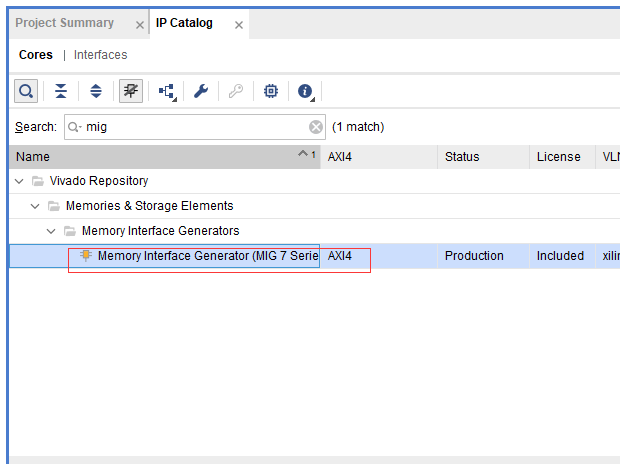

搜索栏输入mig,双击mig控制器,开始设置mig控制器

点击NEXT

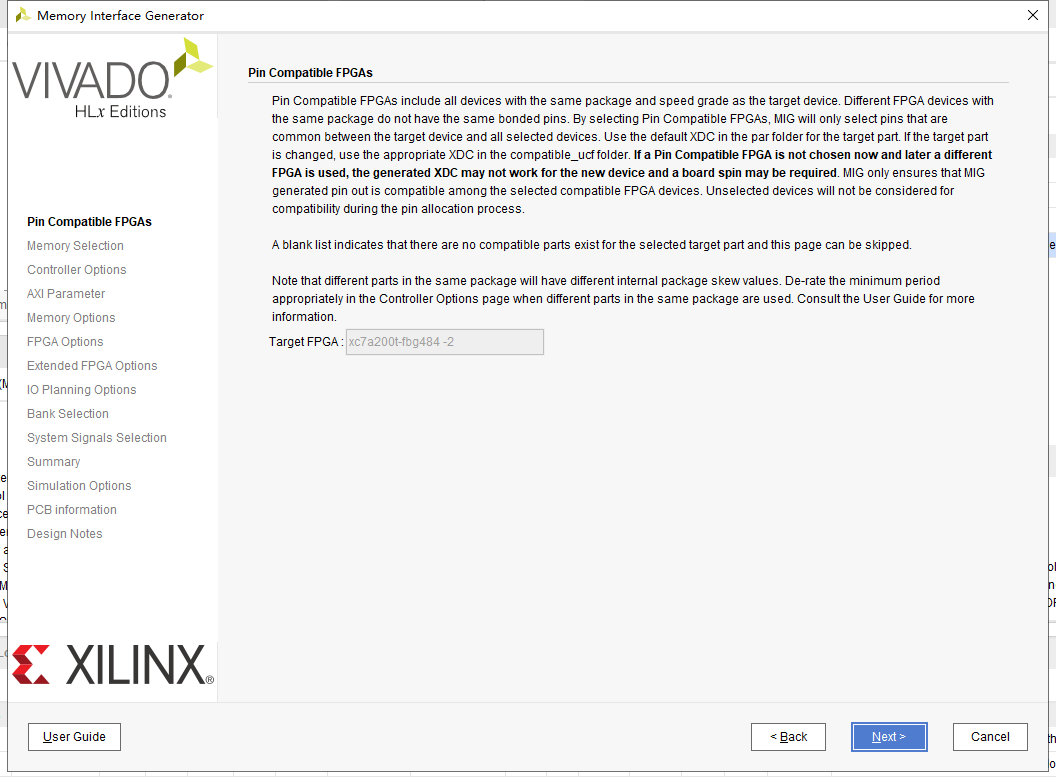

点击NEXT

点击NEXT

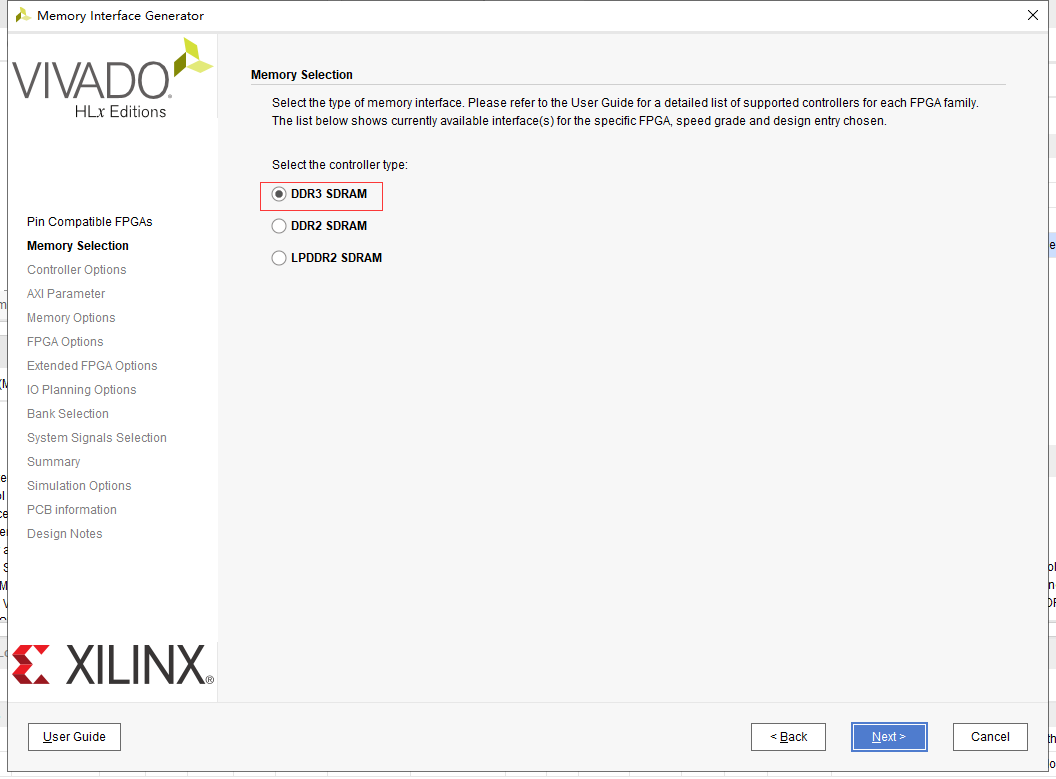

选择DDR3,点击NEXT

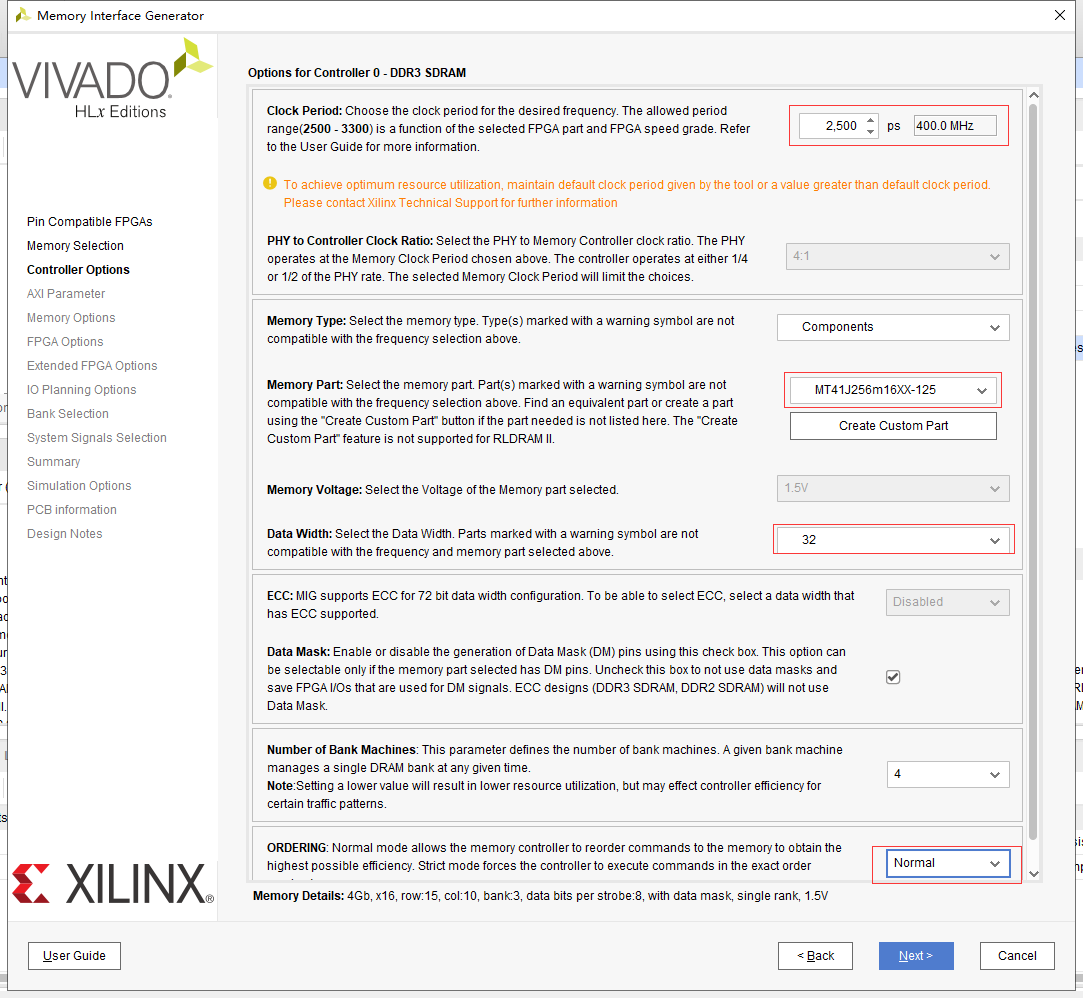

开发板上的型号"MT41J256m16xx-125", Data Width数据宽度选择32位,其它的按照截图中设置,点击NEXT

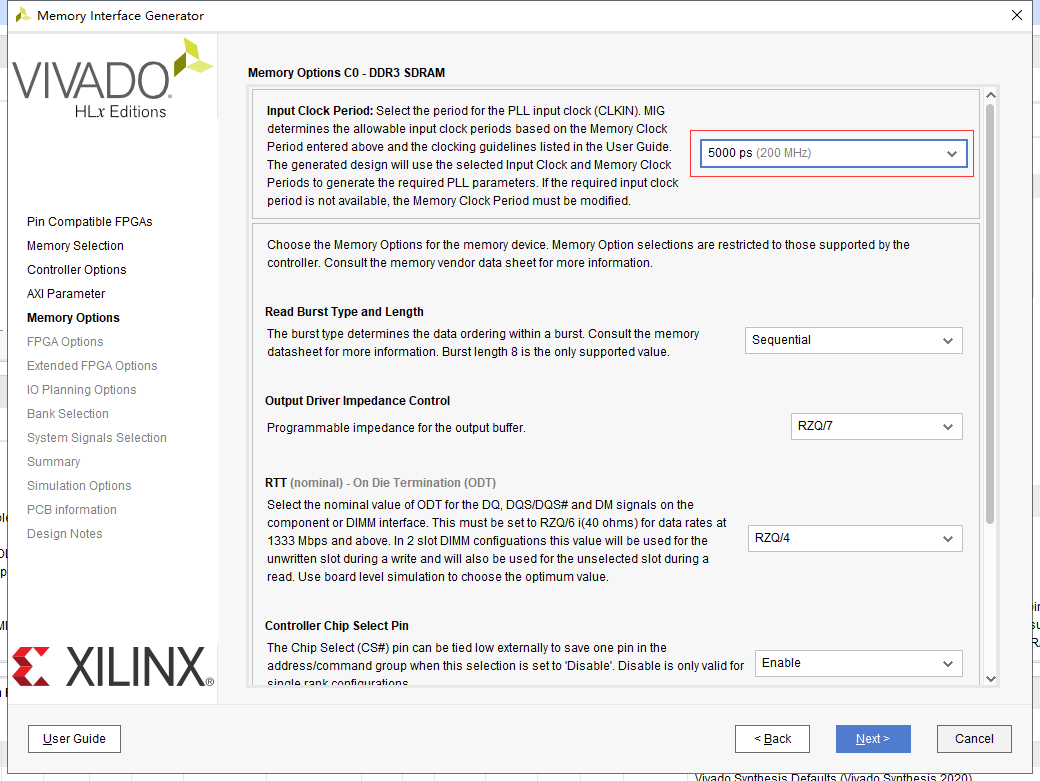

选择ddr3的外部时钟为200M,点击NEXT

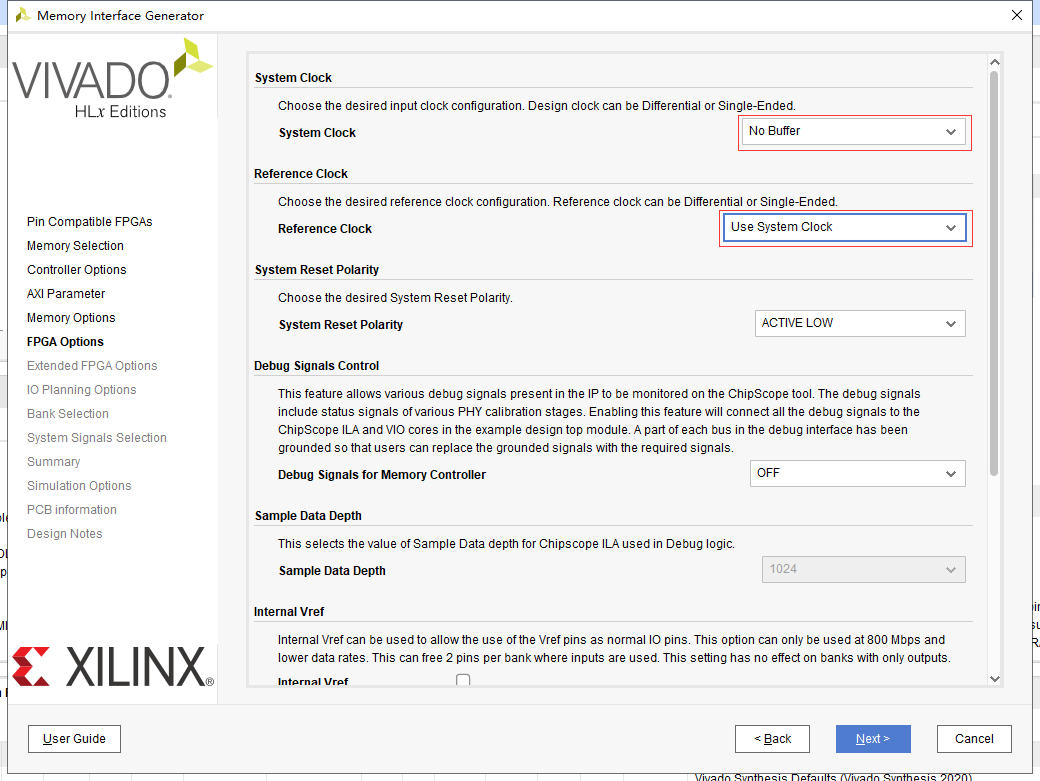

设置输入时钟的输入方式,点击NEXT

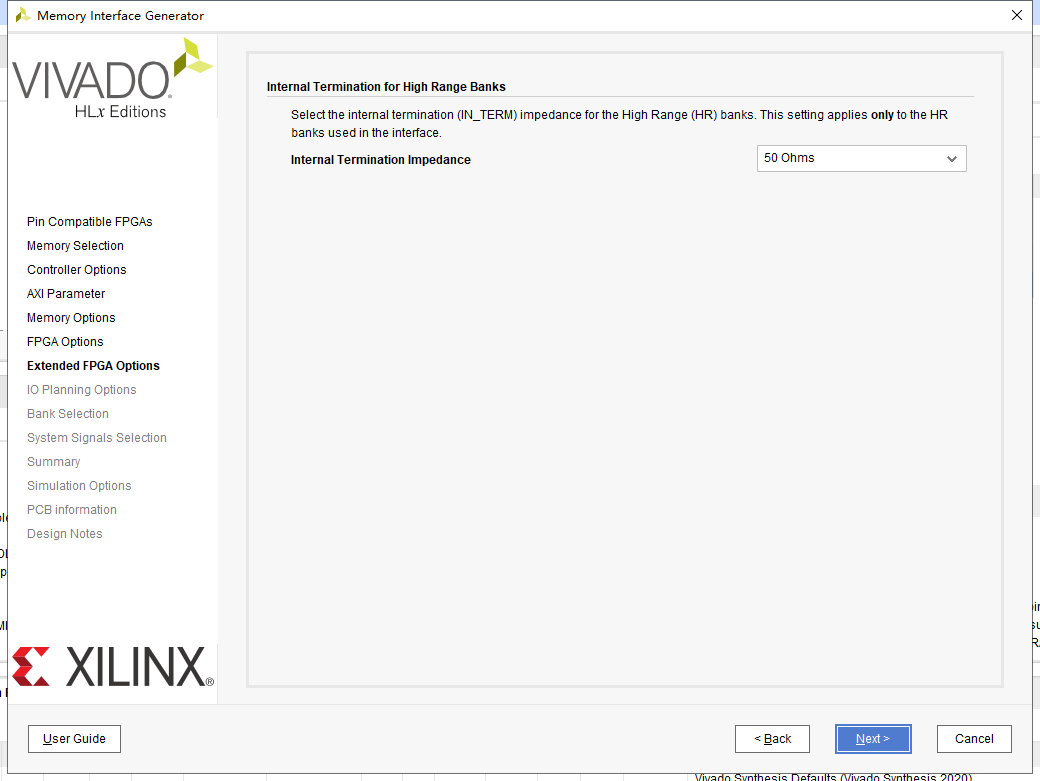

选择默认配置,点击NEXT

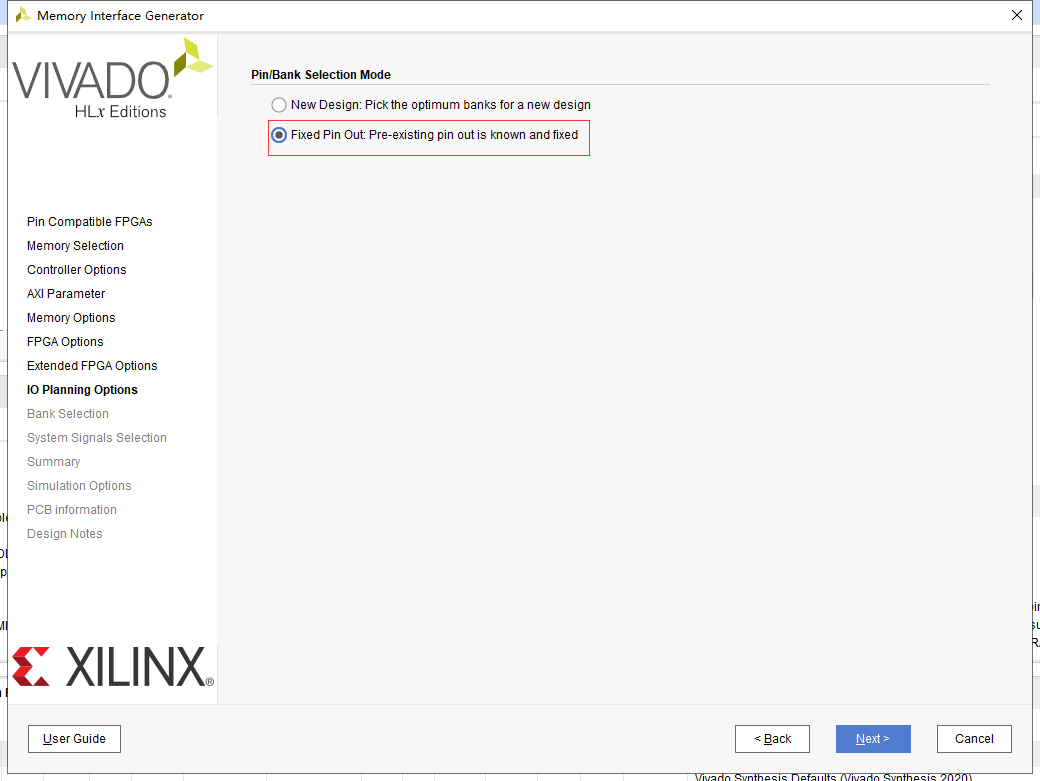

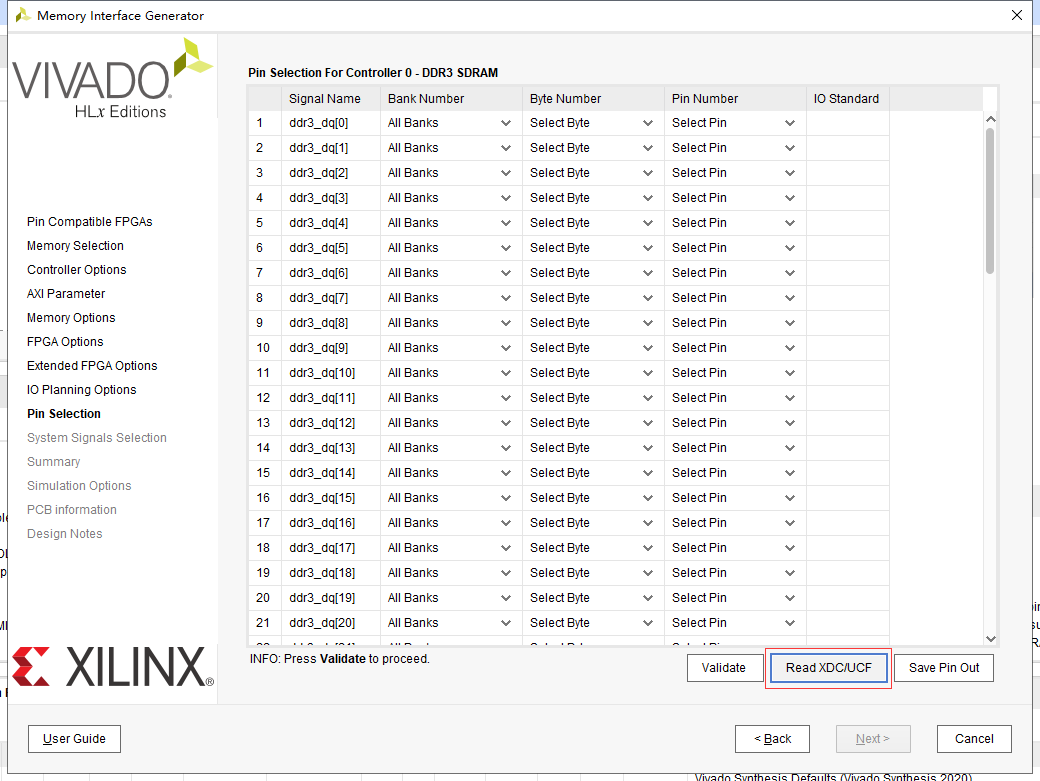

选择第二项,需要设置ddr3管脚,点击NEXT

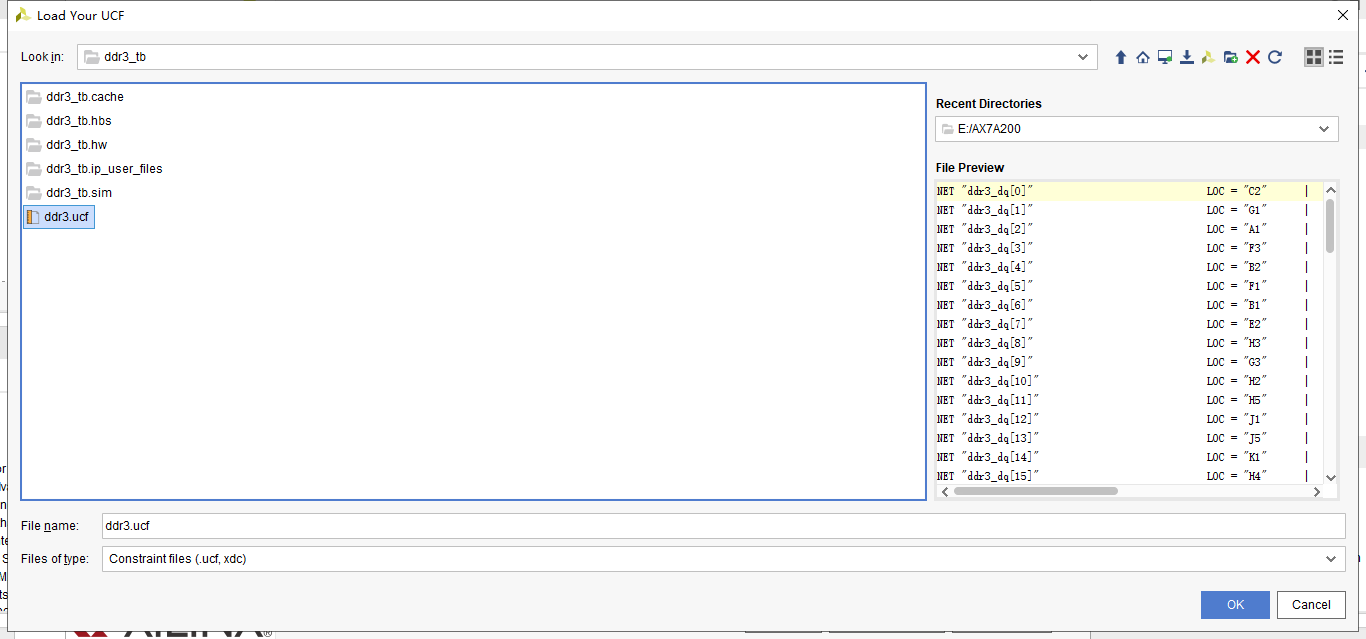

点击Read XDC/UCF,导入黑金提供的ucf文件

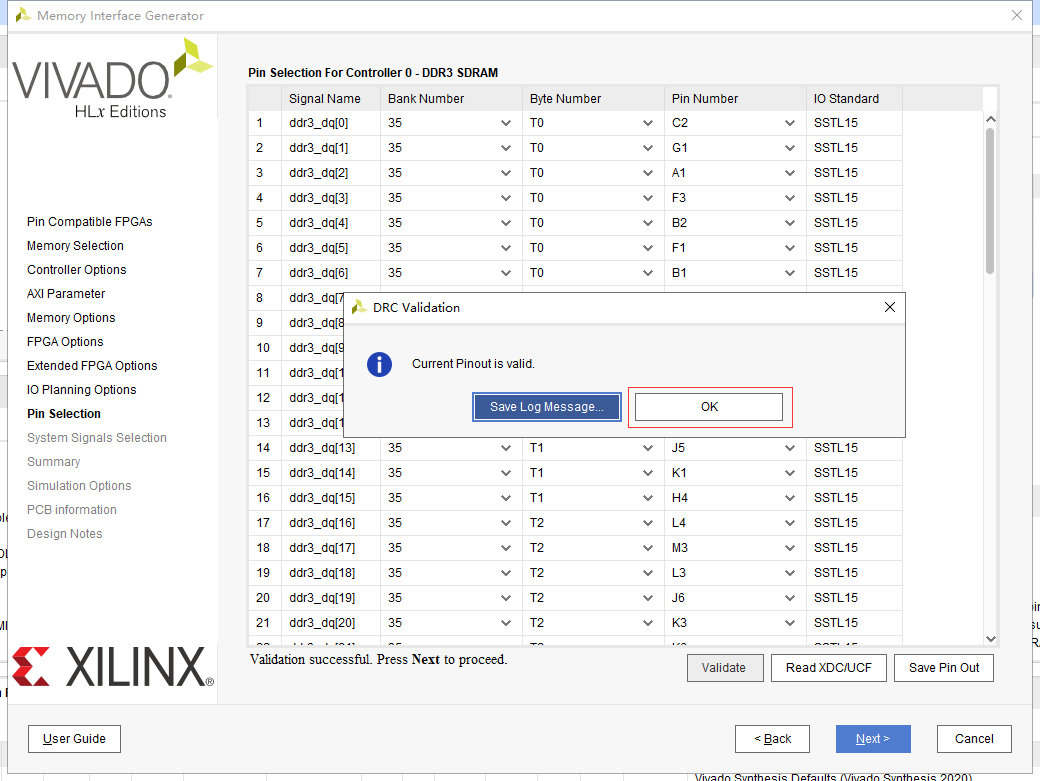

点击OK,导入ucf文件

再点击"validate" 按验证一下,通过后点击 Next

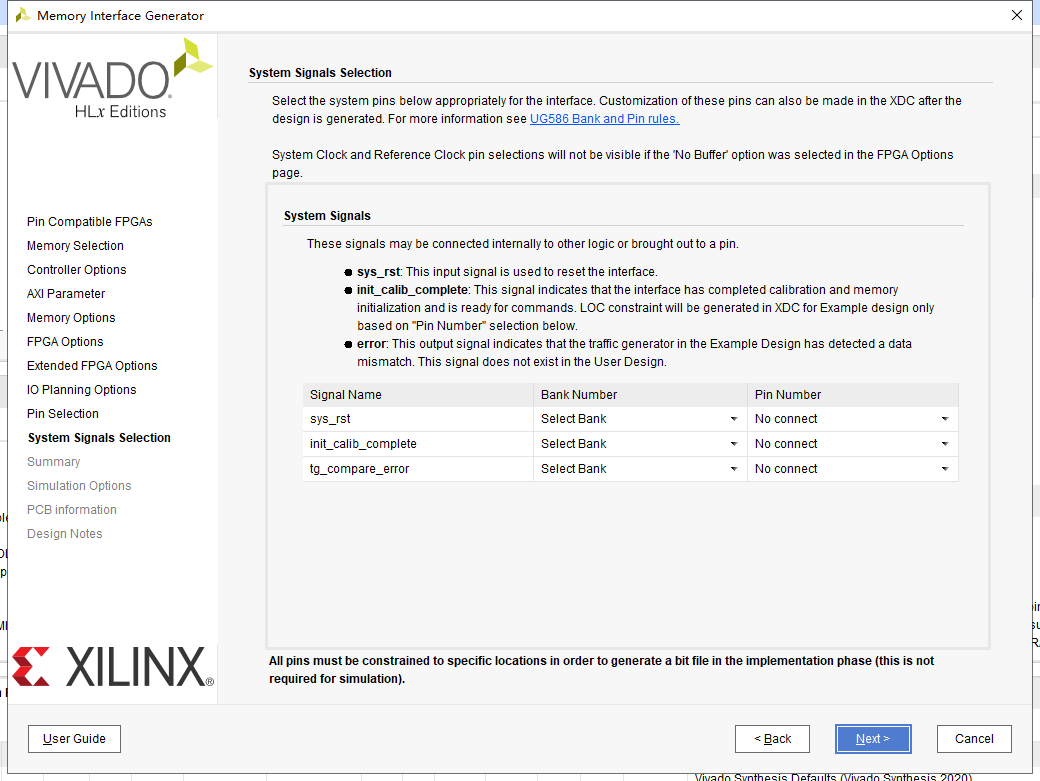

选择默认配置,点击NEXT

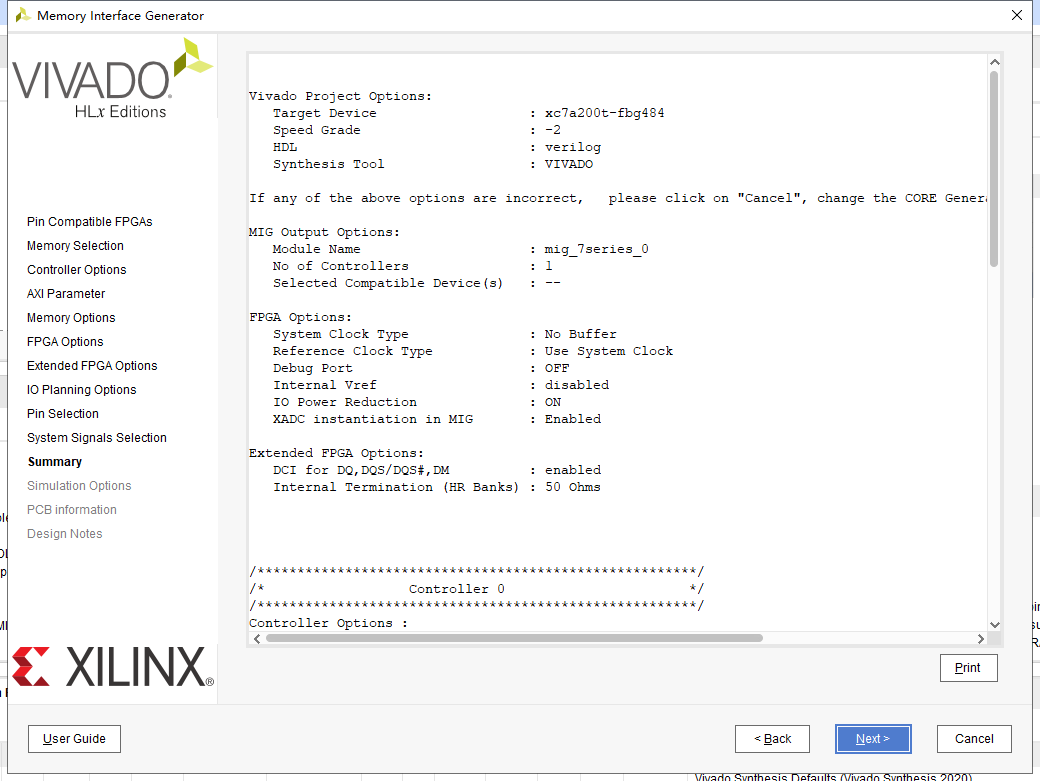

ddr3配置参数,如下图所示,点击NEXT

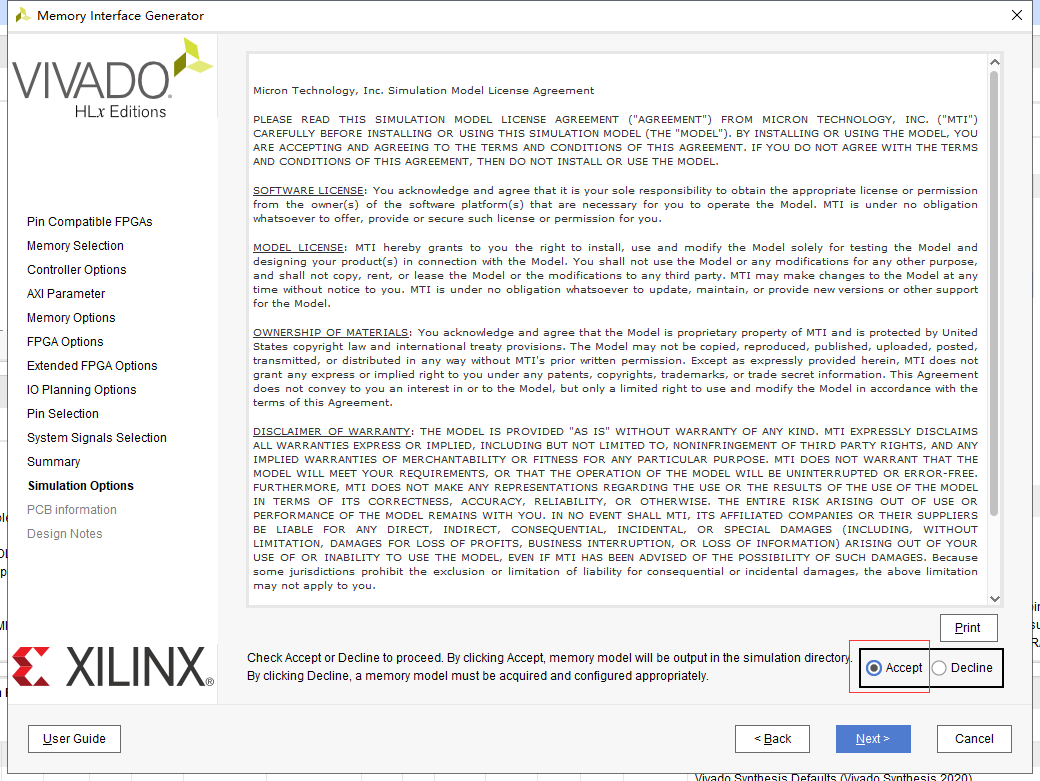

选择 Accept, 点击 Next

点击 Next

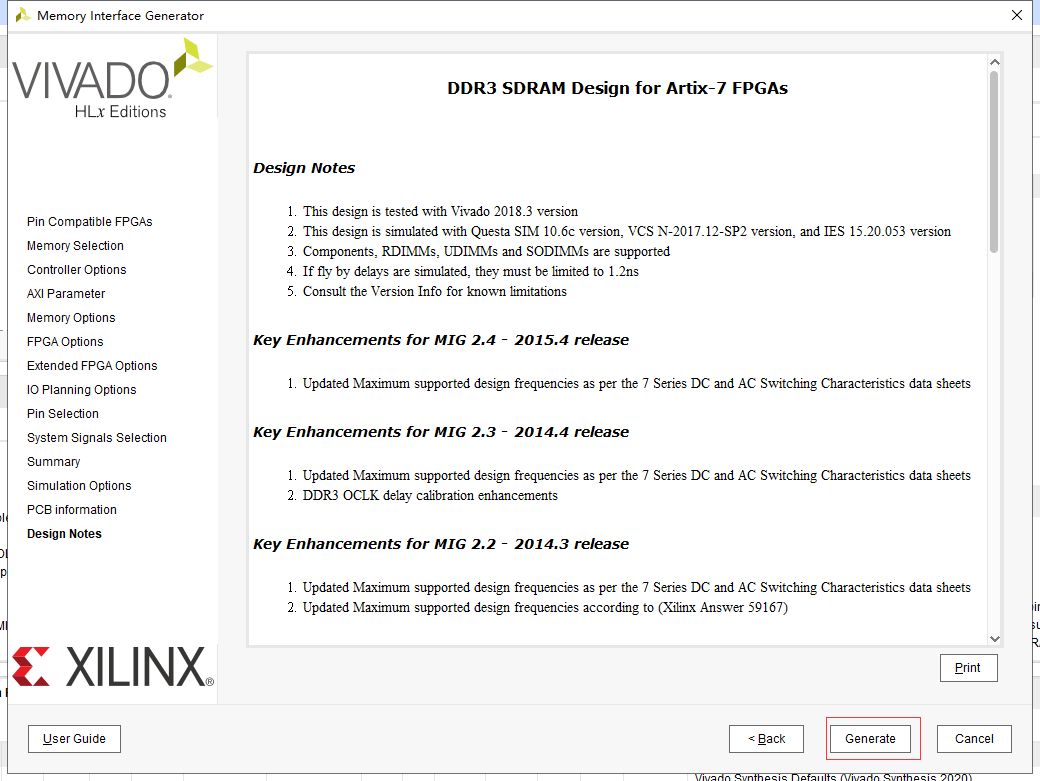

点击 Generate 按钮生成 MIG 控制器

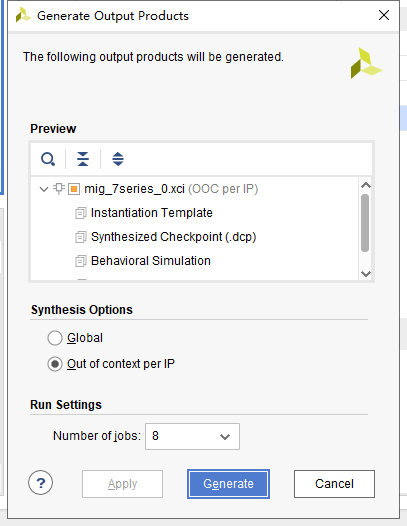

点击 Generate 按钮生成 MIG 相关的设计文件

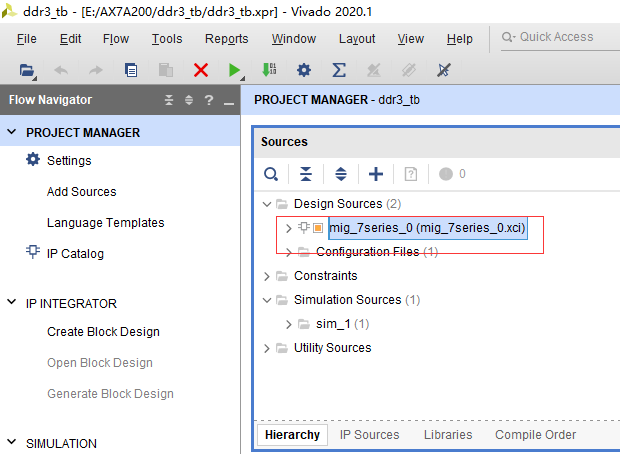

调用的mig控制器

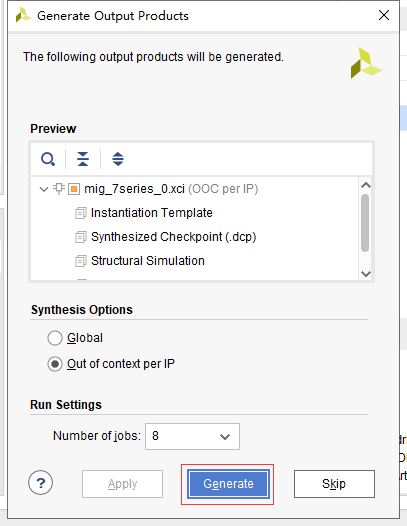

右击mig控制器,选择Generate Output Products

点击 Generate

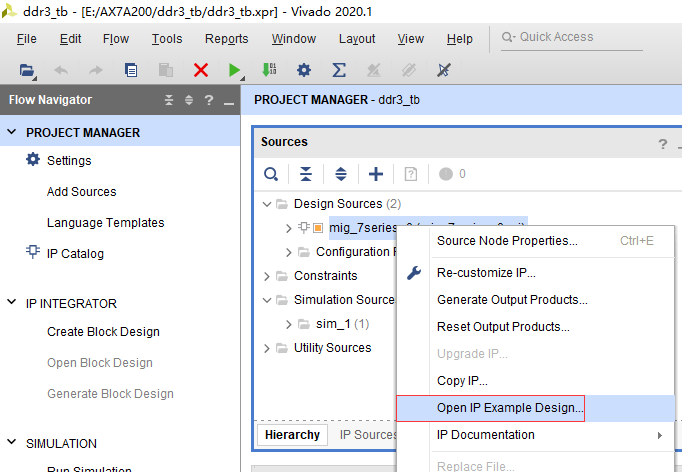

右击mig控制器选择Open IP Example Design,导出官方mig仿真文件

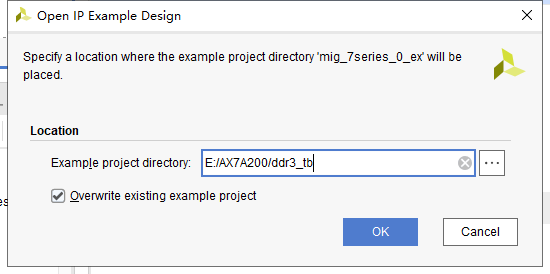

选择官方仿真文件存放位置,点击OK

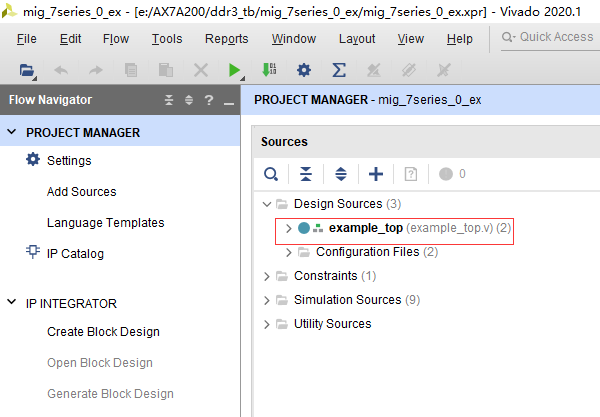

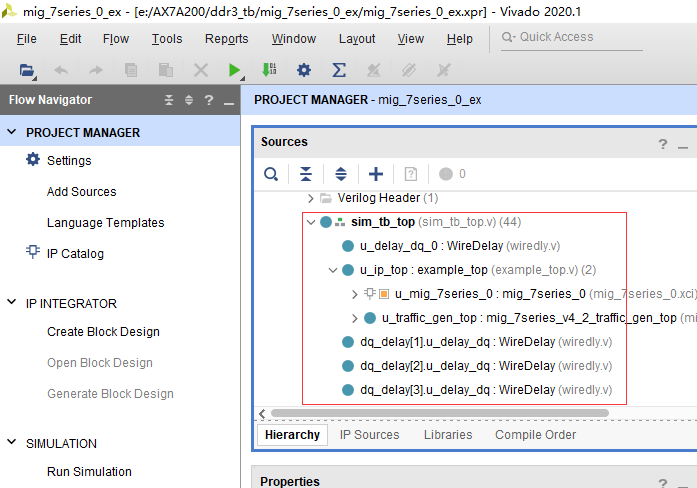

点击OK后,会自动打开官方的mig仿真工程mig_7series_0_ex

官方提供的mig仿真文件(后续如果自己建工程需要仿真ddr工程,可以使用这部分官方配置仿真,不使用modelsim进行仿真)

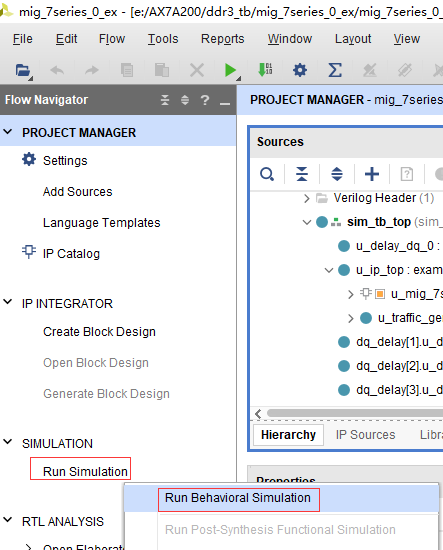

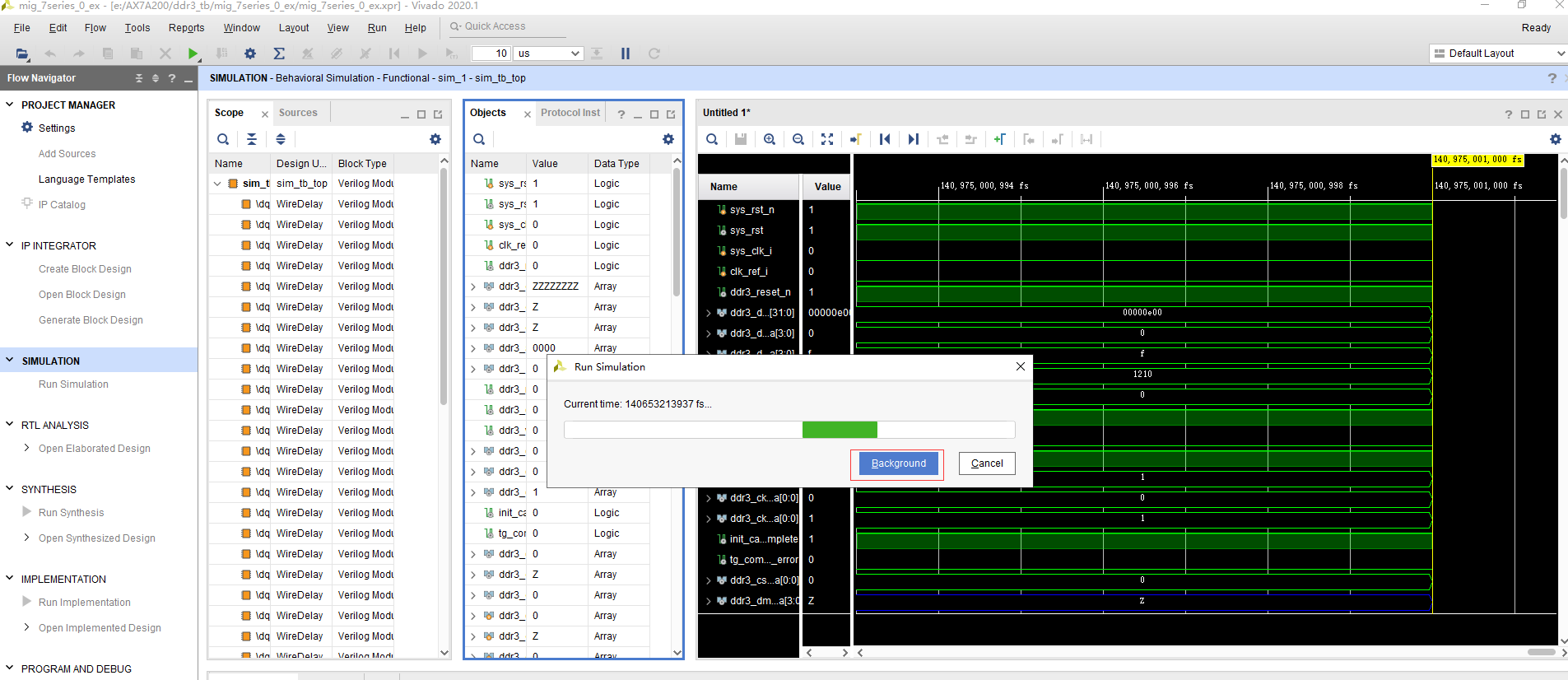

点击Run Simulation-->Run Behavioral Simulation进行仿真

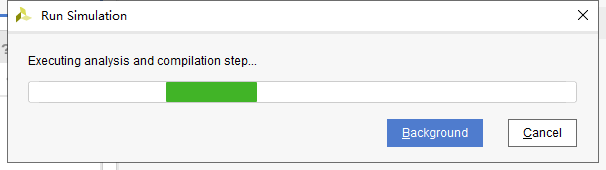

正在打开仿真环境

仿真界面如下图所示,点击Background缩小运行界面

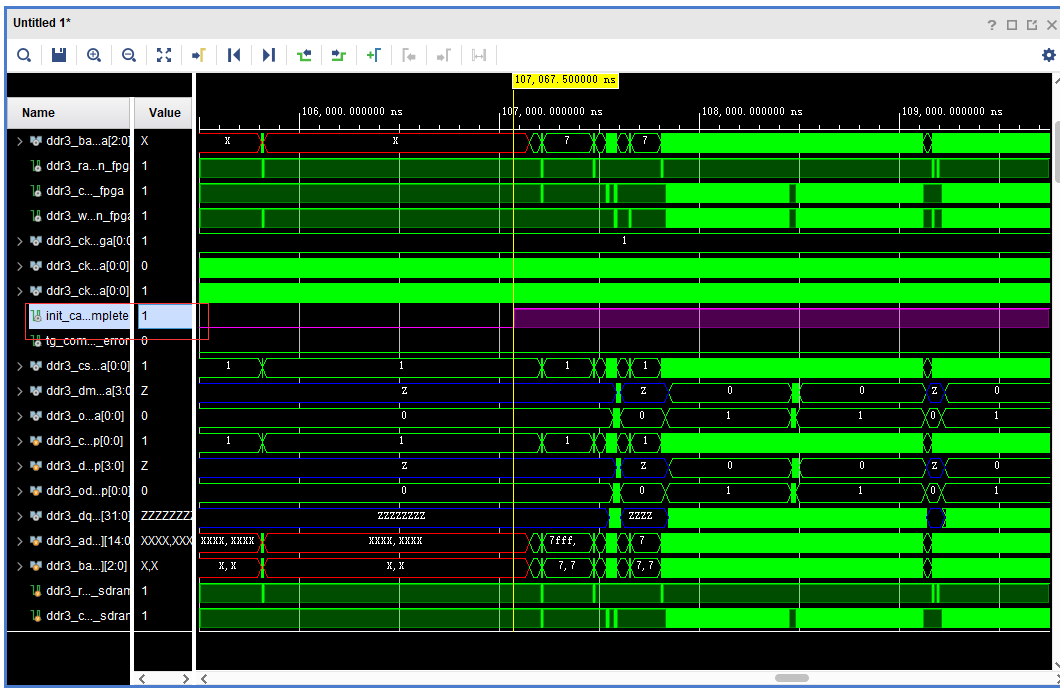

可以看到官方工程运行到107us左右init_calib_complete信号拉高,ddr3初始化成功

本章节主要是调用mig控制器,以及使用官方提供的仿真文件进行仿真,如果我们自己做的工程中使用了DDR3,可以使用官方提供的仿真文件对自己工程进行仿真,后续博客将告诉你如何对带有ddr3的工程进行仿真。

转载:

https://blog.csdn.net/taowei1314520/article/details/128741970?spm=1001.2014.3001.5501