热门标签

热门文章

- 1Python基于Flask的高校舆情分析,舆情监控可视化系统_舆情分析python

- 2ESXI中设置高格作为旁路由并设置双机热备(VRRP)_高恪旁路由

- 3github有趣项目:Verilog在线仿真( DigitalJS+edaplayground)_免费verilog仿真

- 4用C++实现BM3D图像降噪算法_bm3d opencv

- 5Android Monkey的使用

- 6腾讯云最新社招面经出炉(面试原题+答案解析)_腾讯云面试

- 7Pytorch的学习

- 8Maven:排除依赖_maven忽略依赖包

- 9将Mac OS Lion 加入Windows 域

- 10vue项目采用sonarqube扫描代码_sonarqube扫描vue配置sonar-project.properties

当前位置: article > 正文

使用xc7a100tfgg484-2去正点原子的IP核之PLL实验_xc7a100tfgg484-2示波器

作者:Gausst松鼠会 | 2024-06-03 10:34:39

赞

踩

xc7a100tfgg484-2示波器

目前正在学习FPGA,用的是Xinlinx 黑金板子,结合正点原子例程和黑金的例程去学习,而黑金却没有该IP核之PLL实验,于是根据正点原子的例程进行学习。

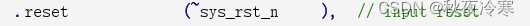

根据正点原子的文档,写了程序,但是仿真的结果却无法实现,其sys_rst_n和sys_clk一直显示高阻态,最后查找发现是下方图片忘记取反了

还有查找的时候,发现了这个篇好文章,结合正点原子的记录一下

https://blog.csdn.net/yishuihanq/article/details/130760772

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/666850

推荐阅读

- php项目系统 ...

赞

踩

相关标签