- 1从小红书app开启逆向之旅(1)_小红书app逆向

- 2微信小程序刷新页面数据_wx.getstorage获取的数据还在动态变化怎么办

- 3unity退出游戏_unity退出 游戏到初始界面

- 4python高校舆情分析系统+可视化+情感分析 舆情分析+Flask框架(源码+文档)✅_文本情感分析系统可视化

- 5教你如何提高双目立体视觉系统的精度

- 6vs code无法登陆git_git的相关操作

- 7【机器学习】机器学习:人工智能中实现自动化决策与精细优化的核心驱动力_集成优化目标的核心决策驱动力点?

- 8Unity3D性能优化 (五)——UI

- 9电话机器人 模拟人工打电话

- 10Rust TCP扫描器_rust 检查端口开启

MATLAB/simulink HDLCoder生成DDS quartus项目_simulink hdl coder

赞

踩

前言

为了提升FPGA学习过程的生活品质,在此记录一下使用simulink搭建模型以后直接使用HDL Coder生成Quartus 项目的过程。

一、什么是HDL Coder

HDL Coder 通过从 MATLAB 函数、Simulink 模型和 Stateflow 图中生成可移植、可综合的 Verilog® 和 VHDL® 代码来支持 FPGA、SoC 和 ASIC 的高层设计。您可以将生成的 HDL 代码用于 FPGA 编程、ASIC 原型构建和产品级设计。

HDL Coder 包括工作流顾问,可用于在 Xilinx®、Intel® 和 Microchip 板上通过生成的代码自动进行原型构建,并为 ASIC 和 FPGA 工作流生成 IP 核。您可以以速度和面积为目的进行优化,突出显示关键路径,并在综合之前生成资源利用率估计值。HDL Coder 提供 Simulink 模型与生成的 Verilog 和 VHDL 代码之间的可追溯性,因此支持对遵循 DO-254 及其他标准的高完整性应用进行代码验证。

二、使用步骤

选择带有HDL的库中的模块,HDL库中的模块在generate时才能生成代码

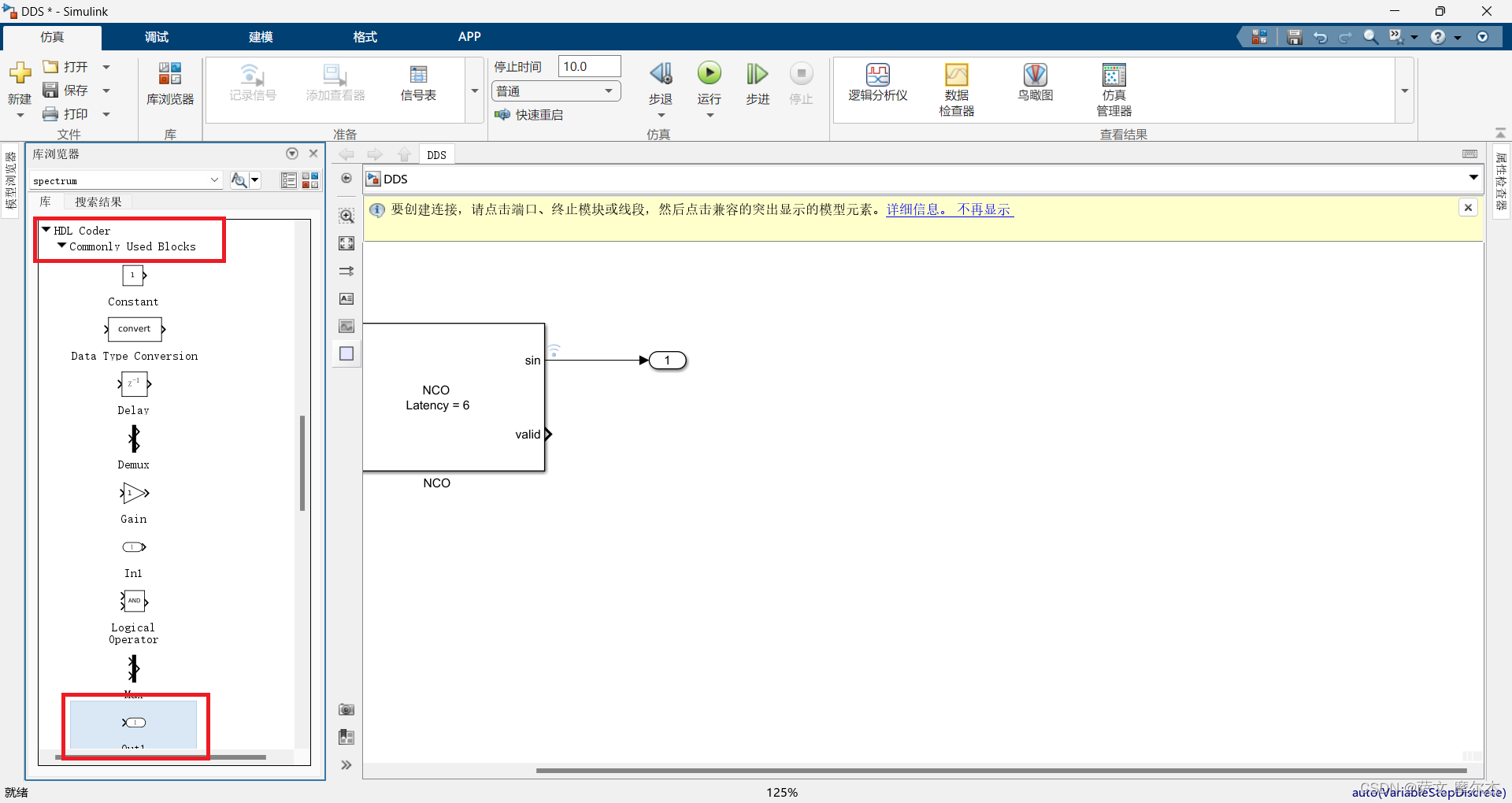

1.搭建simulink模型

-

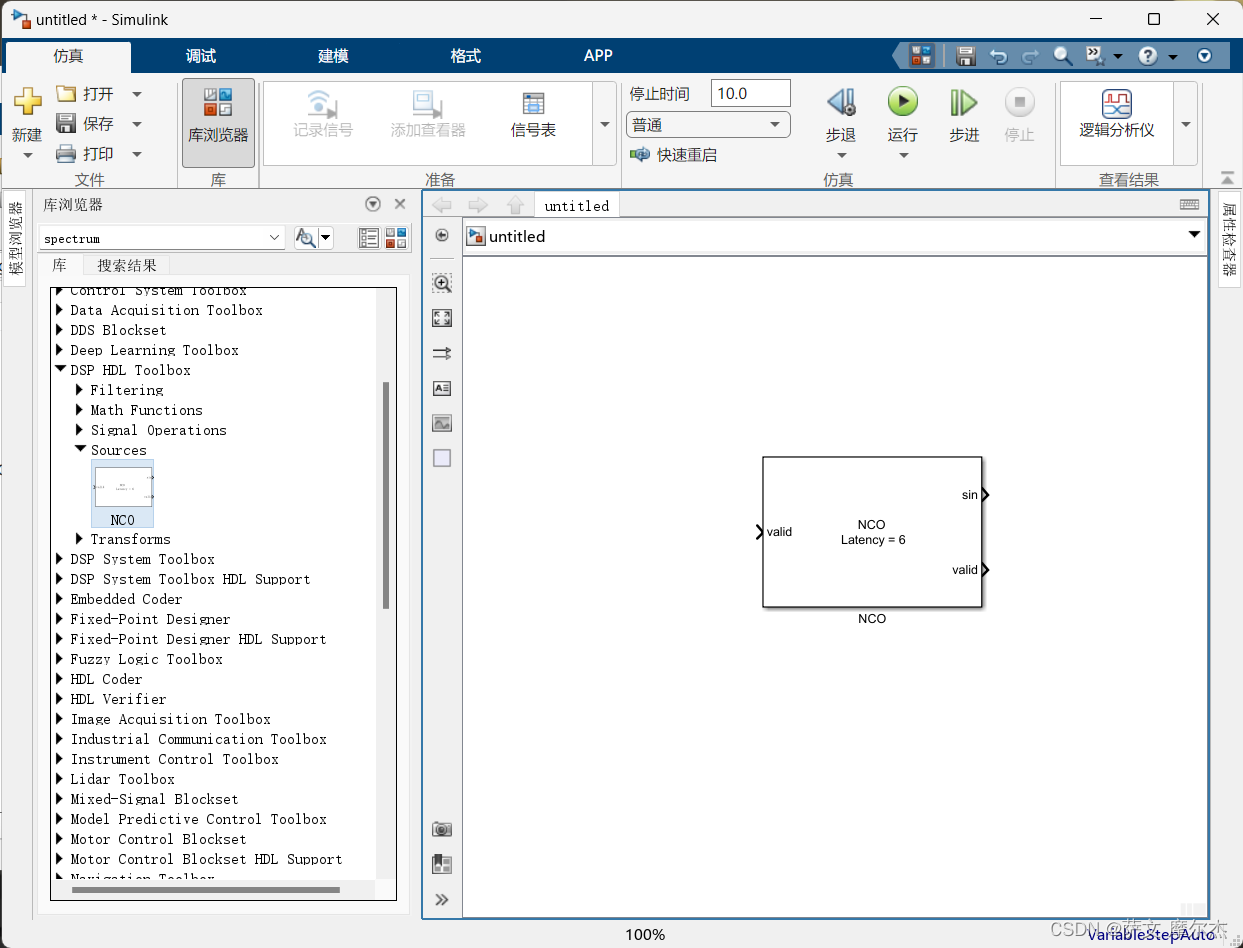

在DSP HDL Toolbox中找到NCO模块

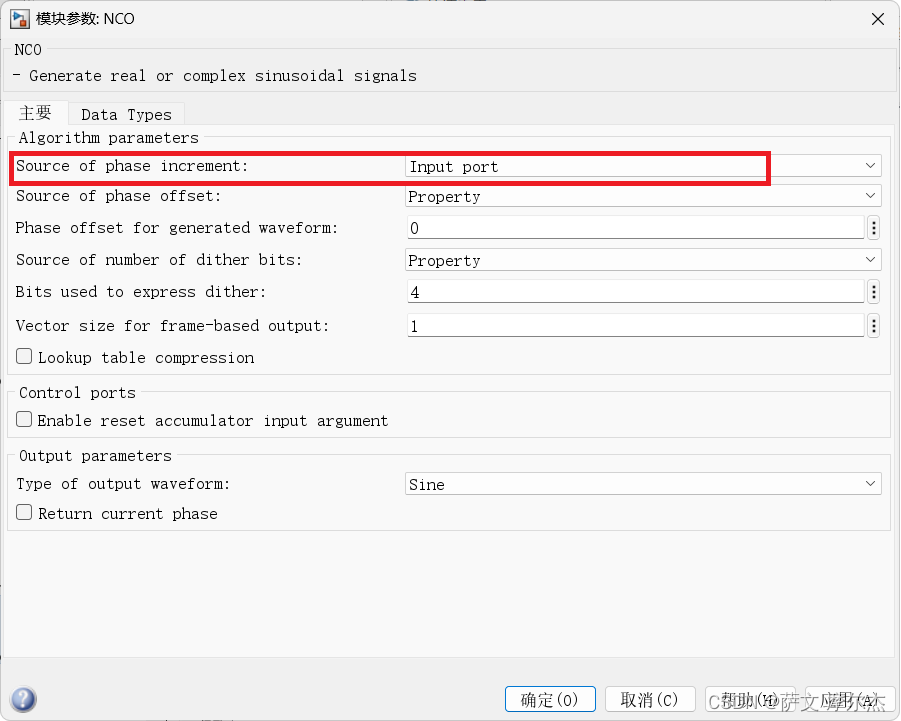

将NCO中phase increment设置为 Input port

-

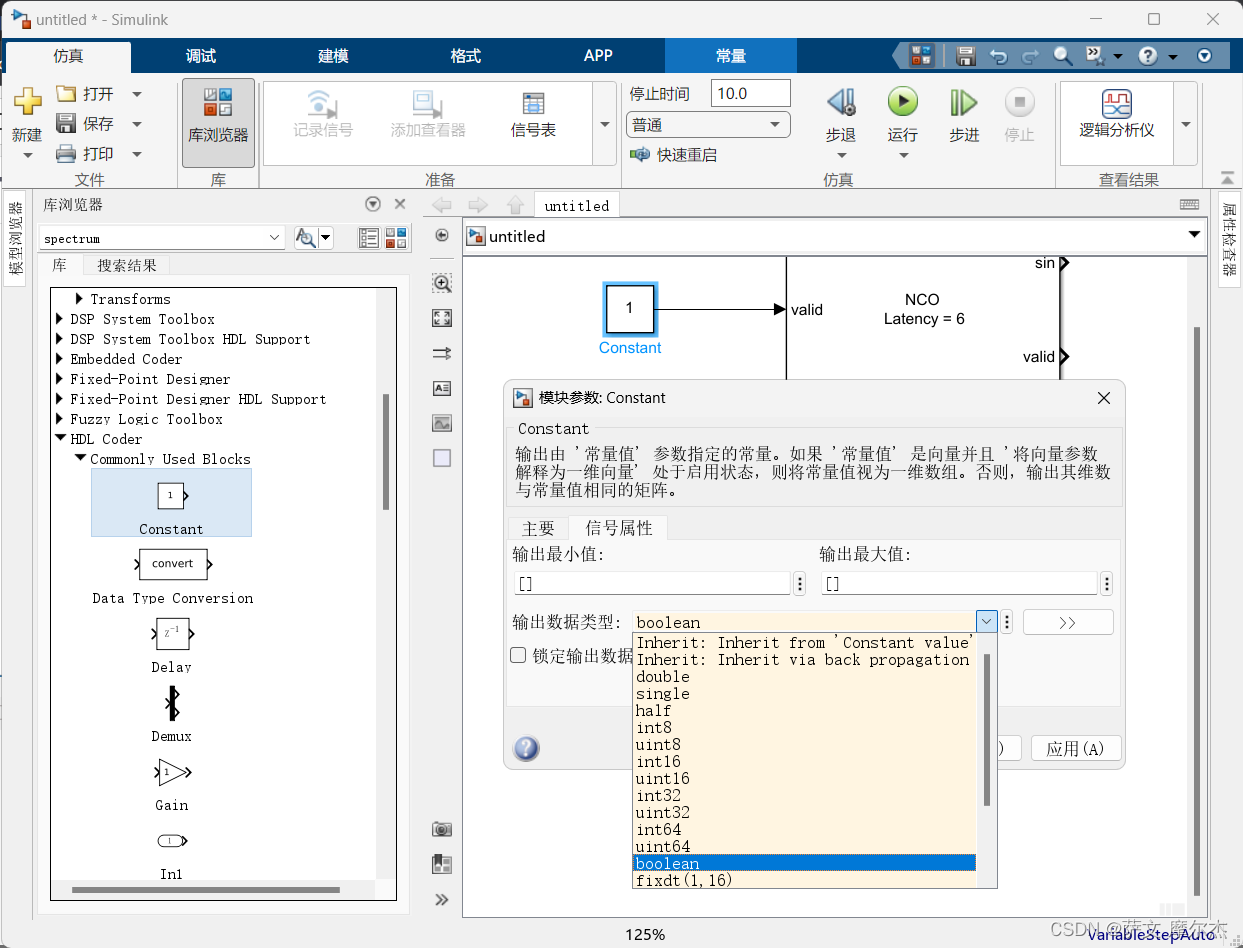

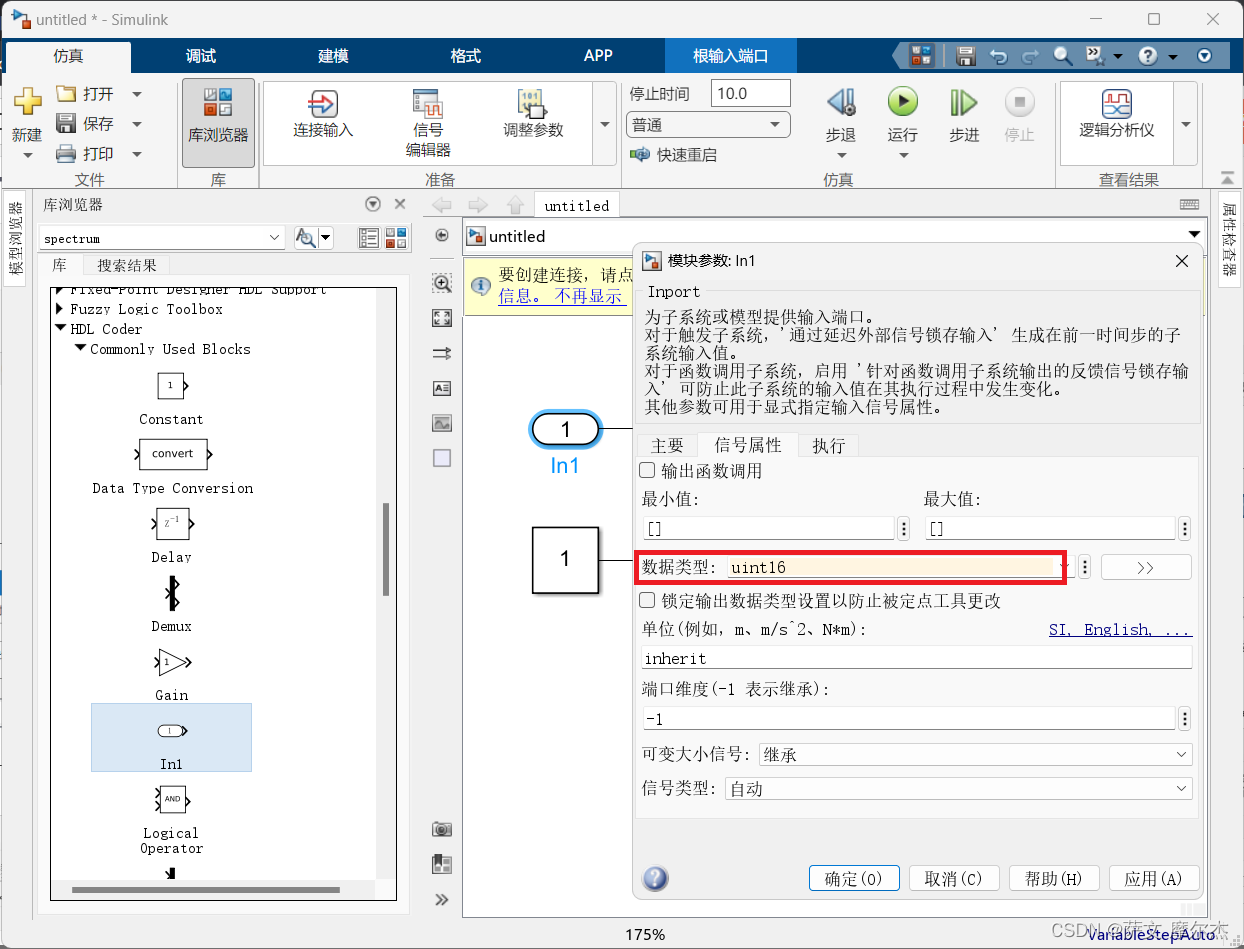

valid端放置constant模块,数据类型设置为Boolean;inc端放置in模块,数据类型设置为uint16

采样时间设置为1,采样率为1Hz,便于计算。

3.添加输出端口

此时基本模型已经搭建完成

此时基本模型已经搭建完成

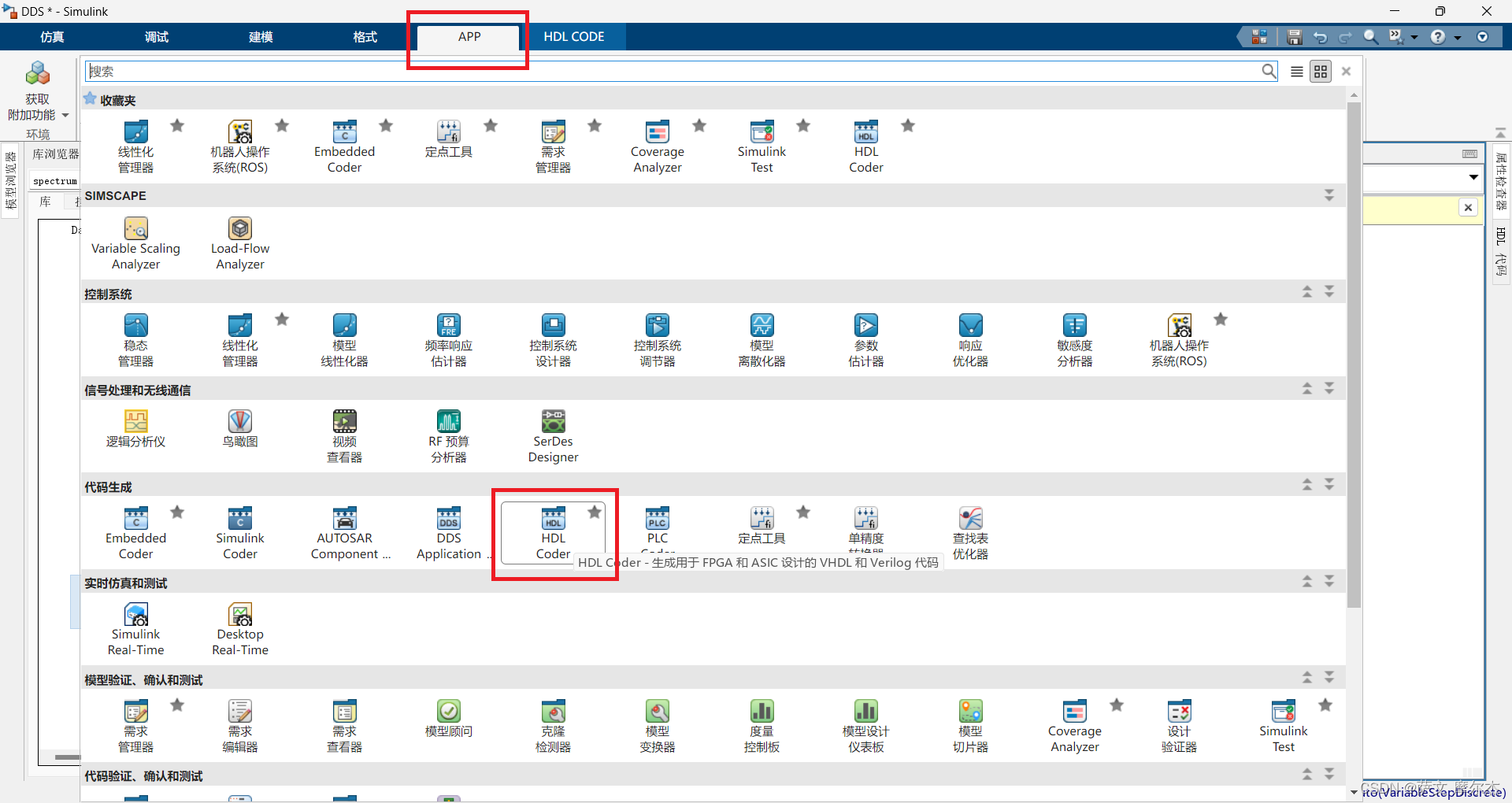

2.HDL Coder使用

- 在任务栏的APP中选择HDL Coder

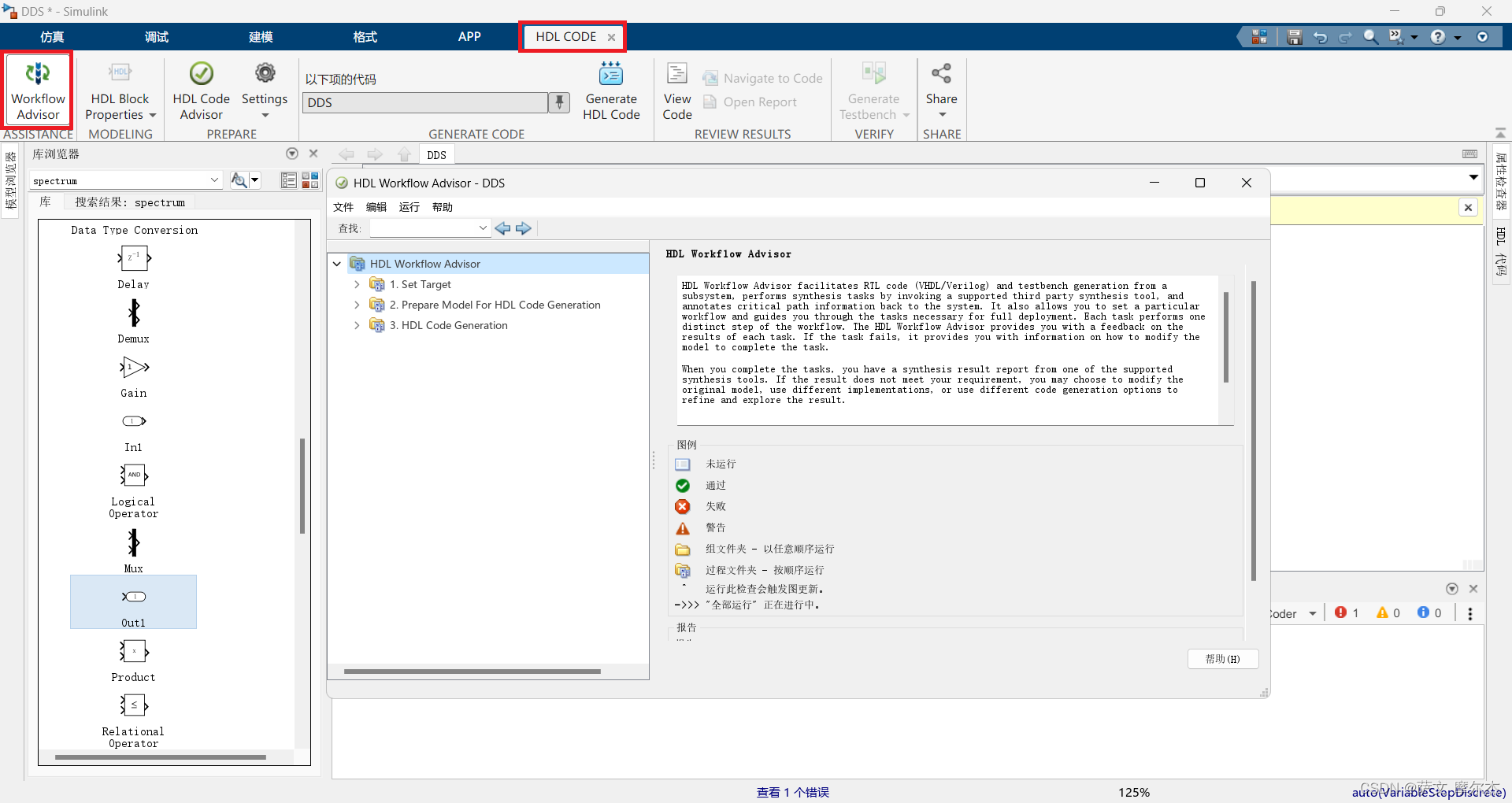

- 点击workflow

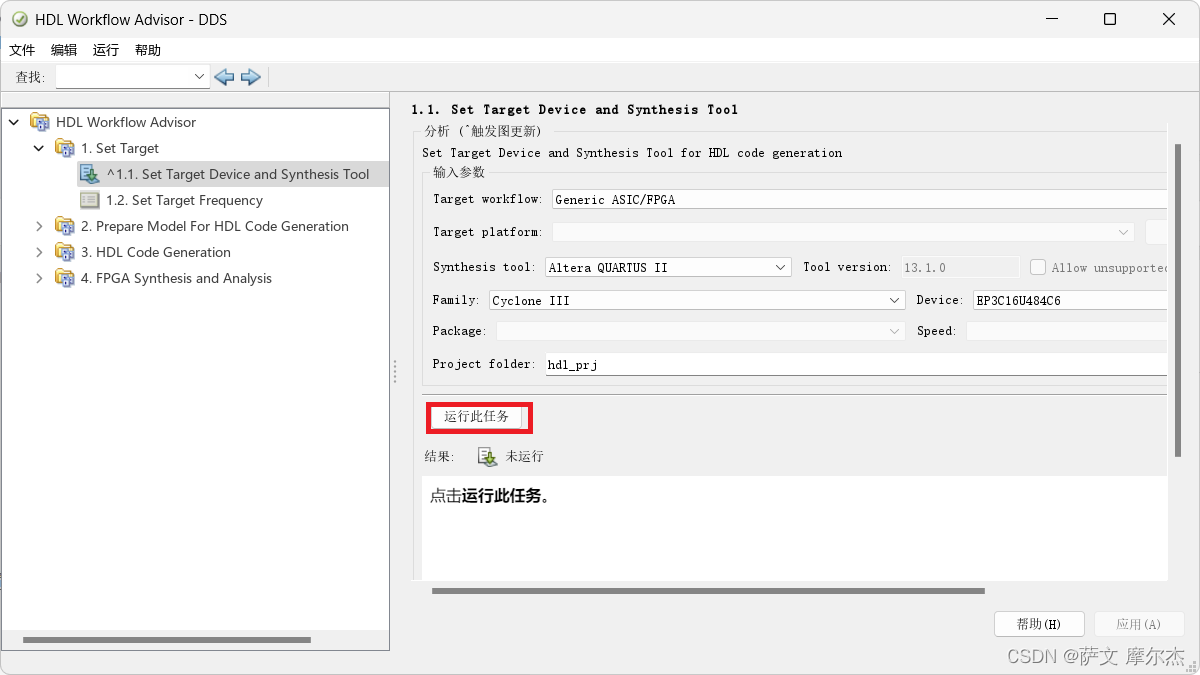

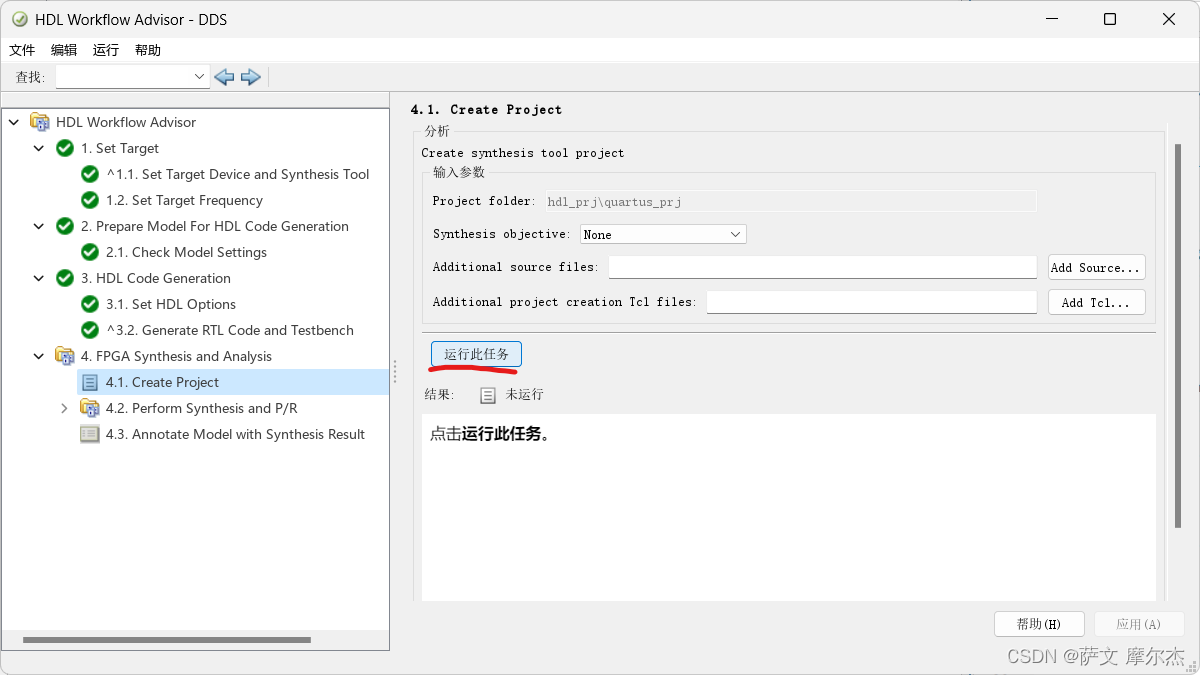

- 选择Target workflow为图上所示选项,选择编译器和FPGA的型号后点击运行此任务,

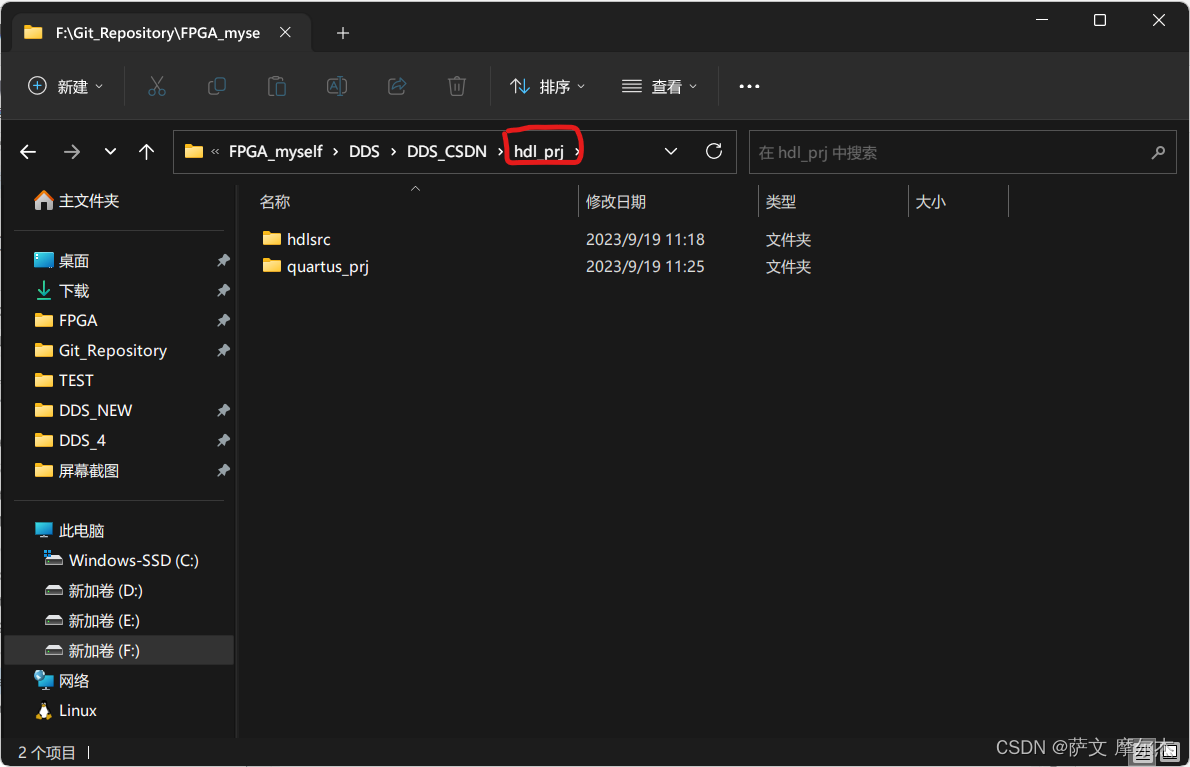

运行以后就会在slx保存目录下新建一个hdl_prj文件夹保存生成的文件

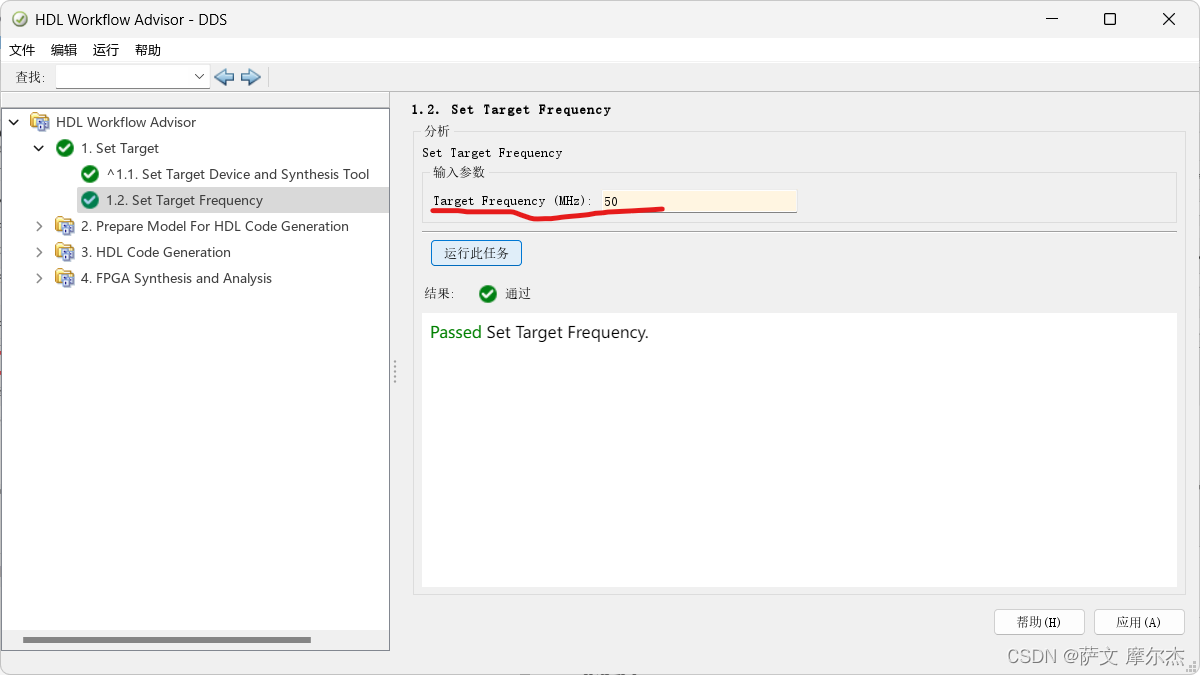

将Target Frequency设置为FPGA工作频率

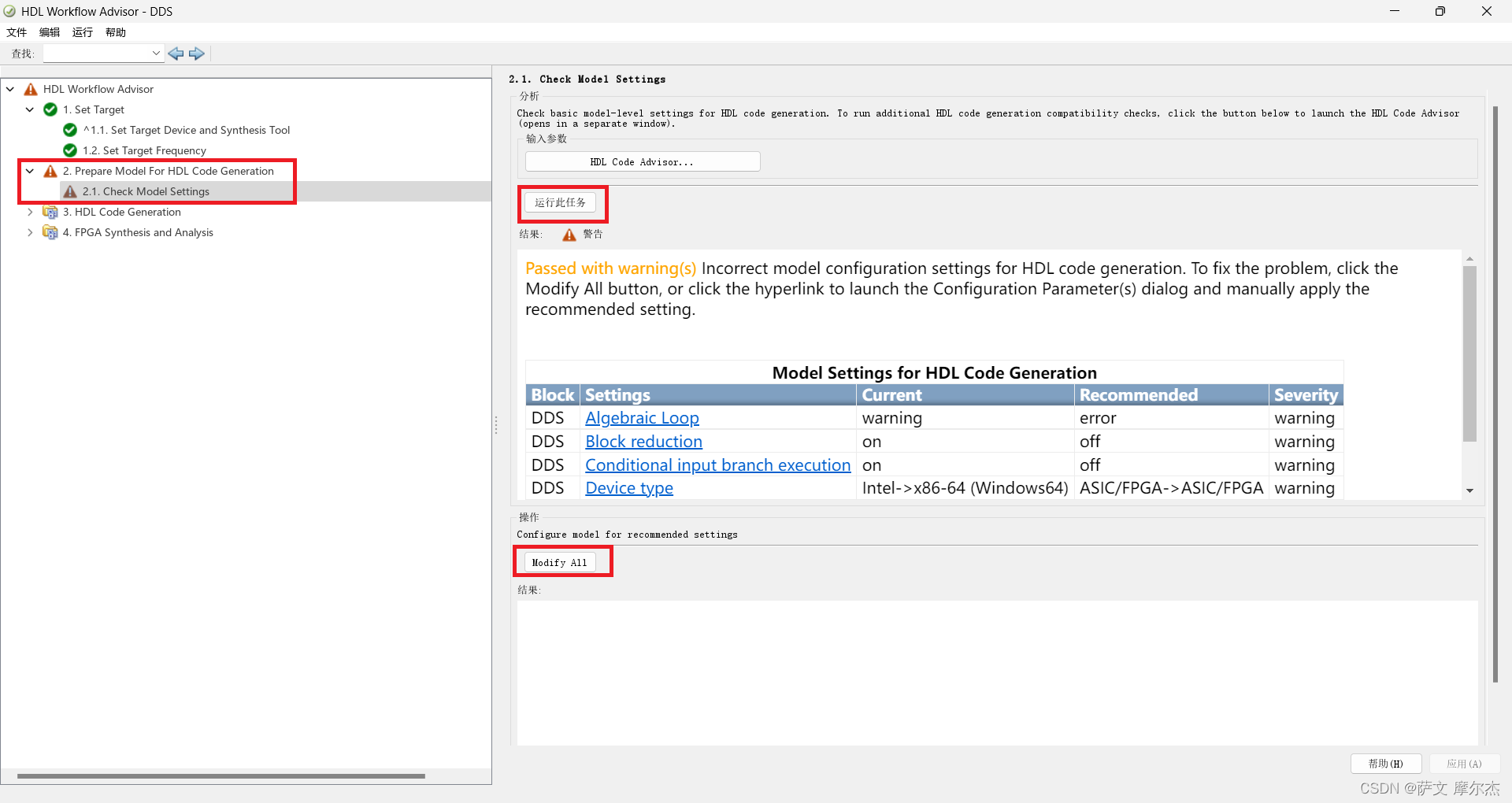

- 该部分点击运行后大概率会有一个warning,只需点击下面的Modify All后再次运行即可

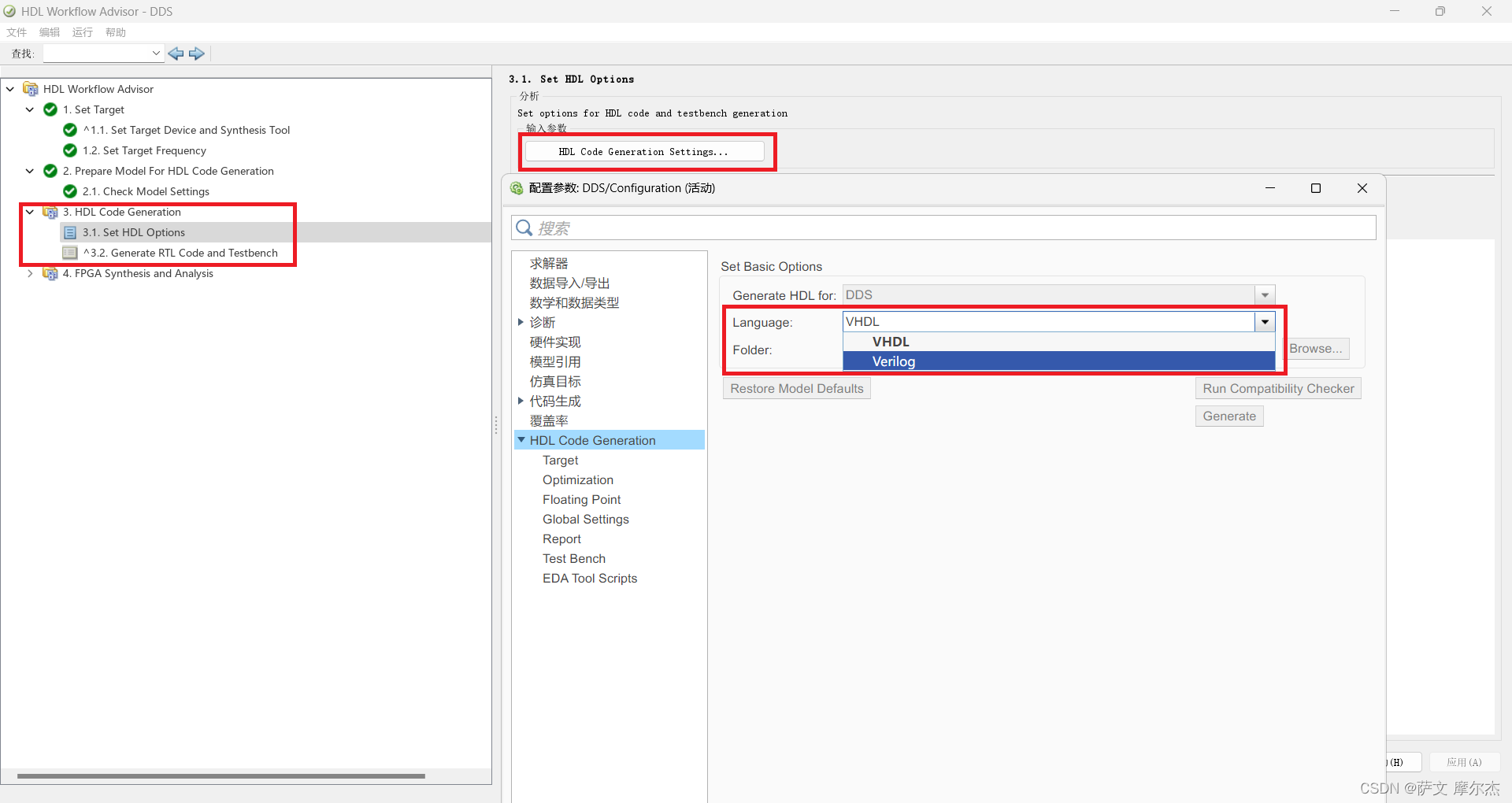

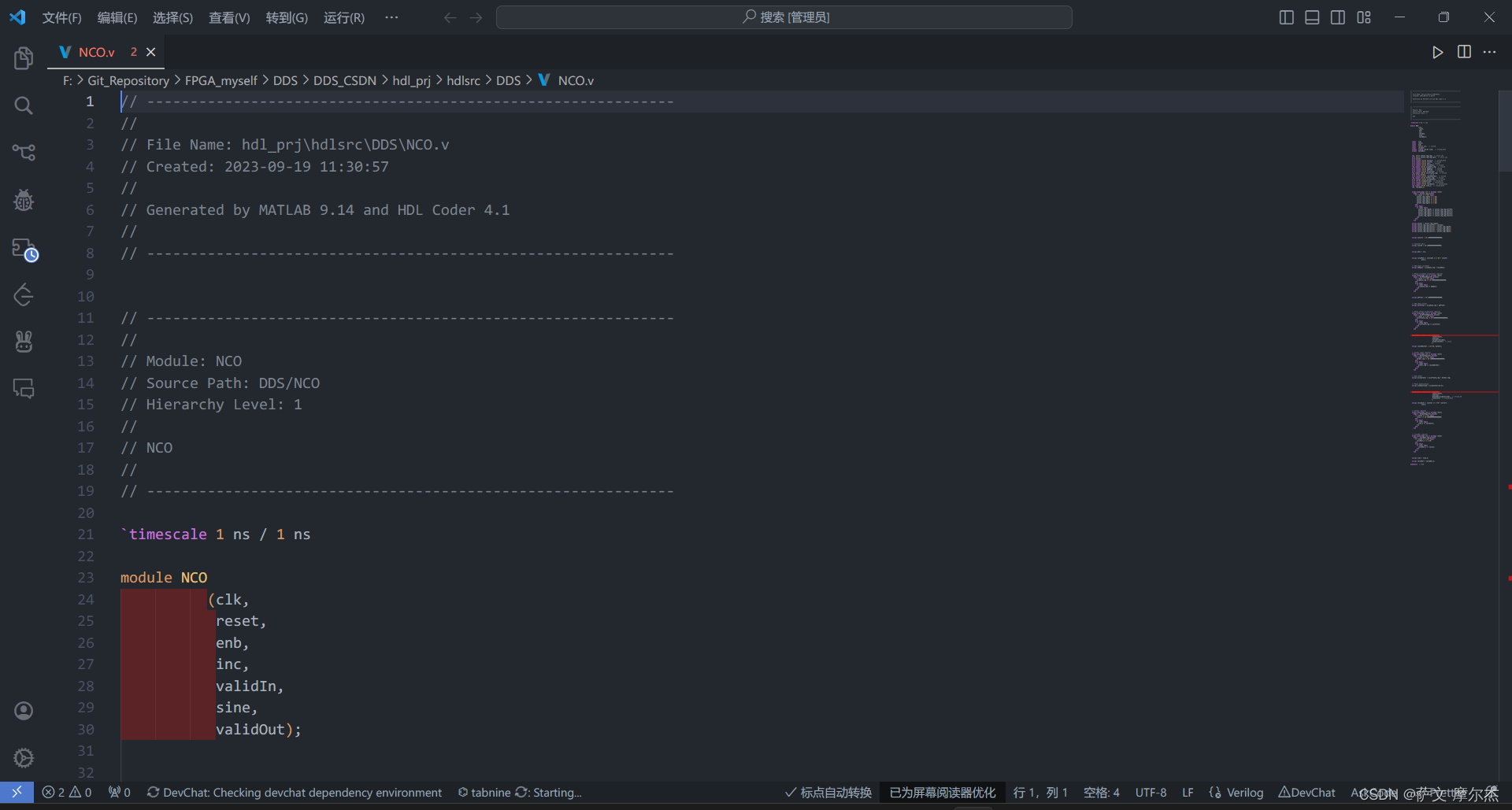

- 选择目标语言为Verilog语言后点击运行

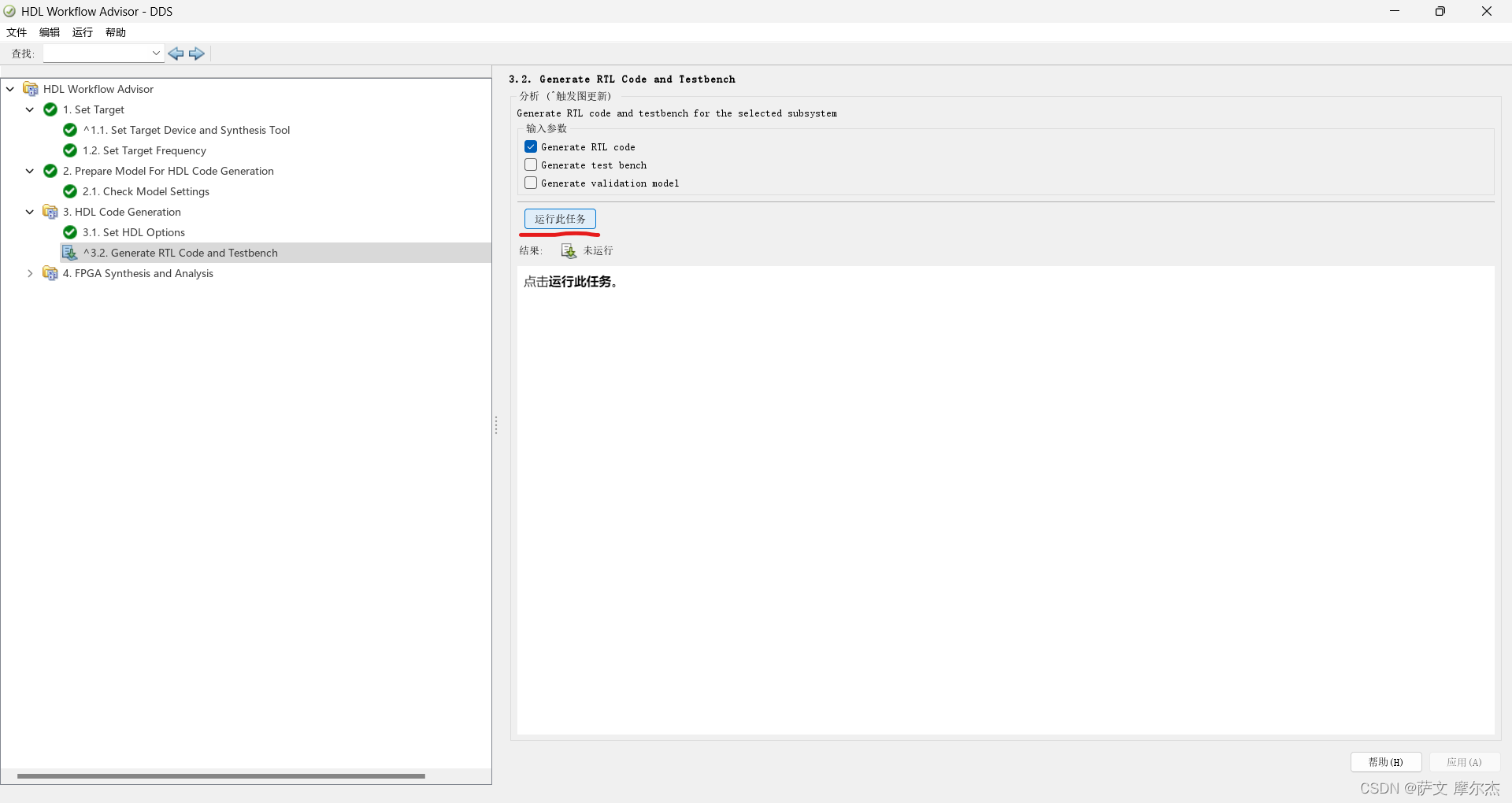

也可以选择生成Testbench,但是需要配置Modelsim,本人还没有学会。。

- 运行完4.1步后Quartus项目生成完毕

- 会在刚开始指定的文件夹内生成一个hdlsrc和quartus_prj文件夹,其中hdlsrc文件夹内是生成的.v文件,quartus_prj内是qsf文件

成功!

总结

本文简单介绍了simulink中HDL Coder的使用,给博主还在军训的兄弟提供一点参考,希望退伍老兵在使用HDLCoder时少走弯路。