- 1拆分xlsx与csv(python实现)_pathon len(sheetnames)

- 2Github贡献PR六部曲_github 如何 pr

- 3M 有效算法

- 4Go进阶:总结19款Go语言日常开发中使用到的热门开源项目_go项目

- 5docker swarm 搭建 elasticsearch 集群_docker elasticsearch配置 swarm

- 6vsCode运行python设置argparse参数_vscode跑模型时修改argparse参数

- 7GitHub使用教程和网络卡顿问题

- 8git删除历史二进制文件_git 删除云端的二进制

- 9NFT Insider #98:The Sandbox与Forkast Labs 达成合作,苹果的混合现实头显将增强游戏和元宇宙

- 10微软小娜关闭服务器,请问微软小娜 (Cortana) 要退出中国了吗?

汽车信息安全--如何理解TrustZone(1)_什么是trustzone?trustzone是如何实现安全隔离的

赞

踩

目录

1.车规MCU少见TrustZone

在车规MCU里,谈到信息安全大家想到的大多可能都是御三家的HSM方案:英飞凌的HSM\SHE+、瑞萨的ICU、恩智浦的HSE/CSE,这些都被称为HTA(Hardware Trust Anchors)。

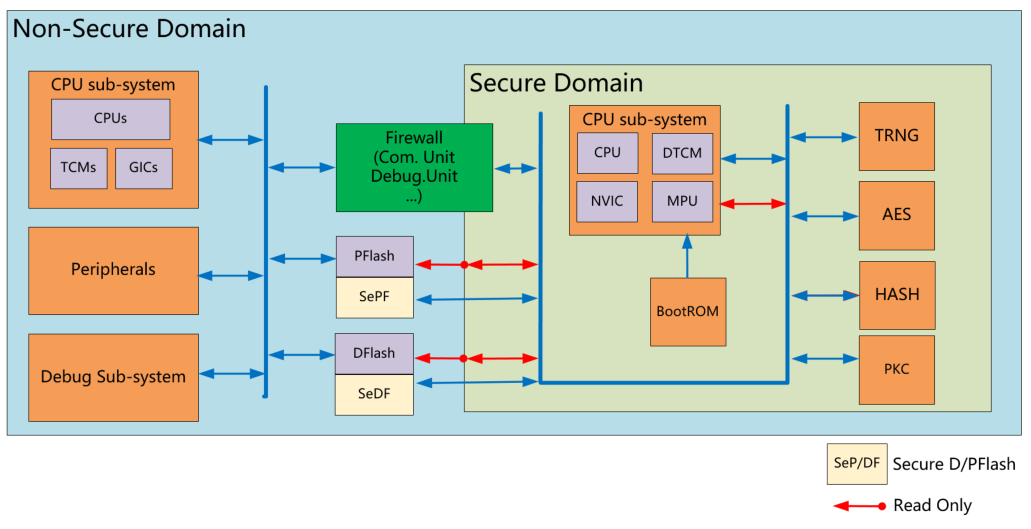

这三家的MCU架构里,Host和HSM分别有自己独立的CPU、密码算法硬件加速器、独占Flash等,如下图:

而当我Review Vector培训材料时,发现了以前经常听到但没有深入研究过的TrustZone也被当做了HTA:

那么什么是TrustZone?它与HSM区别在哪里?今天就通过Cortex-M33来分析一下。

2. 什么是TrustZone

根据Arm官方介绍,TrustZone最先是Arm A核的一种安全架构的统称,它在SOC系统级别提供硬件隔离机制将系统分成了两个运行环境:TEE(Trusted Execution Environment)和REE( Rich Execution Environment):

在REE中,通常执行复杂且功能丰富的应用软件,意味着其攻击面广,更易遭受网络攻击;在TEE中通常为REE提供授信服务,例如加解密、密钥管理等等,这与HSM/SHE的理念比较相似。

后来随着IoT的发展,M核的处理器也提出了相应的信息安全需求,所以TrustZone在ARM V8-M中作为Security Extension被引入。

2.1 TrustZone隔离了什么?

在Armv8-M架构下引入安全扩展后,从CPU、到系统外设资源再到访问方式上都做了隔离和新的设计。

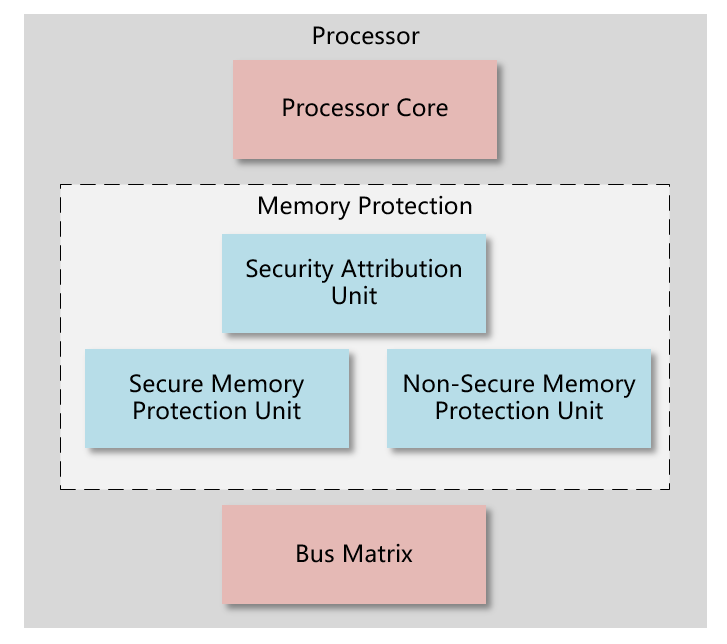

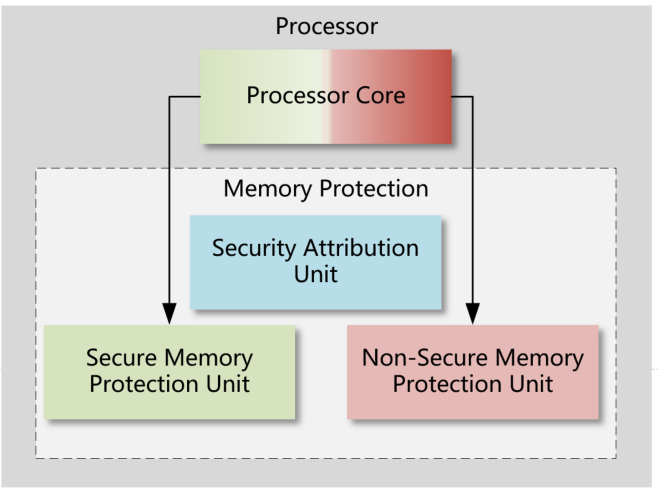

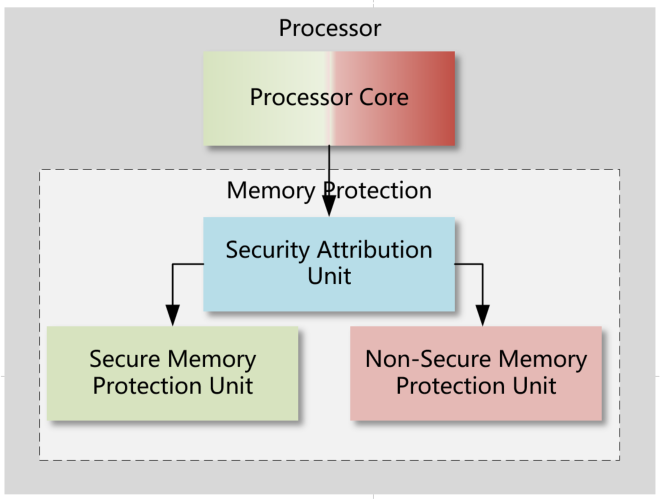

从内核角度来看,与安全扩展相关的组件包括Processor Core、SAU、SMPU和NSMPU、BusMatrix,总结如下图:

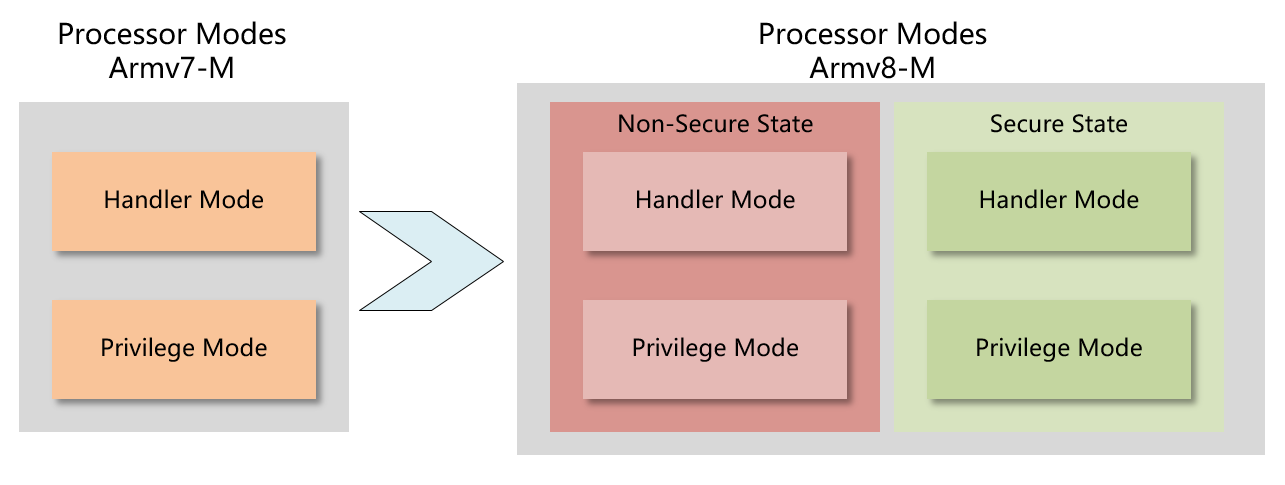

对于Processor Core的运行状态,引入了Non-Secure和Secure状态:

SAU用于定义和识别存储器地址的安全区域和非安全区域,在Secure和Non-Secure状态下分别有各自的MPU

通常情况下,CPU进行数据访问时,根据当前内核运行处于安全或非安全,从而索引到SMPU或者NSMPU的配置,如下图:

当CPU取指时,通过SAU中配置的目标地址安全属性,从而索引到SMPU或者NSMPU,如下:

既然内核、SAU和MPU有Secure和Non-Secure之分,那么在存储器、外设等属性上也应该有该分类。在M33里使用了AMBA5 AHB5,该总线携带安全、非安全访问标记,可实现安全和为安全的访问,因此,在芯片设计之初,从内核到芯片级别的完整硬件隔离机制可按如下示例实现:

2.2 处理器寄存器和异常处理

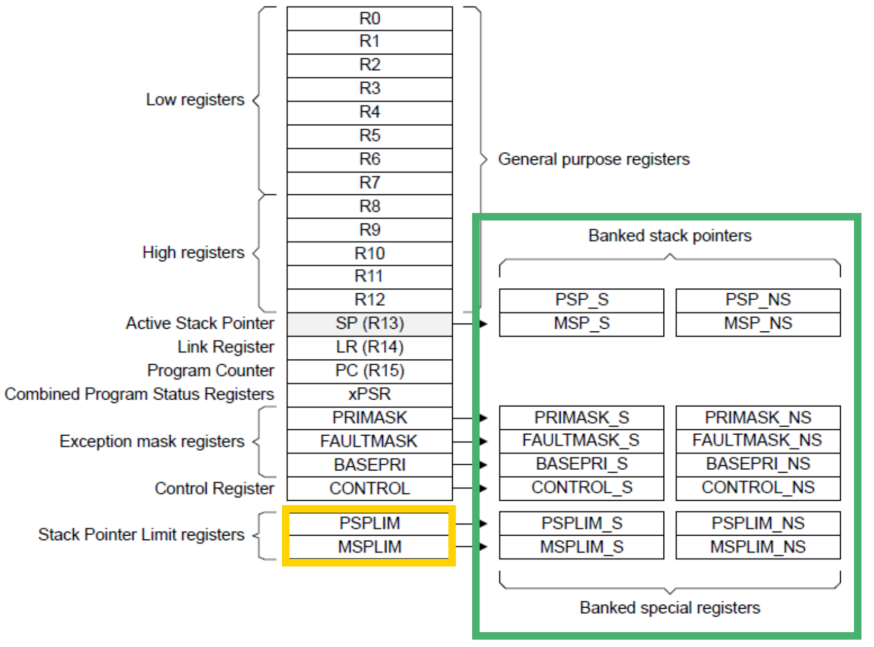

当安全扩展引入后,处理器分为了Secure和Non-Secure两种状态,因此对应状态的寄存器相应也有变化。如下图所示:

- R0-R12:Secure和Non-Secure状态共用一套;

- SP:包含MSP(Main)和PSP(Process)(针对Handler和Thread Mode),在不同状态下有两组Banked寄存器,后缀为S、NS;

- PSPLIM、MSPLIM:新增寄存器,用于限制MSP和PSP堆栈,在不同状态各有一套;

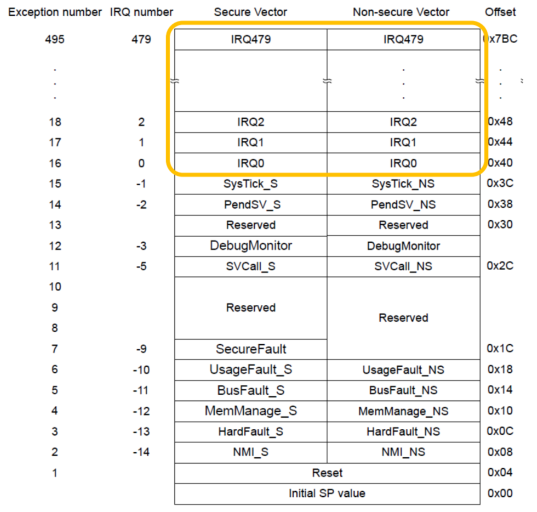

同样的,在异常也可以被指定为Secure和Non-Secure。那么从软件角度来看,中断向量表也需要分为安全和非安全两个,如下图:

可以看到,Secure和Non-Secure都有各自的Handler,有些中断是Banked,但也有些异常是只有Secure才有,如SecureFault。

需要注意的是,所有外设中断上电默认都指向Secure 向量表,但是我们可以在Secure状态运行的代码里修改权限,将外设指向Non-Secure向量表。

3.小结

本文讲解了什么是Trustzone,下文我们继续讲解与HSM的区别、