- 1uniapp 实现tabBar-switchTab之间的传参_uni.switchtab传参

- 2【数据结构】双向链表(思路解释,插入,删除,打印. c++代码)_删除双链表的节点有没有顺序

- 316款开源的全文搜索引擎_java搜索引擎

- 4鸿蒙嵌入式开发工程师“钱”景如何?_嵌入式和鸿蒙

- 5在VS中打开.ui,几秒后退出_vsuiffi

- 6机器学习-算法-半监督学习:半监督学习(Semi-supervised Learning)算法

- 7chatgpt赋能python:Python列表如何倒序输出?_列表逆序输出

- 8PlutoSDR软件无线电平台带宽破解_configureplutoradio

- 9什么是第三方库/程序?_第三方库是什么意思

- 10审稿意见的“so what”如何处理?

AXI Quad SPI IP核基于AXI-Lite接口的标准SPI设计指南_axi quad spi 远程升级

赞

踩

在标准SPI配置下,SPI设备除了包含基本的SPI特性外,还具备以下一些标准功能,这些功能如下所示:

- 支持FPGA内部的多主设备配置,其中使用单独的_I(输入)、_O(输出)、_T(三态)表示三态端口。这种配置允许在FPGA内部有多个主设备共享SPI总线,通过三态驱动器来实现。

- 在默认配置下支持N次8位数据字符的传输。默认的SPI模式实现了通过写入SPI SSR(SPI状态/控制寄存器)来手动控制SS(从设备选择)输出的功能。

此模式只能与外部从属设备一起使用。

在SPI通信中,当FIFO被禁用时,可以选择一个可选操作,使得主设备在每次传输8位字符时 自动切换SS(从设备选择)输出。这是通过SPI控制寄存器(SPICR)中的某个特定位来实 现。

当主设备需要向特定的从设备发送数据时,它会将相应的SS线拉低(通常表示选中该从设 备)。然后,在每个8位字符传输完成后,主设备会自动切换SS线,以便选择下一个从设备 或继续与当前从设备通信。

- 支持多主设备环境,这通常是通过三态驱动器来实现。在多主设备环境中,可能存在多个主设备试图同时访问同一从设备的情况,因此需要软件仲裁来解决可能的冲突。

- 支持多从设备环境,能够自动生成额外的从设备选择输出信号,以便主设备可以选择性地与不同的从设备进行通信。

- 在主模式下,SPI控制器支持的最大时钟速率可达AXI时钟速率的一半。

- 在从模式下,由于AXI和SPI时钟之间的同步方法,最大时钟速率降至AXI时钟速率的四分之一。注意,在从模式下不支持

C_SCK_RATIO = 2的配置。当配置为从模式时,需要确保AXI和外部时钟信号是对齐的。 - 具有一个可配置的波特率生成器,用于生成SPI时钟信号。这允许用户根据应用需求调整SPI通信的速率。

- 不支持WCOL(写冲突)标志,因此WCOL不能用作写冲突错误指示。在SPI数据传输进行中时,不应向发送寄存器写入数据。

- 支持背靠背(back-to-back)事务,即在不中断的情况下进行多个字节、半字或字的传输。这要求发送FIFO在传输过程中始终不为空,接收FIFO始终不为满。

- 所有SPI传输都是全双工的,意味着主设备向从设备发送一个8位数据字符的同时,从设备也在向主设备发送一个独立的8位数据字符。这可以视为一个循环的16位移位寄存器,其中SPI主设备中的8位移位寄存器与SPI从设备中的另一个8位移位寄存器相连。

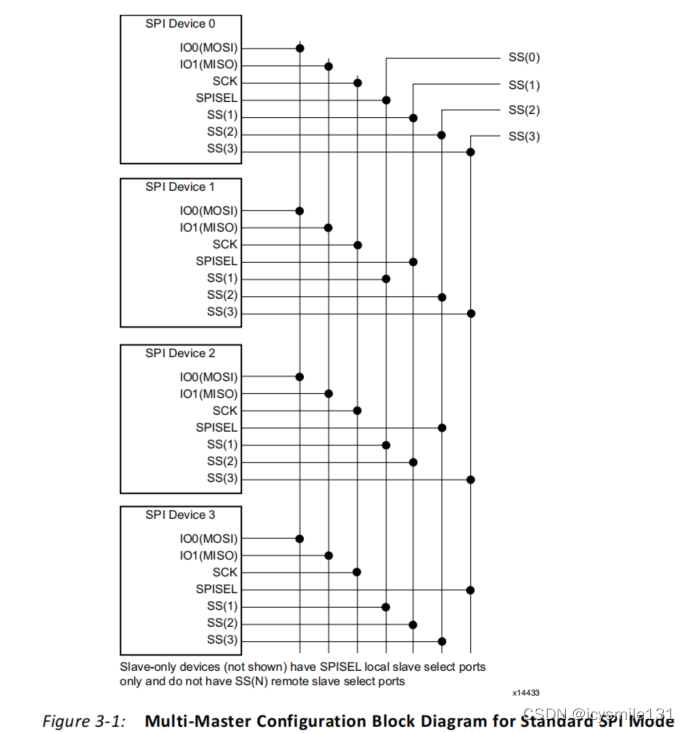

在SPI多主设备配置中,连接到给定从设备(第N个设备)的SPI总线通常由以下四根线组成:

-

Serial Clock (SCK): 串行时钟线,用于同步主设备和从设备之间的数据传输。所有连接到SPI总线的从设备和主设备都共享这根线。

-

IO0 (Master Out, Slave In (MOSI)): 主设备数据输出,从设备数据输入线。主设备通过这根线发送数据到从设备,而从设备通过监听这根线来接收数据。同样,这根线也是所有连接到SPI总线的设备所共享的。

-

IO1 (Master In, Slave Out (MISO)): 主设备数据输入,从设备数据输出线。从设备通过这根线发送数据到主设备,主设备通过监听这根线来接收数据。这根线也是共享的。

-

Slave Select (SS(N)): 从设备选择线,也称为片选线或NSS(Negative Slave Select)。在SPI多主配置中,每个从设备都有一个独特的SS线,用于标识和选择该从设备以进行通信。当主设备需要与某个特定的从设备通信时,它会将对应从设备的SS线拉低(激活状态),而保持其他从设备的SS线为高电平(非激活状态)。这样,只有被选中的从设备会响应主设备的通信请求。

虽然SCK、IO0(MOSI)和IO1(MISO)这三根线是共享的,但每个从设备都有一个独特的SS线,用于在多主配置中区分和选择从设备,如下图所示。此外,任何连接到SPI总线的设备(无论是主设备还是从设备)都可以根据配置(例如通过寄存器设置)在运行时动态地切换其角色(从主设备变为从设备,或从从设备变为主设备)。

注:当IP核在主机模式下生成,但通过寄存器配置(60h)将其配置为从机时,SPISEL(Slave Select)信号应由SPI主机驱动到该IP核。这意味着,尽管该IP核可能是在主机模式下创建的,但通过特定的配置,它可以作为从机工作,并从主机接收选择信号。

每个SPI主机设备都可以生成一个低电平有效、一位热编码(one-hot encoded)的SS(N)向量。在这个向量中,每一位都被分配了一个SS信号,用于控制每个SPI从机设备。这意味着主机可以同时管理多个从机,通过不同的SS信号来激活和与特定的从机通信。

SPI主机和从机设备可以都是FPGA内部的,也可以有外部的从机设备。当与外部SPI从机设备接口时,Vivado Design Suite会自动生成必要的SPI引脚。这提供了与外部硬件通信的接口。

图3-1展示了多个SPI主机和从机设备的配置。这种配置同样适用于dual 模式。