热门标签

热门文章

- 1西安华为OD面试经验(德科)_华为od背调

- 2python入门14:os库,遍历文件夹下的所有文件,一些常用函数(获取文件目录、判断文件是否存在、合并路径、删除文件等),以及应用举例_os库遍历删除文件

- 3在linux操作系统上安装sqlserver_linux安装sqlserver

- 4【机器学习】Exam4

- 5UniApp与React的比较:移动应用开发框架的对比_uniapp react

- 6ComfyUI + Stable Diffusion 3(Windows 11)本地部署教程_stable diffusion 3.0 windows本地部署

- 7运行stable-diffusion出现的问题_checkout your internet connection or see how to ru

- 8如何降低AI辅写疑似度?7招助你论文过关!_aigc论文降低

- 9MySQL索引的正确使用姿势_mysql index lookup

- 10Visual Studio Code 常见的配置、常用好用插件以及【vsCode 开发相应项目推荐安装的插件】_vscode structure

当前位置: article > 正文

PS与PL协同设计实现GPIO学习记录_ps pl联合

作者:IT小白 | 2024-07-15 17:50:01

赞

踩

ps pl联合

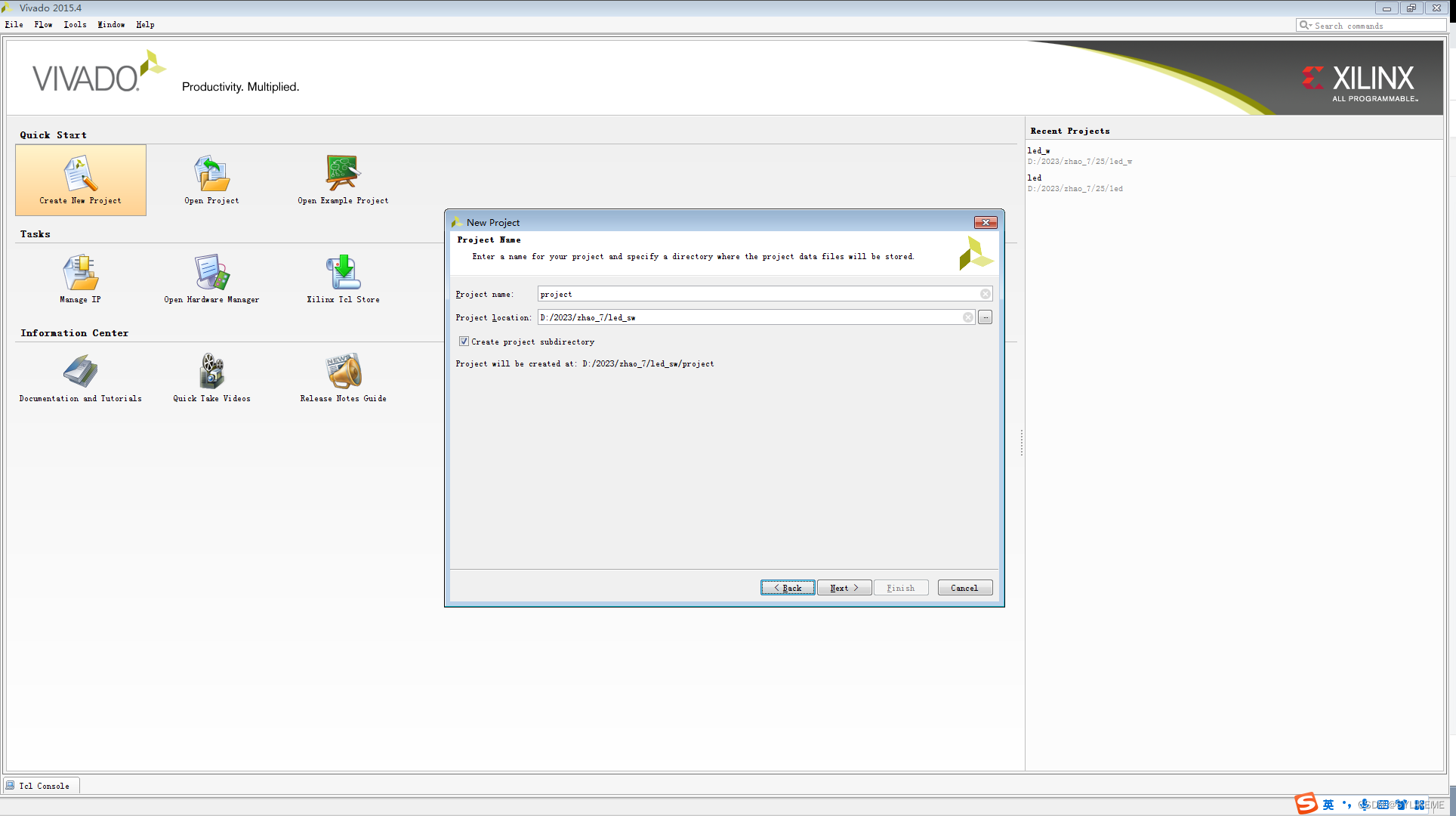

本次学习用的软件是VIVADO,版本2015.4.

同PL端开发一样,PS端同样需要创建工程。

所用的开发板是ZEDBORAD

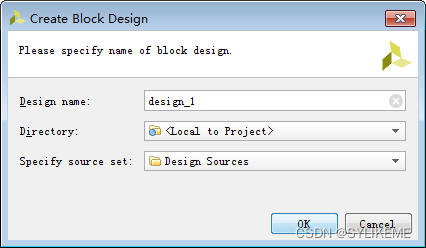

创建Block design。

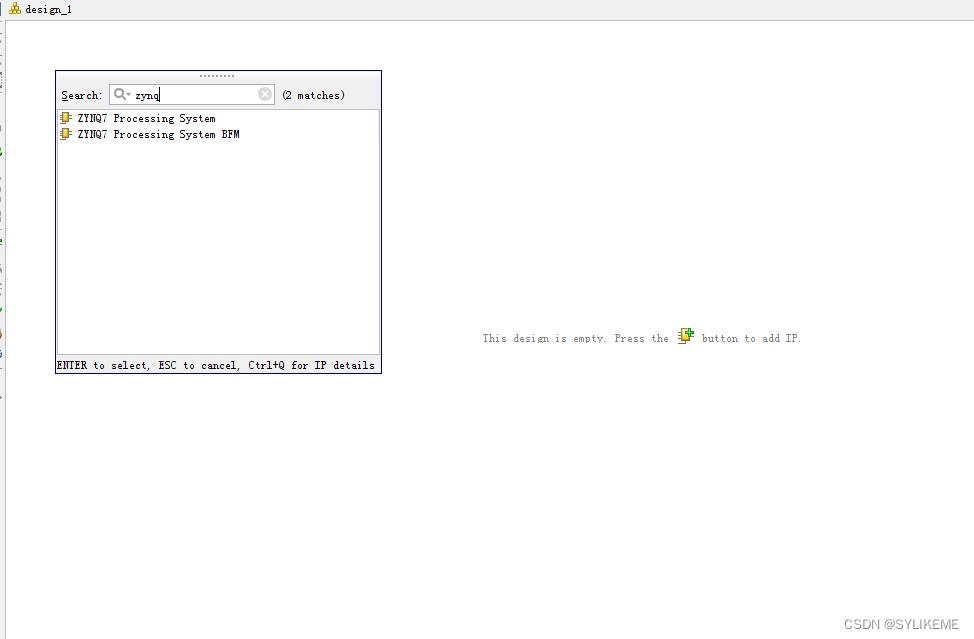

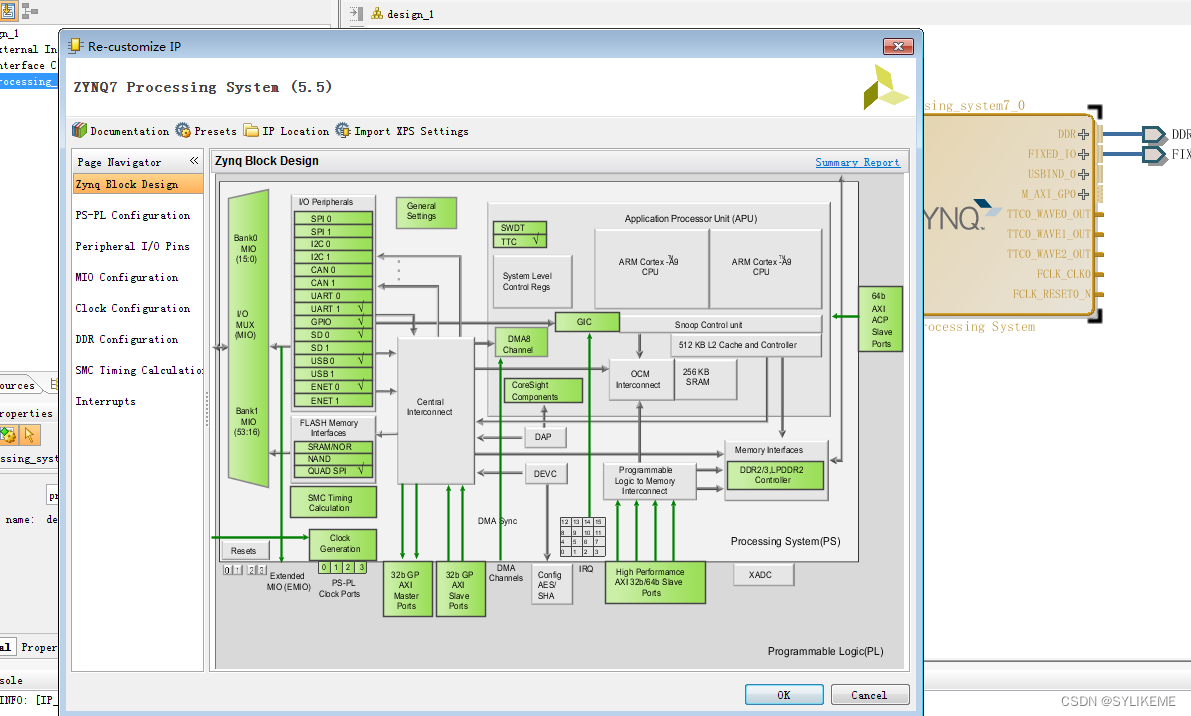

在Diagram中添加 ZYNQ7 Processing System。

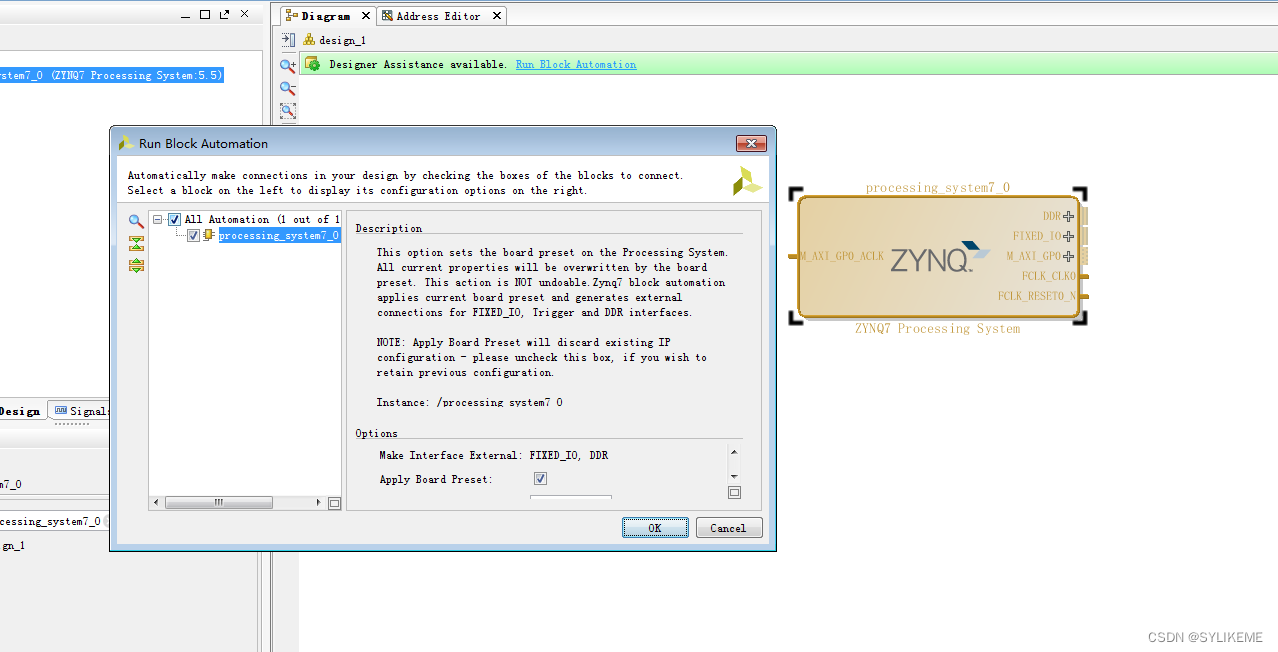

点击run block automation,根据Zedboard中所存有的配置来配置system。

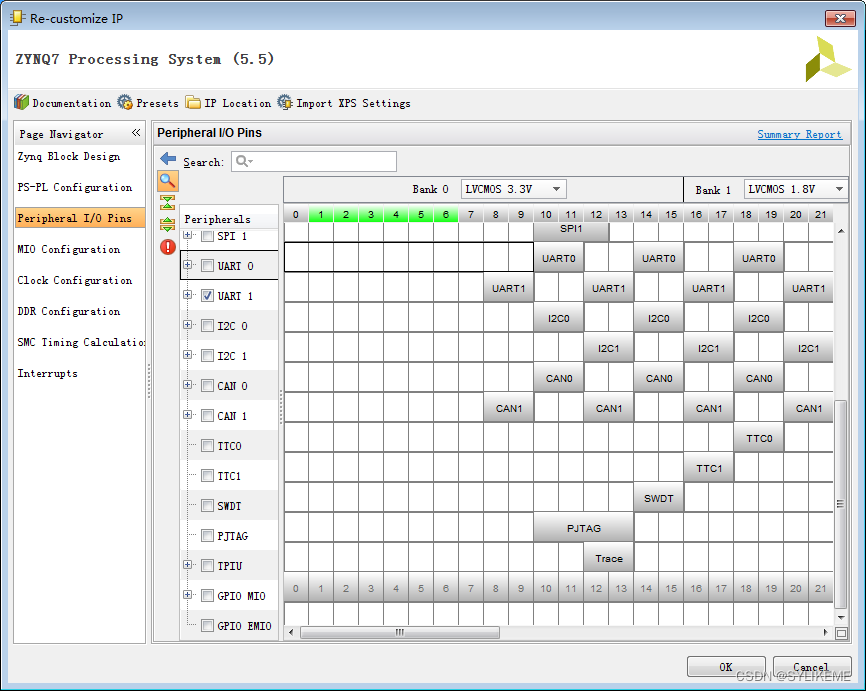

双击system来勾选我们需要的接口。

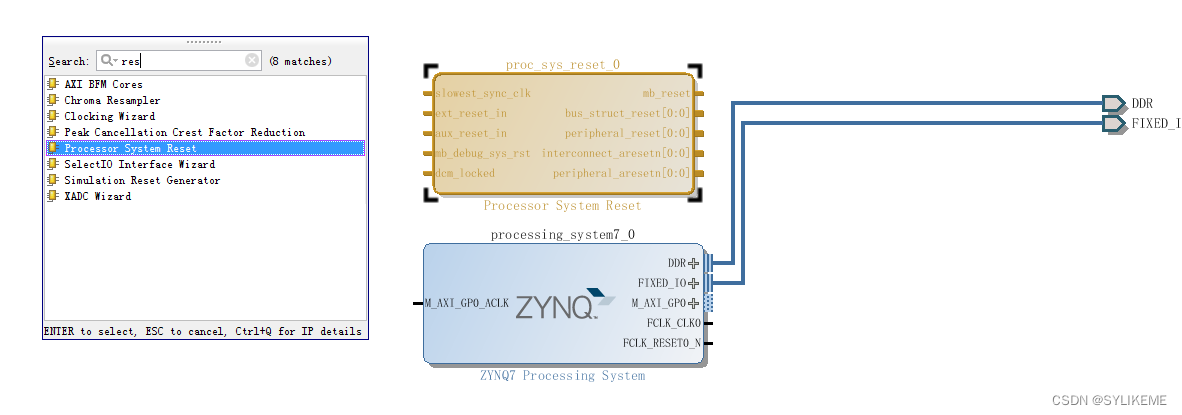

一般来说需要加上一个复位模块。

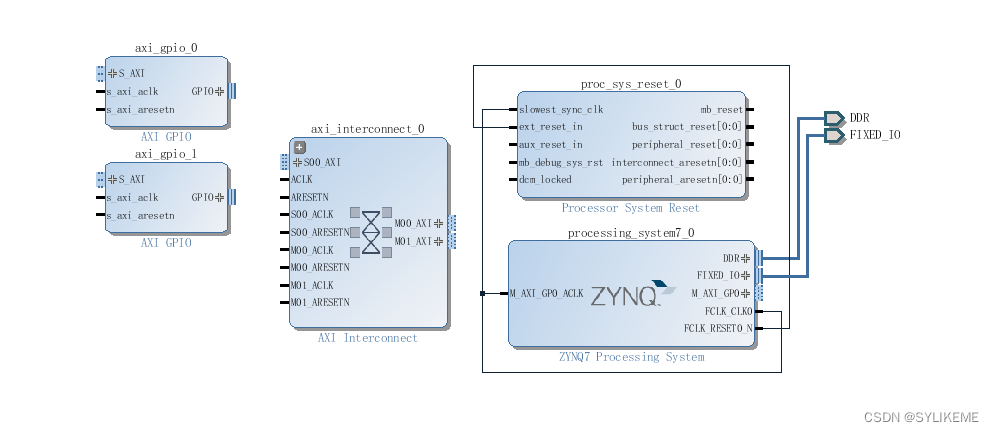

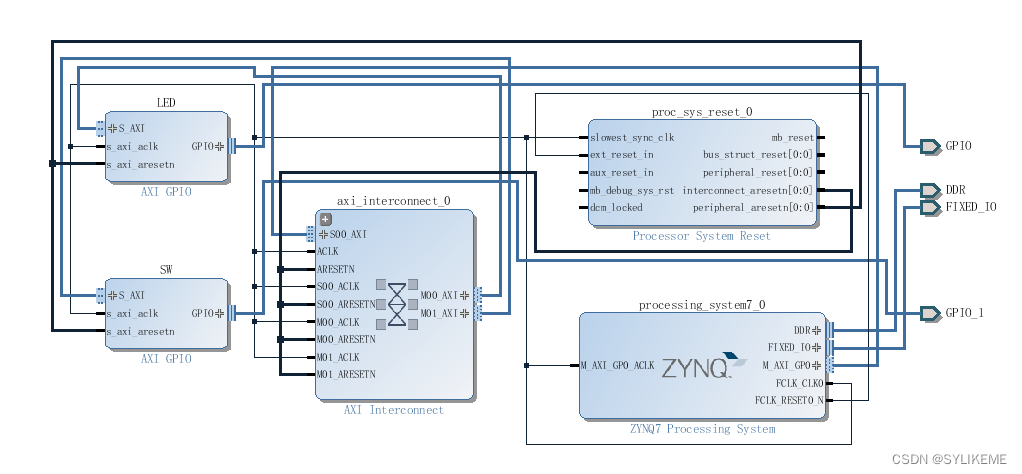

本次还需要一个AXI Interconnect和两个GPIO模块。

将模块进行连接。

将模块进行连接。

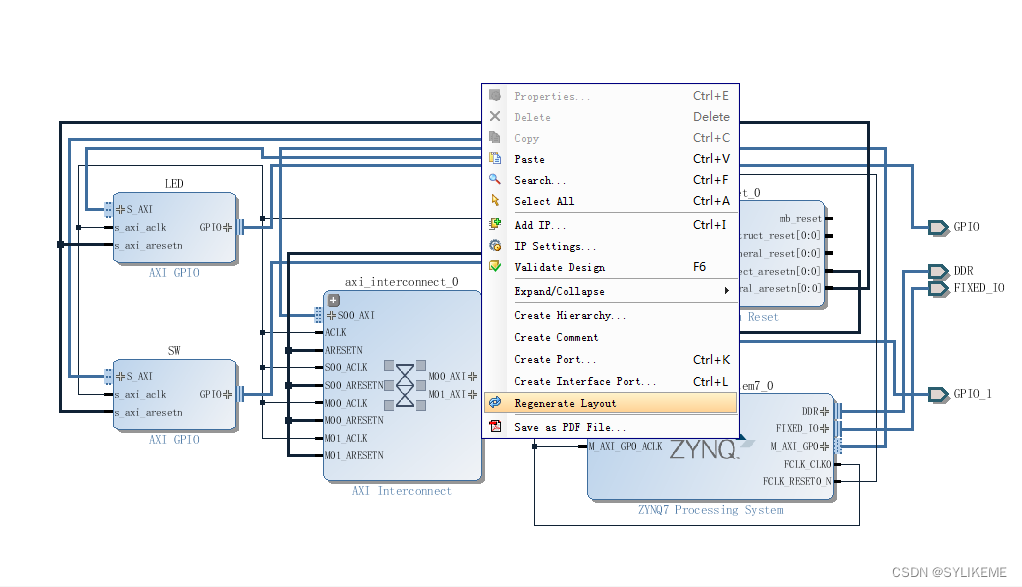

重新布局。

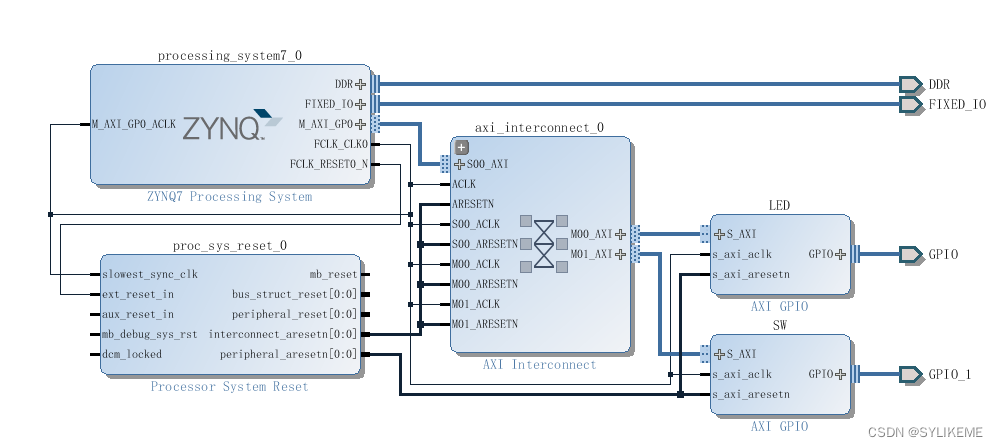

布局后。

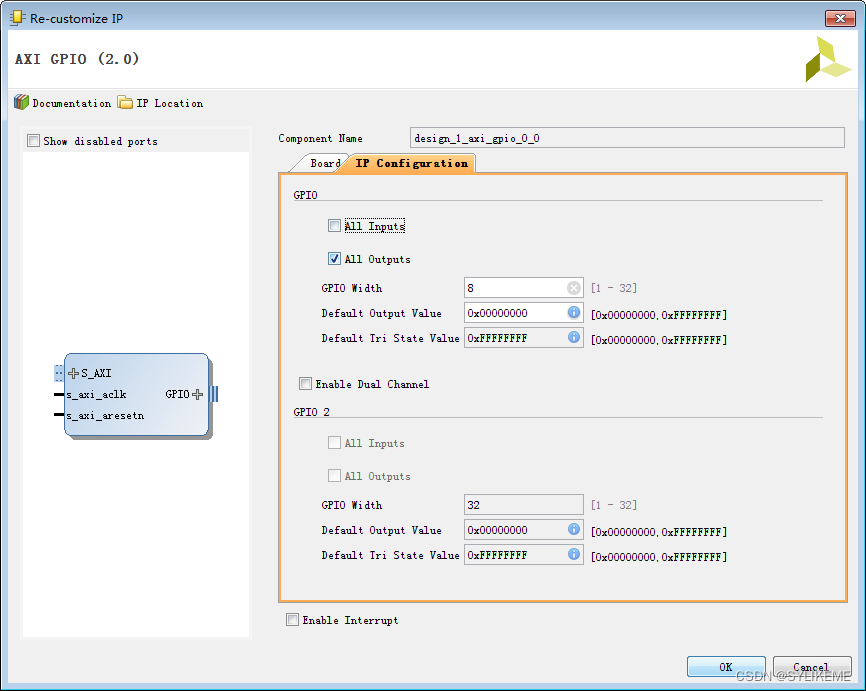

配置GPIO全为输出,宽度为8位。另外一个全为输入,宽度也是8位。

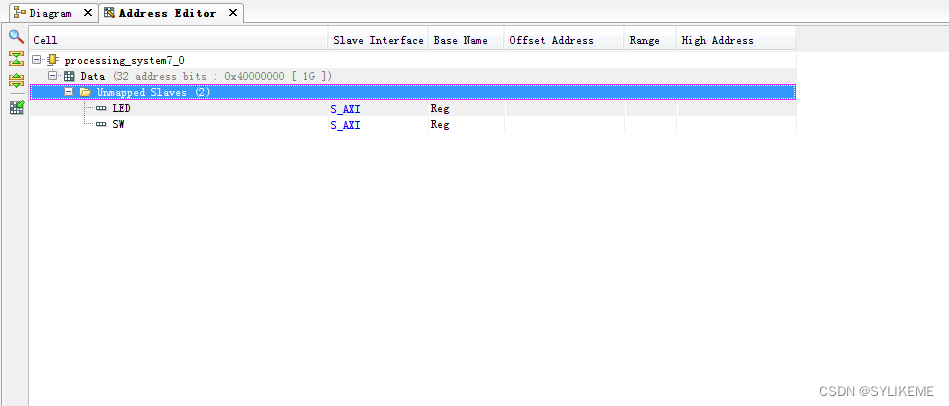

由于FPGA要控制外设是通过寄存器来控制的,而寄存器要映射FPGA的寻址地址。给没有映射的外设配置地址,之后保存。

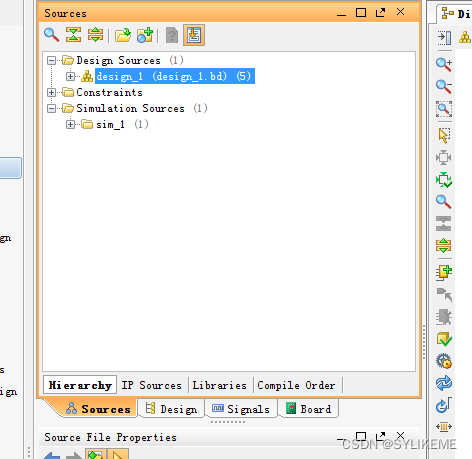

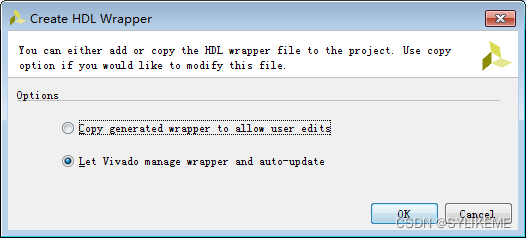

之后在sources中点击右键点击generate output products 和 create HDL wrapper。

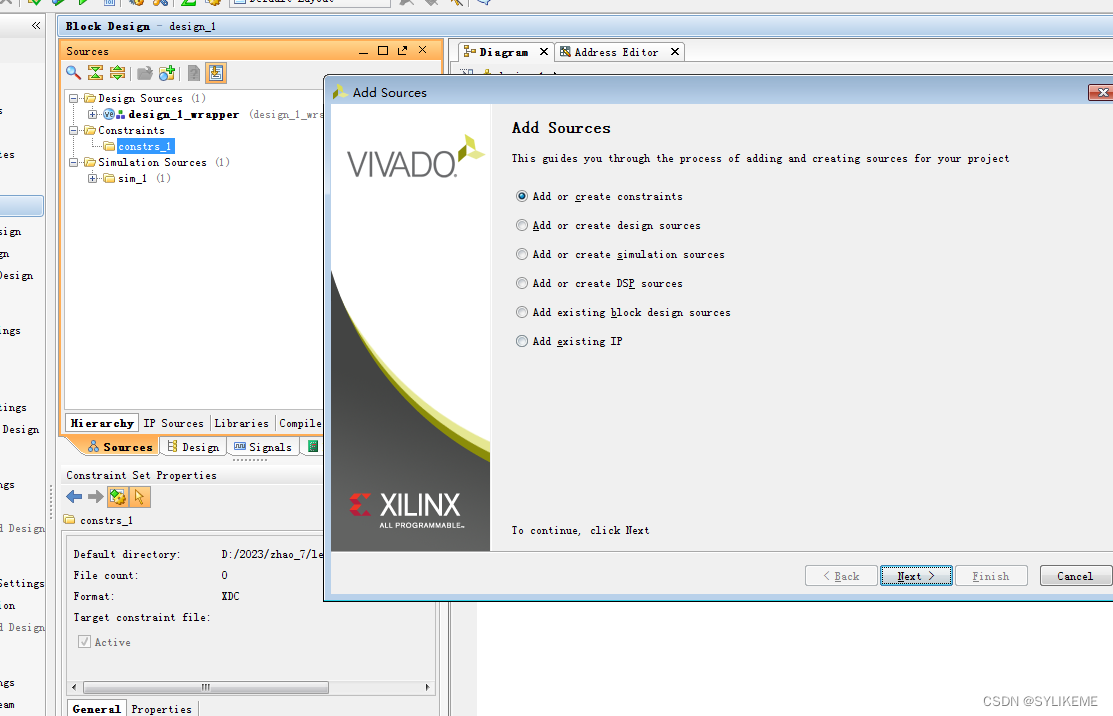

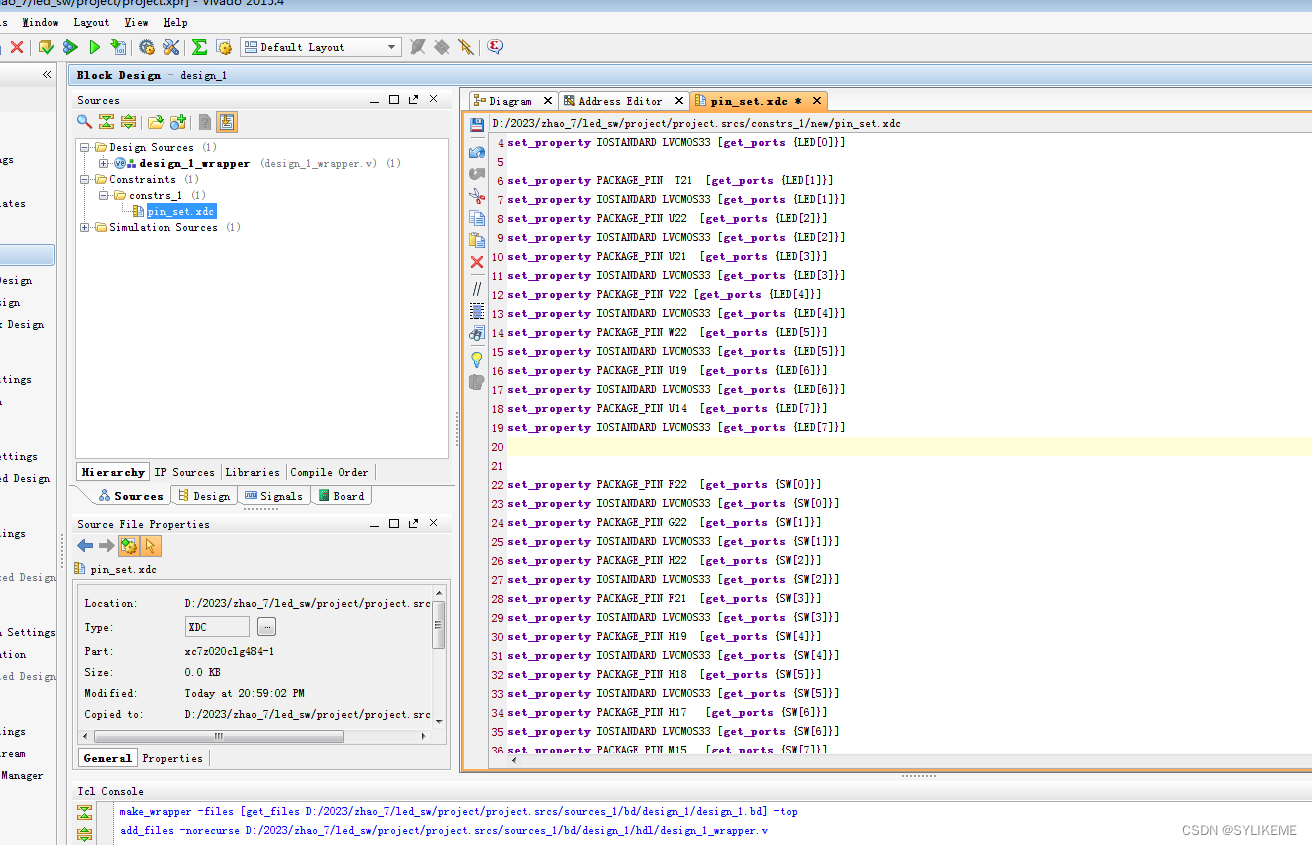

建立约束文件,绑定引脚。

编写约束文件,并保存。之后点击生成bit流。

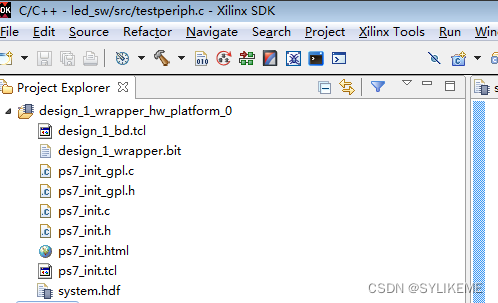

生成BIT流文件之后,先点击file>export>export hardware 之后launch SDK。

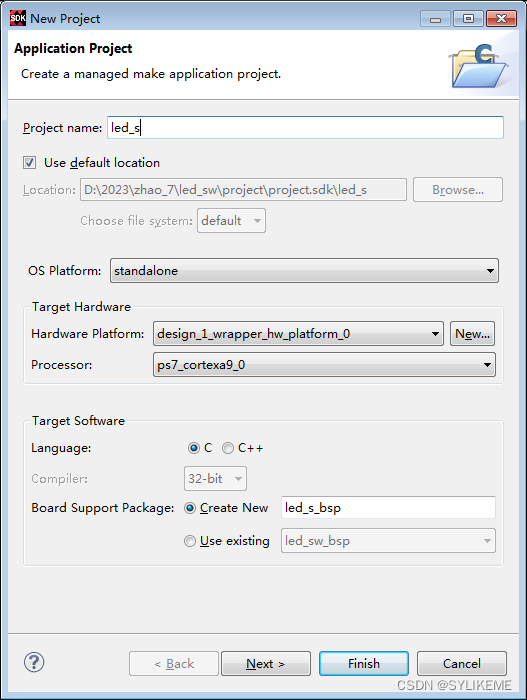

点击File>NEW>Application file

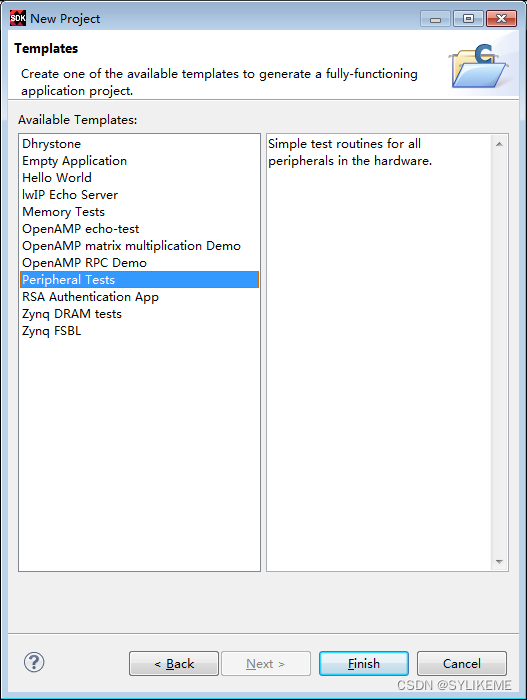

点击Next,选择Peripheral Tests。

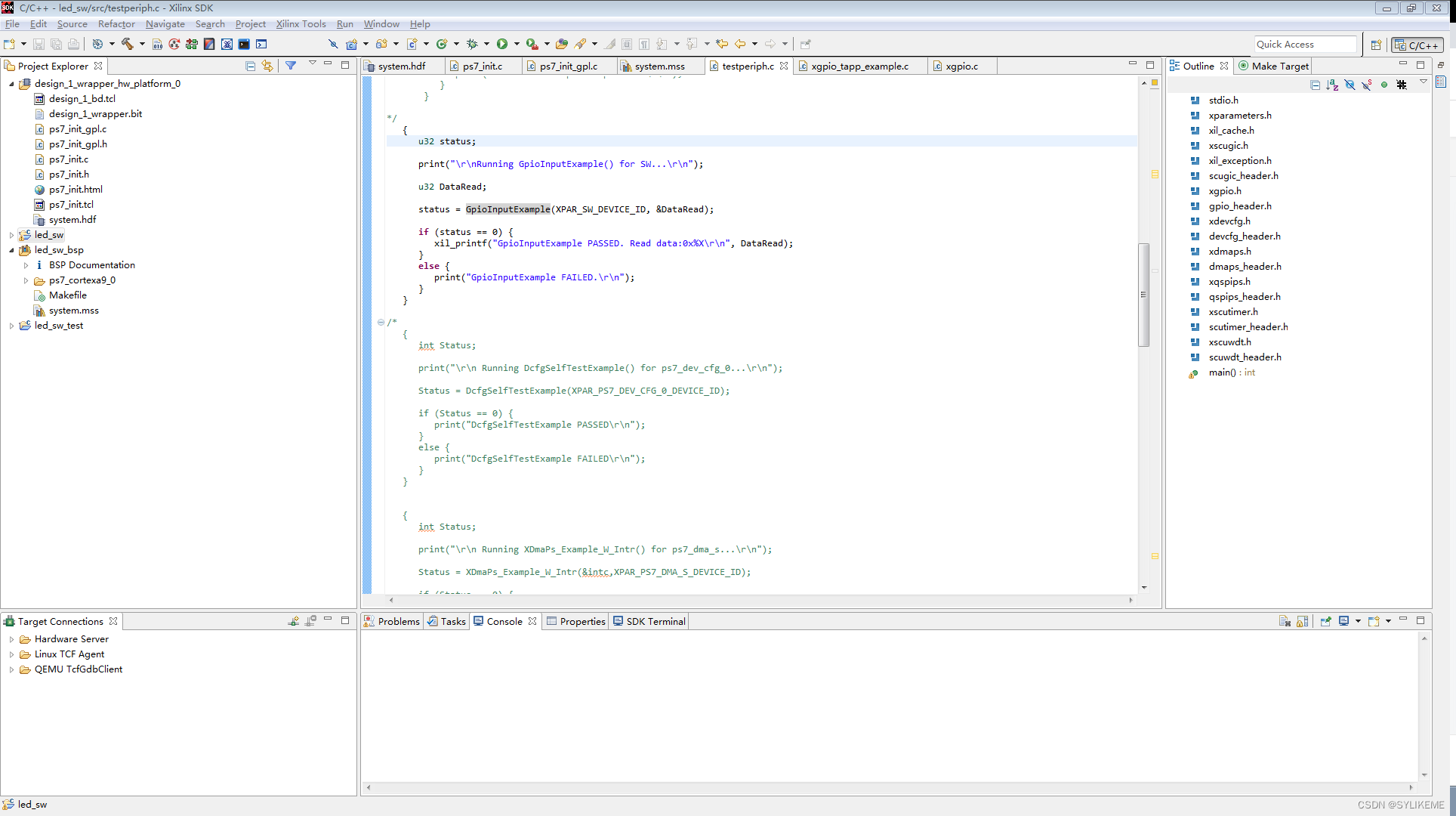

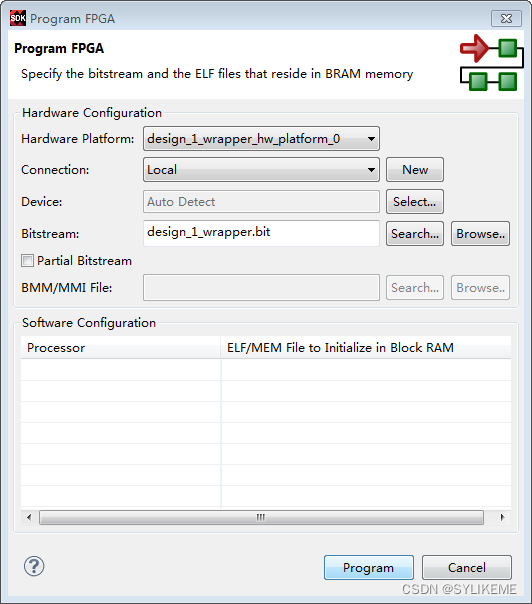

在所建立的app 文件中编辑程序。之后点击Xilinx Tools > program FPGA 进行烧写程序。

在所建立的app 文件中编辑程序。之后点击Xilinx Tools > program FPGA 进行烧写程序。

之后点击Run > Run as >Launch on hardware。板子即可运行程序。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/IT小白/article/detail/830472?site

推荐阅读

相关标签