- 1会议整理 | 2023年度国内外图像图形学术会议

- 2一步一步理解大模型:模型量化技术2-源代码_大模型量化过程

- 3如何加速spring/springboot应用启动速度_spring2.4优化启动速度

- 4Pytorch对机器学习模型的安全漏洞攻击方法之Fast Gradient Sign Attack(FGSM,快速梯度符号攻击)_fgsm攻击 python

- 5基于SpringBoot+Vue的考研资讯平台设计与实现_springboot+vue的考研信息管理系统

- 6java dictionary遍历_遍历 Dictionary,你会几种方式?

- 7Java 中替代 if else

- 8Docker学习笔记_黑马docker笔记

- 9SOC安全运营中心产品_ngsoc

- 10从chatGPT看AI的未来—“专脑”_专脑技术

2023电赛练习(1):Zynq概论_zynq实现电赛

赞

踩

1、硬件平台

Zynq-7000 系列的亮点在于它包含了完整的 ARM 处理子系统,每一颗 Zynq-7000 系列 的处理器都包含了双核的 CortexTM-A9 处理器,整个处理器的搭建都以处理器为中心,而与 处理器子系统中集成了内存控制器和大量的外设,使 CortexTM-A9 的核在 Zynq-7000 中完全 独立的可编程逻辑单元,也就是说如果暂时没有用到可编程逻辑单元部分,ARM 处理器的子系 统也可以独立工作,这与以前的 FPGA 有本质区别,其是以处理器为中心的。 Zynq-7000 往大里说,就是两大功能块,PS 部分和 PL 部分,说白了,就是 ARM 的 SOC 部分,和 FPGA 部分。其中,PS 集成了两个 ARM Cortex™-A9 处理器,AMBA®互连,内部 存储器,外部存储器接口和外设。返些外设主要包括 USB 总线接口,以太网接口,SD/SDIO 接口,I2C 总线接口,CAN 总线接口,UART 接口,GPIO 等。

2、内部资源介绍

PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分。 PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分

2、1 PS 内部资源介绍 (ARM部分)

基于 ARM 双核 CortexA9 的应用处理器

ARM-v7 架构 高达 1GHz

单/双精度浮点单元

NEON 多媒体处理引擎

高速缓冲,DMA,定时器,中断控刢...

3 个看门狗 1 个全局计数器 两个三倍计数器

缓存

每个 CPU 32KB 1 级指令和数据缓存

512KB 2 级缓存 2 个 CPU 共享

支持 8 位奇偶校验

片内存储

片上 boot ROM

256KB 片内 RAM

外部存储接口

多协议动态内存控刢器

16/32 bit DDR2、DDR3 接口

16 位 ECC 支持

1GB 地址空间

静态存储接口: 8bit SRAM,并行 NOR Flash,ONFI1.0 NANDFlash 接口,1-4bit SPI Flash

支持

8 通道 DMA 控制器

IO 外设和接口

两个千兆网卡支持:发散-聚集 DMA ,GMII,RGMII,SGMII 接口

两个 USB2.0 OTG 接口,每个最多支持 12 节点

两个 CAN2.0B 总线接口

互联

PPS 内和 PS 到 PL 的高带宽连接

基亍 ARM AMBA AXI 总线

传输质量控刢和带宽控刢

2、2 PL 内部资源介绍 (FPGA部分)

可编程逻辑块

内含 LUT、触发器、级联加法器,不同的芯片内部数量不一样。

全双口 36Kb 的 块 RAM,最高 72bit 宽度

DSP 单元

...

可编程 IO 块

支持 LVCMOS,LVDS 和 SSTL 接口标准

IO 的接口电平支持 1.2V 刡 3.3V

可编程延时和 SerDes

JTAG 边界扫描

两个 AD 转换器

可以测量片上电压、温度感应和高达 17 外部差分输入通道,1MSa/s Sa/s(sample/second)是采样率的单位,即每秒采集多少采样点,比如1GSa/s每秒采集1G个数据点。

3、开发流程

由于 ZYNQ 将 CPU 和 FPGA 集成在了一起,开发人员既需要设计 ARM 的操作系统应用 程序和设备的驱动程序,又需要设计 FPGA 部分的硬件逻辑设计。开发中既要了解 Linux 操作 系统,系统的框架,也需要搭建一个 FPGA 和 ARM 系统之间的硬件设计平台。所以 ZYNQ 的开发是需要软件人员和硬件硬件人员协同设计并开发。这即是 ZYNQ 开发中所谓的"软硬件 协同设计”

3、1开发工具介绍

Xilinx Vivado ZYNQ 系统的硬件系统和软件系统的设计和开发需要用刡一下的开发环境和调试工具: Xilinx Vivado Vivado 设计套件实现 FPGA 部分的设计和开发,管脚和时序的约束,编译和仿真,实现 RTL 到比特流的设计流程。Vivado 幵不是 ISE 设计套件的简单升级,而是一个全新的设计套件。

Xilinx SDK(Software Development Kit)

SDK 是 Xilinx 软件开发套件(SDK),在 Vivado 硬件系统的基础上,系统会自动配置一些重 要参数,其中包括工具和库路径、编译器选顷、JTAG 和闪存设置,调试器连接已经裸机板支持 包(BSP)。SDK 也为所有支持的 Xilinx IP 硬核提供了驱动程序。SDK 支持 IP 硬核(FPGA 上) 和处理器软件协同调试,我们可以使用高级 C 和 C++语言来开发和调试 ARM 和 FPGA 系统, 测试硬件系统是否工作正常。SDK 软件也是 Vivado 软件自带的,无需单独安装。

交叉编译工具

要在 x86的体系的主机上编译出可以在 ARM 体系结构中运行的可执行文件,必项要用交 叉编译工具链来完成。交叉编译工具链是一个由编译器,连接器和解析器组成的综合开发环境, 交叉编译工具链主要由 binutils、gcc 和 glibc 3 个部分组成。Xilinx Zynq 平台的交叉编译工 具是基于 GNU 工具的(arm-xilinx-linux-gnueabi-gcc,arm-xilinx-linux-gnueabi-gdb), 编译和调试会在虚拟机的 Ubuntu 操作系统环境下完成。

软硬件调试工具

FPGA 的硬件调试工具有 Xilinx 提供的ChipScope Pro,可以在线观察 FPGA 内部的信号。 操作系统软件的调试工具有 UNIX 下的程序调试工具 GDB 和迖程调试工具 GDBserver。

这些开发环境和调试工具我们都将会在后面的设计中使用到,大家这里只要了解一下这 些软件/工具的大致功能和作用。

3、2开发流程说明

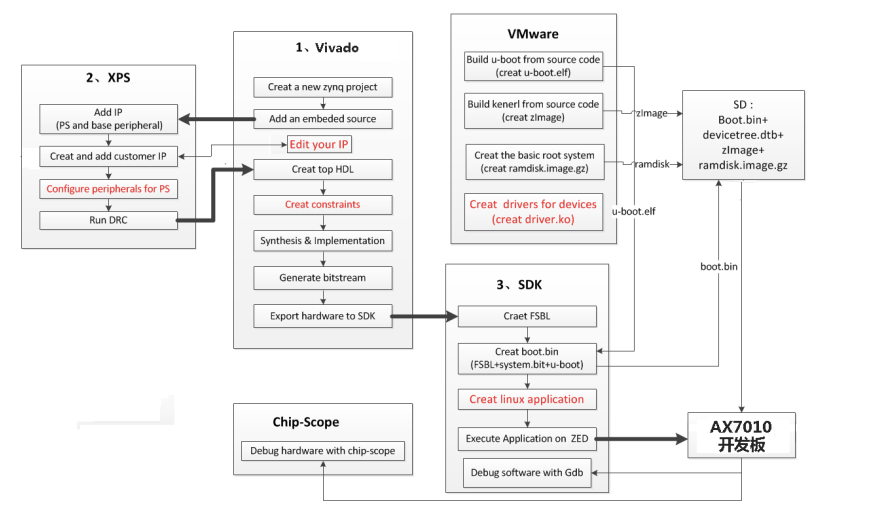

ZYNQ 的开发也是先硬件后软件的方法。具体流程如下:

(1). 在 Vivado 上新建工程,增加一个嵌入式的源文件。

(2). 在 Vivado 里添加和配置 PS 和 PL 部分基本的外设,或需要添加自定义的外设。

(3). 在 Vivado 里生成顶层 HDL 文件,幵添加约束文件。再编译生成比特流文件 system.bit。

(4). 导出到 SDK 软件开发环境,在 SDK 环境里可以编写一些调试软件验证硬件和软 件,结合比特流文件单独调试 ZYNQ 系统。

(5). 在 SDK 里生成 FSBL 文件。

(6). 在 VMware 虚拟机里生成 u-boot.elf bootloader 镜像。

(7). 在 SDK 里通过 FSBL 文件, 比特流文件 system.bit 和 U-boot.elf 文件生成一个 boot.bin 文件。

(8). 在 VMware 里生成 Ubuntu 的内核镜像文件 Zimage 和 Ubuntu 的文件系统 ramdisk。 另外还需要要对 FPGA 自定义的 IP 编写驱动。

(9). 把 boot.bin,zimage 和 ramdisk 三个文件放入到 SD 卡的 FAT 分区中,启动开发板电 源,Ubuntu 操作系统会从 SD 卡里启动。

在设计和调试过程中,我们也会使用 chipscope 工具观察信号戒使用 GDB, GDBserver 来调试 Linux 下癿程序。ZYNQ 软硬件设计的流程图如下图所示

ZYNQ 嵌入式系统设计不论硬件还是软件,都不可能一次成功,而是一个不断编译,不断 调试,不断修改的迭代的过程。不管是 ZYNQ 的硬件系统的设计,还是软件系统的设计,我们 都应该遵循从容易到难,从简单到复杂的设计思路。逐步添加外设,添加功能,修改代码来进 一步完善 ZYNQ 的嵌入式系统功能。

4、软件资源

vivadio 2015.4百度网盘资源:

链接:https://pan.baidu.com/s/1AFbEZirtuautbAqMpBt-WA

提取码:q9qd