- 1数据挖掘算法——关联分析算法(apriori和FPgrowth)_数据挖掘(关联规则(fp-growth、apriori)、分类(决策树、k-近邻、朴素贝叶斯)、聚

- 2关于IDEA(VScode)中github push时连接失败的问题解决_vscode网络原因github访问不到

- 3postgresql源码学习(27)—— 事务日志⑦-日志落盘上层函数 XLogFlush

- 4【Python入门】Python循环语句(for循环的基础语法)_python for

- 5OpenLayers中样式Style,styleMap等的设计分析和使用说明

- 6失物招领平台|基于Springboot+Vue实现失物招领系统_springboot和vue工具软件

- 7POWERLINK协议在stm32单片机+w5500移植成功经验分享_stm32 w5500

- 8写typescript项目时怎么引入第三方包的d.ts声明文件

- 9关于微信JAVA家政小程序源码技术实现方案_家政小程序java

- 10安装Ubuntu Linux,配套安装宝塔,安装禅道OK!_宝塔安装禅道

【两周学会FPGA】从0到1学习紫光同创FPGA开发|盘古PGL22G开发板学习之点亮LED灯(一)_紫光同创开发板

赞

踩

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

适用于板卡型号:

紫光同创PGL22G开发平台(盘古22K)

一:实验目的

实现对LED灯点亮和熄灭的控制,同时初步熟悉PDS软件的操作流程。

二:实验要求

控制8个LED灯以固定的周期闪烁(如点亮0.5s熄灭0.5s)。

三:实验原理

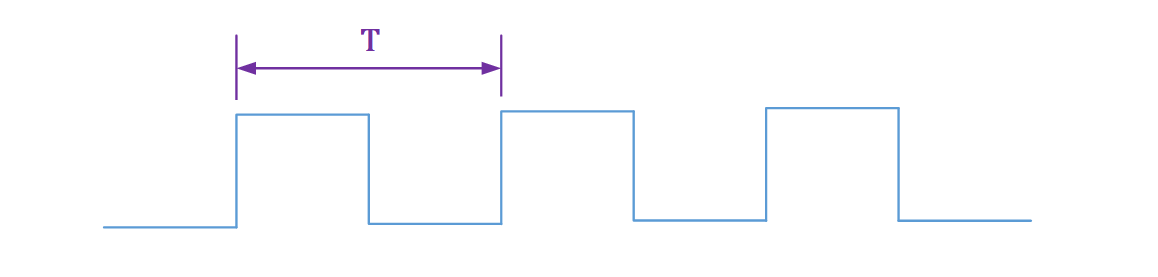

LED灯按照一定的时间进行亮与灭的转换,在FPGA中,实际原理是LED灯在一定的时钟周期内保持高电平或者低电平。时钟周期也称为振荡周期,定义为时钟频率的倒数,我们通常称之为周期(T)。时钟周期也是数字系统中的基本时间单位。

f(频率)=1(时间:秒)/T(周期)

以50MHz的时钟为例:

50MHz = f(频率)=1(时间:秒)/T(周期),那么:

T(周期)= 1(时间:秒)/f(频率)= 20ns。

也就是说,一个周期20ns,运行50_000_000个周期即为1s。

如果我们控制LED灯点亮1s,那么只需要让LED灯保持50_000_000个周期的高电平即可,熄灭1s同理。

MES22GP板卡上有一个50MHz和一个27MHz的晶振为PGL22G提供时钟信号。

四:实验分析

如上所述,点亮1s所需的周期数为:

1s = 20ns * 50_000_000次

那么点亮0.5s所需的周期数即为:

0.5s = 20ns * (50_000_000 / 2)次

控制LED亮灭需要控制IO输出的高低电平即可(高电平点亮,低电平熄灭),原理图如下:

五:实验源码设计

首先双击design建立一个文件用于编写代码。

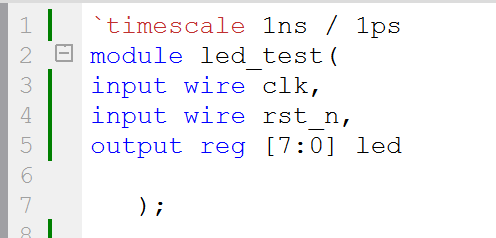

文件头部如图所示:

timescale是Verilog HDL 中的一种时间尺度预编译指令,它用来定义模块的仿真时的时间单位和时间精度。需注意PDS中每个文件的模块顶部需要自己手动添加该语句。

先定义模块的输入时钟和复位,以及输出的8个LED灯。

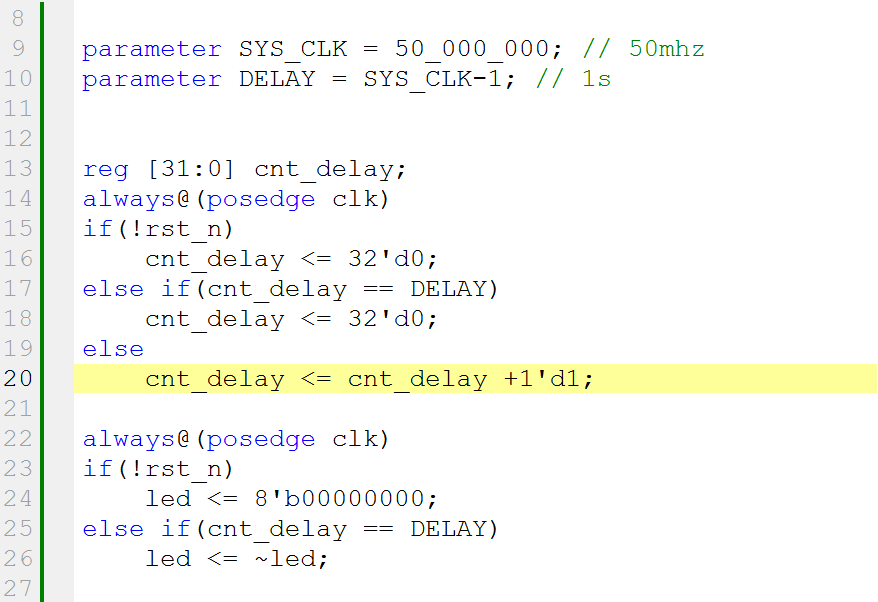

然后使用参数parameter定义输入时钟的数值和LED灯闪烁所需的频率次数方便后续多次使用,需注意参数parameter定义的数值需为常量。

接着定义一个32位的寄存器类型的变量cnt_delay用于计数,每当满足条件(达到所需频率次数)即清零,否则增加。

同时LED灯在cnt_delay计数满足条件时进行翻转(取反)即可实现闪烁控制。

六:时钟约束和管脚分配

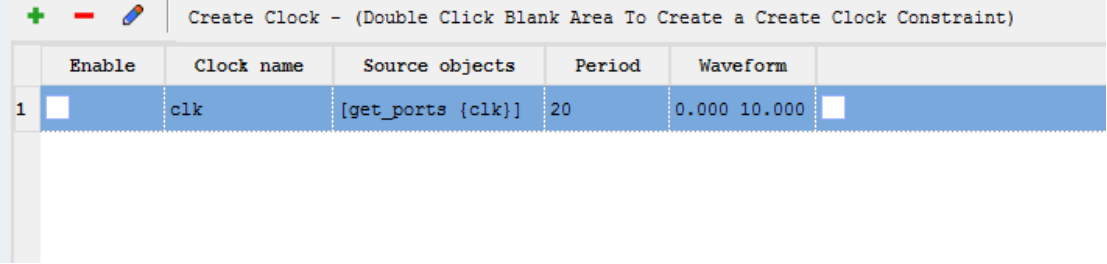

代码编写完成后(compile后未报错),点击菜单栏Tools工具栏的用户约束编辑User Constraint Editor,选择综合前约束Pre Synthesize UCE选项,选择Timing Constraints后选择Create Clock添加基准时钟,基准时钟一般是通过输入port输入用户涉及的板上时钟。

在弹窗中对时钟命名,关联时钟管脚,添加时钟参数,点击OK会创建一条时钟约束,Reset重置该页面。

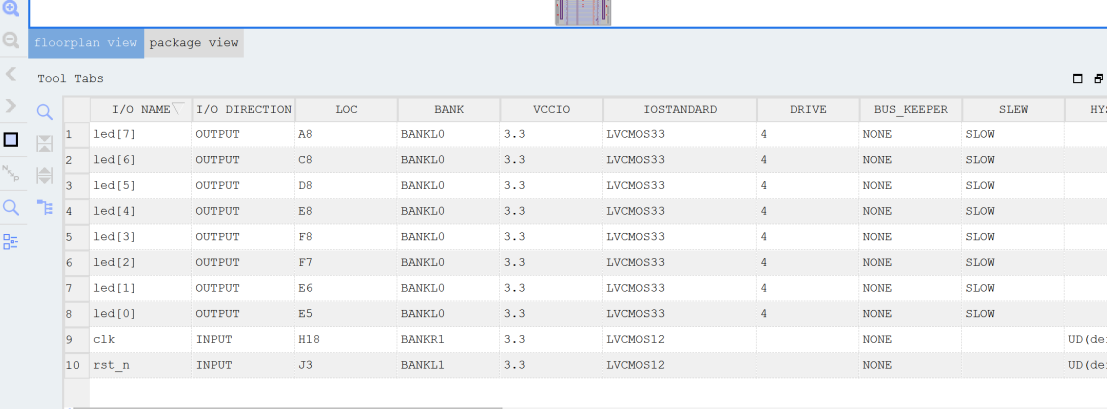

然后点击Device,选择右边的I/O图标,便可以对输入输出分配引脚了。

具体的引脚配置需要参考相关开发板的硬件手册和原理图,如

《MES22GP开发板硬件使用说明书》和《MES22GP_V1-0原理图》。

七:烧录比特流文件

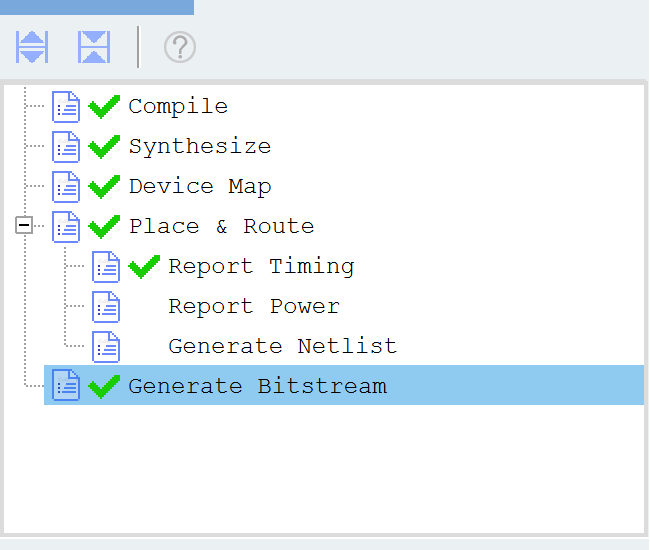

完成引脚约束后,依次双击Synthesize—>Device Map—>Place & Route—>Generate Bitstream完成综合、布局布线、生成比特流文件等相关操作。

点击下载程序的选项。

点击扫描选项。

打开要烧录的比特流文件。

点击芯片,点击右键选择Program即可烧录文件。

若开发板在已经扫描连接成功的情况下重新烧录文件,只需:

1、点击芯片,单击右键选择Assign New Configuration File重新打开要烧录的比特流文件;

2、点击芯片,点击右键选择Program烧录所需文件。