热门标签

热门文章

- 1「SQL面试题库」 No_1 员工薪水中位数_sql求员工薪水中位数

- 2关于 QSound播放wav音频文件,播放失败“using null output device, none available” 的解决方法_qsound::play using null output device, none availa

- 3渗透测试工具Kali Linux安装与使用

- 4mysql分组统计占比/百分比_mysql 查询占比

- 5Git清除指定文件cached_git cache

- 6全国职业院校技能大赛 GZ037工业互联网集成应用赛项 赛题9_广西职业院校技能大赛 工业互联网集成应用

- 7什么是MySQL的预编译?_mysql预编译

- 8docker安装Homeassist

- 92019年上半年软考信息安全工程师上午真题及答案解析_我国sm3算法被采纳为新一代宽带无线移动通信系统 (lte) 国际标准

- 10用AI給人生開掛的正確方式: AI比人进化快的时代,學什麼才不落伍?

当前位置: article > 正文

第55篇:创建Nios II工程之Hello_World<一>

作者:Monodyee | 2024-04-25 08:54:57

赞

踩

第55篇:创建Nios II工程之Hello_World<一>

Q:本期我们开始介绍创建Platform Designer系统,并设计基于Nios II Processor的Hello_world工程。

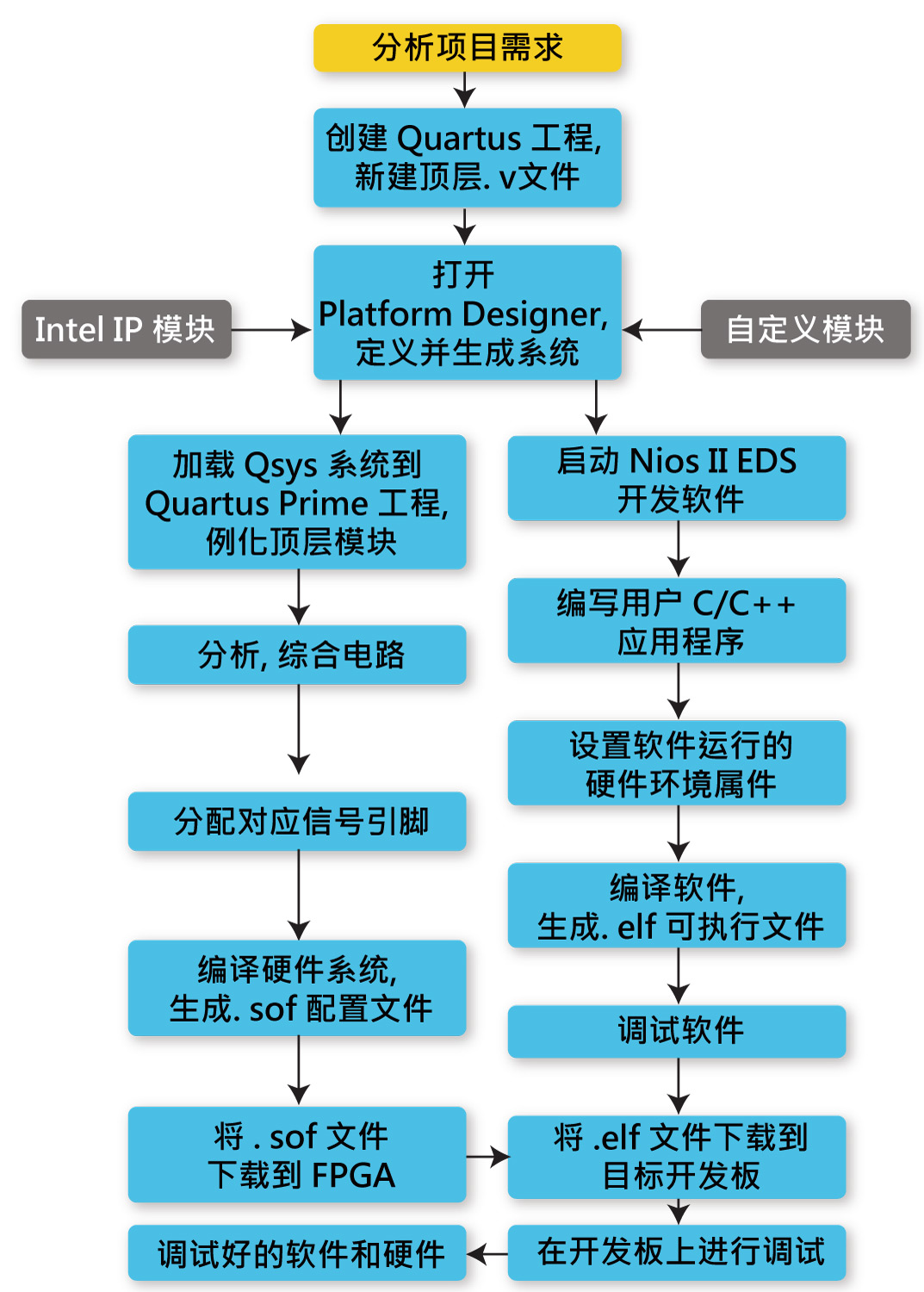

A:设计流程和实验原理:需要用到的IP组件有Clock Source、Nios II Processor、On-Chip Memory、JTAG UART和System ID外设。Nios II Processor是整个系统的核心,其他组件都会通过Avalon总线连接到这个系统核心上,关于Nios II处理器的详细说明和用法可参考Nios II Processor Reference Guide。基于Nios II Processor的设计开发流程:

On-Chip Memory用来控制和分配片上存储资源;JTAG UART是PC与FPGA通信的控制台,PC可以将数据通过JTAG传输到FPGA,也能将FPGA产生的数据回传到PC;

然后需要分别用Quartus软件完成系统的硬件设计部分,生成硬件部分的可配置文件(.sof);

在Nios SBT中完成软件设计部分(用printf函数打印出“Hello_World from Nios II!”字符),生成可执行程序(hello_world.elf),最终系统将“ Hello_World from Nios II! ”字符串通过JTAG UART传输到PC并显示在Nios II Console终端。

本文内容由网友自发贡献,转载请注明出处:https://www.wpsshop.cn/w/Monodyee/article/detail/484383

推荐阅读

相关标签