- 123种Java设计模式

- 22024中国AIGC广告营销产业全景报告

- 3软考高项-信息网络安全模拟题_公钥基础设施(pki)也称公开密钥基础设施。以下不属于pki的组成的是()

- 4micromamba快速安装(windows版本)_windows mamba

- 5上海市计算机学会竞赛平台2021年5月月赛丙组数球数_上海计算机学会竞赛平台五月竞赛题解

- 6抖音seo源码,抖音seo优化系统技术一手源头搭建开发_抖音权重查询网站源码

- 746.整理华子面经+笔试+排序算法_华子面试

- 8【C语言数据结构】双向循环链表_c语言双向循环链表

- 9Wireshark抓包——TCP协议分析_wireshark tcp

- 10十二个常见的Web安全漏洞总结及防范措施_web应用常见漏洞

DFi频率比系统中 DDR 控制器的行为模型_ddr dfi

赞

踩

一、背景:

长期以来,内存控制器 (MC) 的设计及其与系统的集成一直给工程师和系统架构师带来艰巨的挑战。内存控制器和 PHY 之间的互操作性就是这样一个挑战。DFi™ 是一种标准,可确保 DDR MC 和 DDR PHY 在目标匹配频率和频率比下的兼容性。

在频率比系统中,MC 以 PHY 频率的一半速率或四分之一速率运行。因此,对于非相位操作,DFi™ 信号之间的时序关系只能以 PHY 时钟的 2 倍或 4 倍表示。对于分阶段操作,专用总线允许建立 2 倍或 4 倍 PHY 时钟以外的时序关系。

相位信息由 MC 编码并作为“N 相位”信号发出。PHY对“N相位”信号进行解码,以生成所需的定时信号,并将其用于进一步的操作。

DFi™ 规范未指定任何相位编码和交换格式。这留给实现。该文提出一种相位编码算法,用于在DFi™频比系统中MC与PHY建立所需的时序关系。这种方法的区别在于,MC和PHY之间相位关系的整个实现被简化为一个简单的数学方程式。

一、概述

本文详细介绍了DFi™频比系统中的DDR MC相位编码算法。它面向有兴趣了解 DDR MC 如何在特定相位总线中对 PHY 时序信息进行编码的技术受众。请参阅 DFi™ 3.1 规范,了解有关频率比系统的完整详细信息。

DFi™ 是普遍存在的行业规范,它定义了 DDR 内存控制器和 PHY 之间的接口协议。(文末有官方DFI协议文档链接,需要自己下载)它支持开发支持最新 DRAM 标准的片上系统 (SoC)。从所有频比系统的 MC 角度理解 DFi™ 可以简化协议验证组件的开发。

在DFi™频比系统中,相位是一个重要的概念,它有助于DDR-MC将定时参数传达给DDR-PHY。然而,频率比系统的DDR MC相位编码算法不在规范中。尽管该算法是特定于实现的,但了解 MC 相位编码算法对于有效理解 MC 的控制结构非常重要。

现有的相位编码算法是特定于设计实现的,因此很少公开。作为设计验证工程师,您可以参考本文中介绍的方法来验证符合 DFi™ 标准的 DDR-MC 的相位编码功能。该算法显著提高了工程师开发验证组件的效率。

这种方法的关键组成部分是两个不同系统发挥作用的机制的泛化。以下各节详细介绍了以下提到的方面。

- DFI 的频率比

- 频率比时钟定义

- 频率比系统中的写入和读取数据接口

- 编码时序关系参数

- 结论和相关工作。

二、协议

1、DFi频率比

DFI 在 MC 到 PHY 边界处定义,因此在 MC 的时钟频域中工作。 MC 时钟始终是 DFI 时钟,所有 DFI 信号均以 MC 时钟为参考。 在 DDR 内存子系统中,以比 MC 更高的频率操作 PHY 可能会更有利。 如果 PHY 以 MC 频率的倍数运行,则 PHY 以相对于 DFI 时钟更高的数据速率传输数据,并且 MC 可以选择在单个 DFI 时钟周期内执行多个命令。

DFI 规范支持 1:2 或 1:4 MC 与 PHY 频率比,定义 MC 和 PHY 参考时钟的关系。

如果信号参考 DFI 时钟的上升沿并且时钟相位对齐,则可以在 DFI PHY 时钟上发送或接收 DFI 信号。 MC 通过 dfi_freq_ratio 信号将频率比设置传达给 PHY。 仅使用此频率比协议的设备需要此信号。

2、频率比时钟定义

DFI 时钟和 DFI PHY 时钟必须相位对齐,并且相对于彼此的频率比为 1:2 或 1:4。一些从 MC 到 PHY 的 DFI 信号必须参考 DFI PHY 时钟来传达有关信号的信息,以保持正确的定时信息。因此,DFI PHY 时钟以相位来描述,其中系统的时钟相位数是 DFI PHY 时钟与 DFI 时钟的比值。

图1 频率比 1:2 相位定义

图2 频率比 1:4 相位定义

3、与频率比系统的接口信号

写入数据和读取数据信号按相位定义,所有信号时序均参考 DFI 时钟。PHY 必须考虑基于 DFI 时钟的任何断言。由 PHY 驱动的任何信号只能在 DFI PHY 时钟的第 0 阶段发生变化,以允许 MC 捕获完整的 DFI 时钟来捕获信号变化。

DFI 规范支持在 DFI PHY 时钟的每个相位上发送唯一命令的能力。为了将此信息传达给 PHY,DFI 规范以矢量格式定义了频率比系统的命令。PHY 必须维护此信息,以保留命令和数据之间的时序关系。因此,对于频率比系统,控制信号接口、写入数据接口和读取数据使能信号都以“_pN”为后缀,其中N是相数。例如,对于 1:2 频率比系统,有 2 个信号:dfi_address_p0 和 dfi_address_p1,而不是单个dfi_address信号。读取数据信号、读取数据有效和读取数据无效信号以“_wN”为后缀,其中 N 是 DFI 数据字。

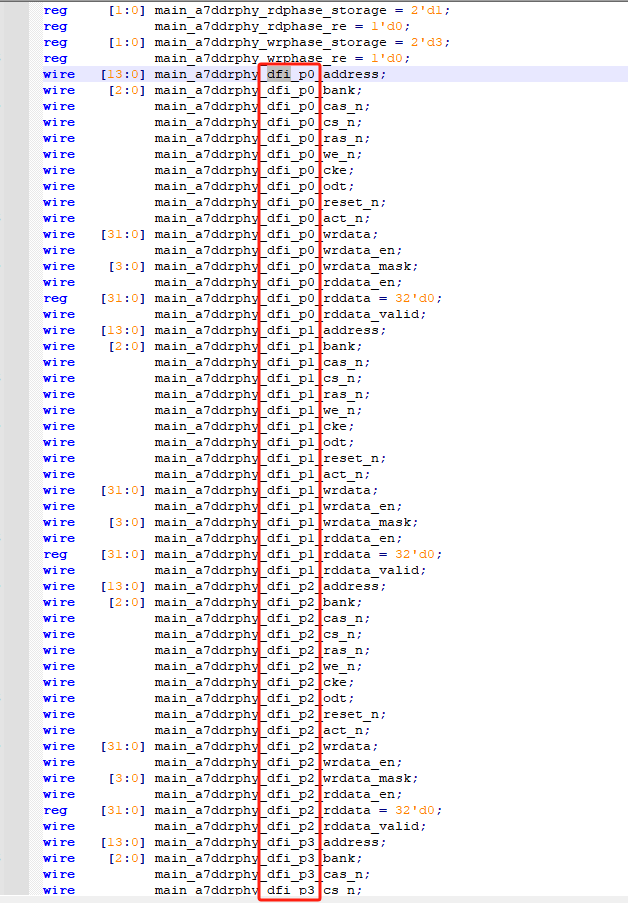

实际代码举例:

我这里是使用1:4,所以是P0,P1,P2,P3。

4、在频率比系统中写入数据接口

写入数据使能信号 (dfi_wrdata_en_pN) 向 PHY 指示有效dfi_wrdata将在Tphy_wrdata周期内传输,其宽度定义了写入的数据相数。为了将此信息传达给 PHY,必须在信号中对相位信息进行编码。因此,该信号也根据频率比被矢量化为多个信号。与 DFI 命令类似,每个信号都与 DFI PHY 时钟的一个相位相关联。

5、频率比系统中的读取数据接口

与写入数据使能信号类似,读取数据使能信号 (dfi_rddata_en_pN) 定义读取命令和读取数据之间的时钟数,其宽度定义读取的数据相数。每当读取数据可用时,PHY 都会将读取数据发送到dfi_rddata_wN总线上的 MC,置位相关的dfi_rddata_valid_wN信号以通知 MC 哪些总线包含有效数据。与与DFI PHY时钟相位相关的读取数据使能信号不同,读取数据、读取数据有效和读取数据无效信号均以DFI数据字后缀为矢量。

6、编码时序关系参数

由于 1:2 频率比系统中的最大相数是 2,我们可以表示以 2 为底数的数系统(相位 0 和相位 1)中的“相位 N”。同样,1:4 频率比系统中的最大相数为 4 。因此,我们可以表示以 4 为底数的数系中的“N 相位”(相位 0、相位 1、相位 2、相位 3)。这处理了 DFI 指定的轮换顺序规则。

示例使用可以看第3点。

(a) 如果命令在阶段 0 上驱动,则 N = 0 且 N+1 = 1 和 ((N+1) +1) = 0,依此类推。

(b) 如果命令在第 1 阶段驱动,则 N = 1 且 N+1 = 0 和 ((N+1) +1) = 1 等。

表 1: 频率比系统的余数

| 频率比 | 余数(R1) | 余数(R2) |

|---|---|---|

| 1:2 | mod (Tphy_wrlat /2) | mod (Tphy_wrdata, 2) |

| 1:4 | mod (Tphy_wrlat /4) | mod (Tphy_wrdata, 4) |

表 2:频率比系统的商

| 频率比 | 商数(Q1) | 商数(Q2) |

|---|---|---|

| 1:2 | floor(Tphy_wrlat /2) | floor(Tphy_wrdata /2) |

| 1:4 | floor(Tphy_wrlat /4) | floor(Tphy_wrdata /4) |

在表 1 中,R1 和 R2 表示在 1:2 和 1:4 频率比系统中将 PHY 延迟分别除以 2 和 4 时的余数。

在表 2 中,Q1 和 Q2 表示在 1:2 和 1:4 频率比系统中,PHY 延迟分别除以 2 和 4 时的商。

(R1! =0)?(S=1) :(S=0) (1)

(R2! =0)?(T=1) :(T=0) (2)

从等式“(1)”和“(2)”中,S表示在1:2和1:4频率比系统中Tphy_wrlat分别被2和4整除。R 表示在 1:2 和 1:4 频率比系统中,Tphy_wrdata 分别被 2 和 4 整除。

7、编码时序关系流程图

图 3 表示 1:2 频率比系统的相位编码算法。它解释了如何根据 PHY 支持的延迟来断言 dfi_wrdata_en_pN 和 dfi_rddata_en_pN 信号,以用于到达不同相位的命令。它还解释了如何在遵循旋转顺序规则的特定相位数据总线中对各种数据字之间的时序关系进行编码。

表 3 显示了在特定相位总线中发出命令后置位使能的 DFI 时钟。

表 3:使能信号的时序关系

| S | T | T_en |

|---|---|---|

| 0 | 0 | Q1 |

| 0 | 1 | Q1 |

| 1 | 0 | Q1+S |

| 1 | 1 | Q1+S |

表 4 显示了根据 S 和 T 的值在特定相位总线中置位使能后驱动数据字的 DFI 时钟。

表 4:数据字的时序关系

| S | T | T_en |

|---|---|---|

| 0 | 0 | Q2+T |

| 0 | 1 | Q2+T |

| 1 | 0 | Q2+¯T |

| 1 | 1 | Q2+T |

从表 3 中,我们得到

T_en = Q1+S (3)

从表 4 中,我们得到

T_data = Q2+¯S T+S (4)

图3 1:2频比系统的相位编码算法流程图

从等式“(3)”和“(4)”中,我们可以建立使能信号和数据信号之间的时序关系。

表 5 显示了 1:2 频率比系统的 MC 编码算法的数学推导。_pN 表示驱动命令的特定于相位的总线。

表6显示了在1:4和1:2频率比系统中,通过结合“(R1-S)”和“(R2-T)”因子推广的结果。这些因素不会影响 1:2 频域中的相位编码。

表 5:1:2 频率比系统的 MC 编码

| dfi_wrdata_en / dfi_rddata_en | dfi_wrdata / dfi_rddata_valid/dfi_rddata |

|---|---|

| _pN asserted @T_en DFi clock cycles after command. | _pN to _p[N+S*T] asserted @T_data DFi clock cycles from assertion of the first enable. |

| Remaining _pN asserted @Q1 DFi clock cycles after command. | Remaining _pN (if any) asserted @ Q2 after assertion of first enable. |

表 6:全频比系统的 MC 编码

| dfi_wrdata_en / dfi_rddata_en | dfi_wrdata/dfi_rddata_valid / dfi_rddata |

|---|---|

| _pN to _p[N+(R1 - S)] asserted @T_en DFi clock cycles after command. | _pN to _p[N+(R2-T)+S*T] asserted @T_data DFi clock cycles from assertion of the first enable. |

| Remaining _pN asserted @Q1 DFi clock cycles after command. | Remaining _pN (if any) asserted @Q2 DFi after assertion of first enable. |

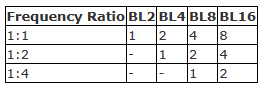

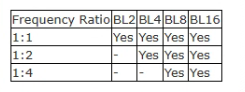

表 7 显示了 DDR-MC 侧各种突发长度必须置位 dfi_*_en_pN 的最小 DFI 时钟数。

表 7:各种突发长度的使能信号需要时间

三、示例

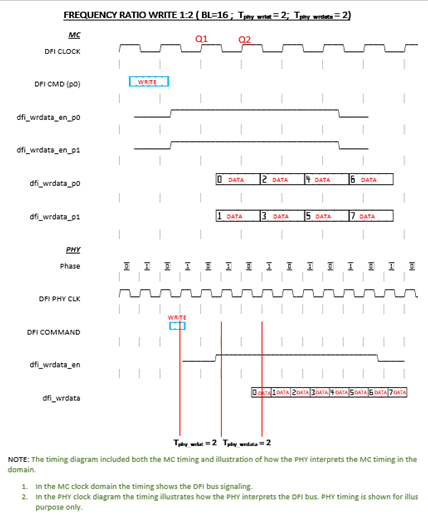

1. Tphy_wrlat = 2; Tphy_wrdata = 2

图 4 显示了一个 1:2 频率比的单次写入命令,其数据字的突发长度为 16

假设 Tphy_wrlat = 2;Tphy_wrdata = 2,MC 打算传输突发长度为 16 的数据字。让我们假设 WRITE 命令是在 DFI 命令总线的第 0 阶段发出的。

由于 Tphy_wrlat 可以被 2 整除,参数 S(等于 0)对 dfi_wrdata_en_pN 的编码没有影响。MC 在 WRITE 命令之后在 Q1 DFI 时钟处置位 dfi_wrdata_en_p0 和 dfi_wrdata_en_p1。

由于 Tphy_wrdata 可以被 2 整除,参数 S(等于 0)和 T(等于 0)对 dfi_wrdata_pN 的编码没有影响。第一个数据字 (D0) 和下一个数据字 (D1) 分别在 dfi_wrdata_p0 和 dfi_wrdata_p1 中驱动,在 Q2 DFI 时钟周期后从 dfi_wrdata_en_p0 的断言开始。后续数据字(D2、D3、D4、D5、D6 和 D7)在后续阶段(p0、p1、p0…等)在以下时钟边沿中。

图4 1:2频率比的单次读取,同时使用偶数的 Tphy_wrlat 和偶数的 Tphy_wrdata

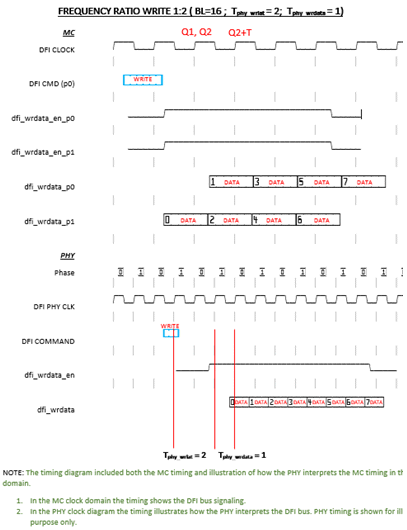

2. Tphy_wrlat = 2; Tphy_wrdata = 1

图 5 显示了一个 1:2 频率比的单次写入命令,其突发长度为 16 的数据字。

假设 Tphy_wrlat = 2;Tphy_wrdata = 1,MC 打算传输突发长度为 16 的数据字。让我们假设 WRITE 命令是在 DFI 命令总线的第 0 阶段发出的。

由于 Tphy_wrlat 可以被 2 整除,参数 S(等于 0)对 dfi_wrdata_en_pN 的编码没有影响。MC 按照 WRITE 命令在 Q1 DFI 时钟处置位 dfi_wrdata_en_p0 和 dfi_wrdata_en_p1

由于Tphy_wrlat能被2整除,而Tphy_wrdata不能被2整除,Tphy_wrdata编码只受参数T(等于1)的影响。MC在第一个dfi_wrdata_en_pN置位后dfi_wrdata_p1在Q2 DFI时钟驱动总线中的第一个数据字(D0),在第一个dfi_wrdata_en_pN置位后,在(Q2+T)DFI时钟驱动dfi_wrdata_p0总线中的下一个数据字(D1)。后续数据字(D2、D3、D4、D5、D6 和 D7)在后续阶段(p0、p1、p0…等)在以下时钟边沿中。

图5 1:2频率比的单次读取,同时使用偶数的 Tphy_wrlat 和奇数的 Tphy_wrdata

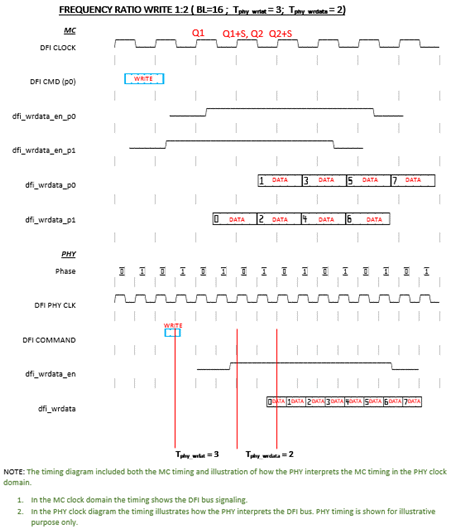

3、Tphy_wrlat = 3; Tphy_wrdata = 2

图 6 显示了一个 1:2 频率比单次写入命令,其突发长度为数据字 16

假设 Tphy_wrlat = 3;Tphy_wrdata = 2,MC 打算传输突发长度为 16 的数据字。让我们假设 WRITE 命令是在 DFI 命令总线的第 0 阶段发出的。

由于 Tphy_wrlat 不能被 2 整除,参数 S(等于 1)对 dfi_wrdata_en_pN 的编码有一定的影响。MC 在 Q1 DFI 时钟上置位dfi_wrdata_en_p1,并在 (Q1+S) DFI 时钟处dfi_wrdata_en_p0 WRITE 命令。

由于Tphy_wrlat不能被2整除,而Tphy_wrdata能被2整除,Tphy_wrdata编码只受参数S的影响。MC 在第一个dfi_wrdata_en_pN置位后dfi_wrdata_p1 Q2 DFI 时钟驱动总线中的第一个数据字 (D0),在第一个dfi_wrdata_en_pN置位后,在 (Q2+S) DFI 时钟驱动dfi_wrdata_p0总线中的下一个数据字 (D1)。后续数据字(D2、D3、D4、D5、D6 和 D7)以增量方式放置在后续时钟边沿的后续相位中。

图6 1:2频率比单读,奇Tphy_wrlat和偶Tphy_wrdata

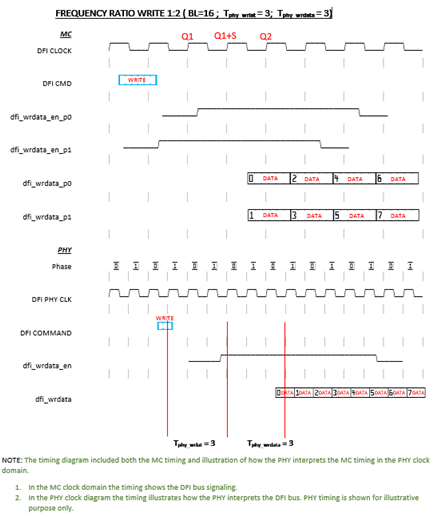

4、Tphy_wrlat = 3;Tphy_wrdata = 3

图 7 显示了一个 1:2 频率比的单次写入命令,其突发长度为 16 的数据字。

假设 Tphy_wrlat = 3;Tphy_wrdata = 3,MC 打算传输突发长度为 16 的数据字。让我们假设 WRITE 命令是在 DFI 命令总线的第 0 阶段发出的。

由于 Tphy_wrlat 不能被 2 整除,参数 S(等于 1)对 dfi_wrdata_en_pN 的编码有一定的影响。MC 在 Q1 DFI 时钟上置位dfi_wrdata_en_p1,并在 (Q1+S) DFI 时钟处dfi_wrdata_en_p0 WRITE 命令。

由于 Tphy_wrlat 不能被 2 整除,而 Tphy_wrdata 也不能被 2 整除,Tphy_wrdata编码会受到参数 S(等于 1)和参数 T(等于 1)的影响。MC在第一个dfi_wrdata_en_pN置位后,分别以(Q2+S)的DFI时钟驱动dfi_wrdata_p0总线和dfi_wrdata_p1总线中的第一个数据字(D0)和第二个数据字(D1)。后续数据字(D2、D3、D4、D5、D6 和 D7)以增量方式放置在后续时钟边沿的后续相位中。

图7 1:2频率比单读,奇Tphy_wrlat和奇Tphy_wrdata

四、注意

此算法不能应用于不属于表 8 所示类别的系统。许多 DFI 系统不需要支持不是频率比倍数的突发传输。例如,使用 4:1 频率系统时,在 2 个 DFI 数据字上传输 4 个 DRAM 字的突发数据。

但是,如果系统确实支持这些突发传输,则 PHY 必须以轮换顺序传输读取的数据。创建一个支持这种组合的系统,即当单次读取的 DFI 读取数据不使用整个 DFI 读取数据接口时,涉及需要考虑的额外复杂性。

表 8:编码算法建议

五、结论

我们在符合DFI标准的DDR内存控制器中提出了一种行为模型相位编码算法。该算法可用于在 RTL 中对 DDR-MC 进行建模。事实证明,该算法有助于在DFi验证环境中从头开始开发各种ASIC验证组件,例如驱动程序、监视器和记分牌,从而减少验证工作。

六、未来工作

我们目前正在将算法扩展到1:2N(N>2)频率比,初步结果令人鼓舞。虽然没有关于大于 1:4 的频率比的讨论。该算法可以扩展到支持更高频率比的未来存储器类型。

七、DFi协议文档

链接:https://pan.baidu.com/s/11PI1W0cVk6SfDdfcLNkGLA?pwd=FBMZ

提取码:FBMZ

–来自百度网盘超级会员V6的分享