- 1数据预处理系列:多重共线性_检测和解决办法_什么数据需要共线性处理

- 2Windows本地部署Fooocus AI绘画工具(小白教程!)_fooocus本地布置

- 3sqlite优化简单分析_sqlite 性能

- 4写python爬虫的第一天,拿百度练手遇到 “ 被反爬遇到<title>百度安全验证</title> ” 的解决方案_被百度反爬

- 5猿编程怎么编程机器人平板:深入探索与实践

- 6【第十届“泰迪杯”数据挖掘挑战赛】B题:电力系统负荷预测分析 Baseline_泰迪杯电力负荷预测

- 7西门子PLC入门-PLC介绍_西门子plc编程软件界面介绍

- 82023社招阿里、腾讯、蚂蚁金服「四面」Java面试真题分享_阿里内部java岗位面试题汇总

- 9getStorageInfoSync和getStorageSync

- 10深入理解二叉树及其在C语言中的实现

University Program VWF仿真步骤__全加器

赞

踩

本教程将以全加器为例,选择DE2-115开发板的Cyclone IV EP4CE115F29C7 FPGA,使用Quartus Lite v18.1,循序渐进的介绍如何创建Quartus工程,并使用Quartus Prime软件的University Program VWF工具创建波形文件,对全加器的功能进行仿真。

使用University Program VWF工具进行仿真,其实也是调用ModelSim软件仿真,只是不用写testbench文件,而是创建波形文件,因此也必须安装ModelSim软件。

一、创建Quartus工程

1、点击Quartus--File--New Project Wizard,一步步创建全加器(full_adder)工程。

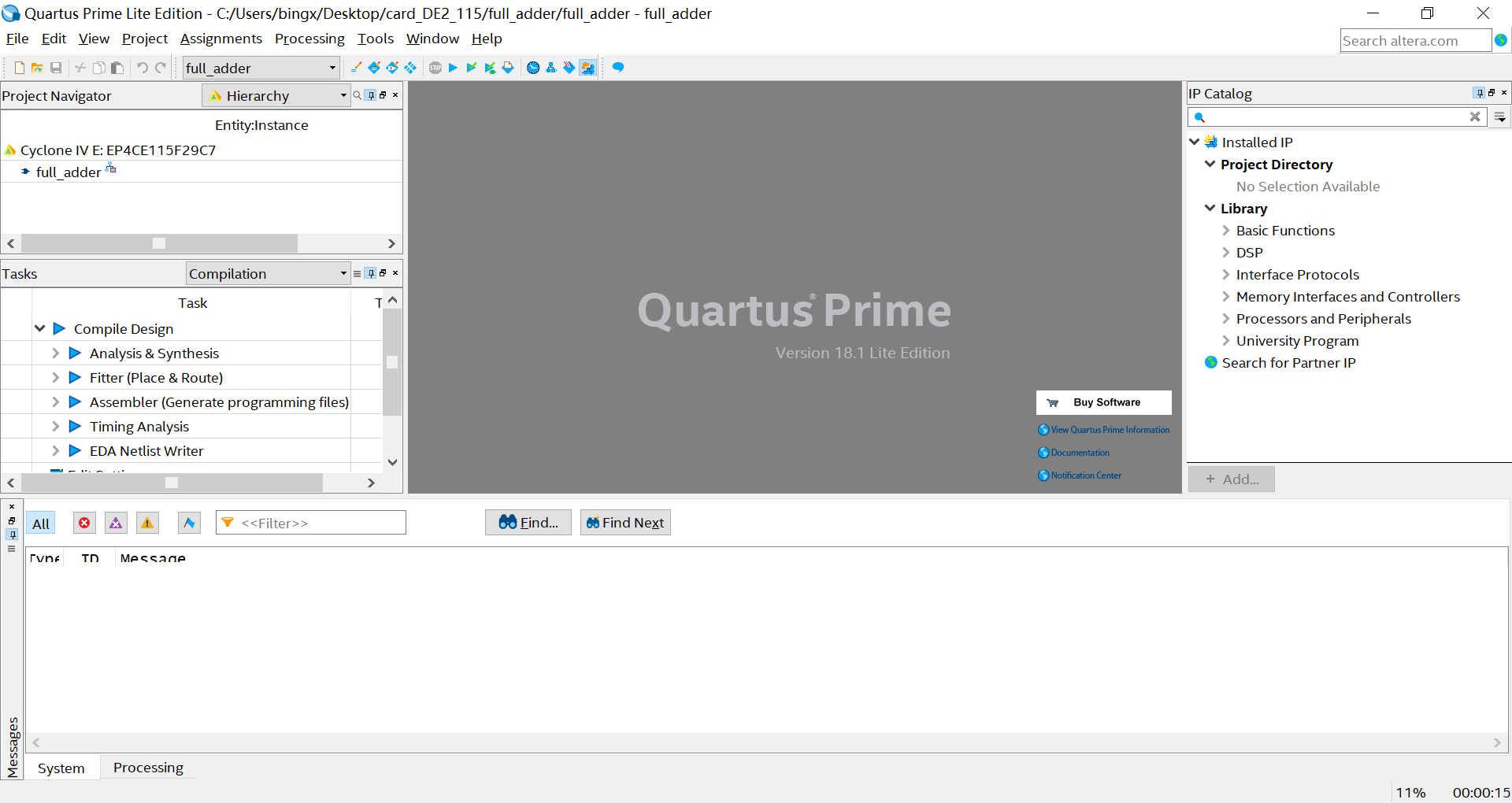

2、打开后的Quartus工程界面如下图所示。

二、创建Verilog模块

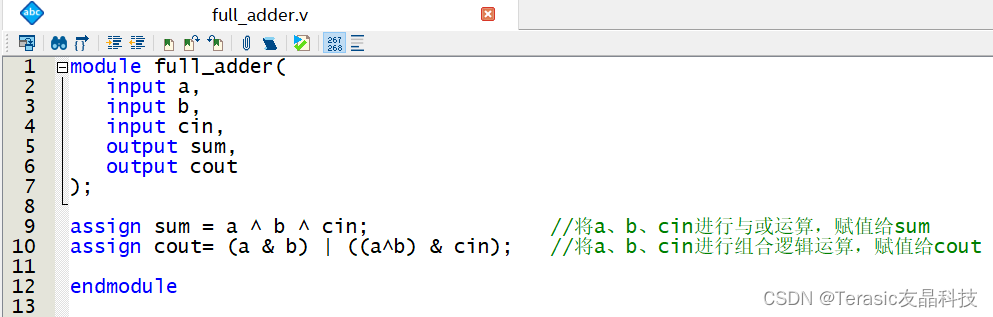

3、点击Quartus-->File-->New-->Verilog HDL,将以下代码复制到.v文件,并保存为full_adder.v。

- module full_adder(

- input a,

- input b,

- input cin,

- output sum,

- output cout

- );

-

- assign sum = a ^ b ^ cin; //将a、b、cin进行与或运算,赋值给sum

- assign cout= (a & b) | ((a^b) & cin); //将a、b、cin进行组合逻辑运算,赋值给cout

-

- endmodule

三、综合与分析Verilog代码

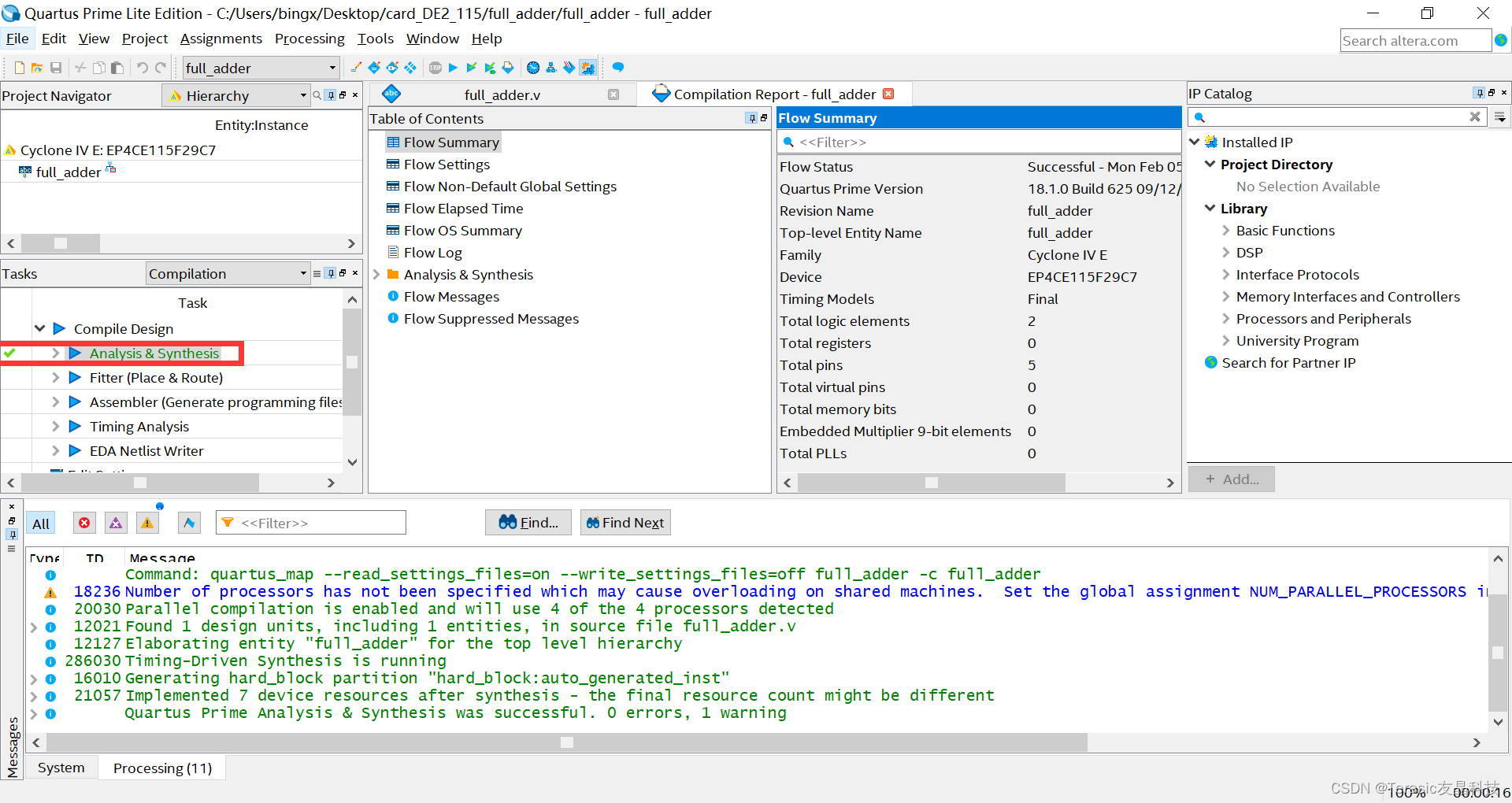

4、点击Quartus软件菜单栏的Processing --> Start --> Start Analysis & Synthesis,对Verilog HDL代码执行语法检查和综合。

如果该过程成功完成,在Quartus软件窗口的Tasks页面中,Analysis & Synthesis旁边将显示一个绿色勾型标记,如下图所示。如果在该过程中提示有错误,请检查Verilog HDL代码语法,确保与上述代码块完全一致。

四、仿真Quartus工程

介绍如何用University Program VWF工具创建vwf波形文件,对全加器的Verilog代码进行功能仿真。

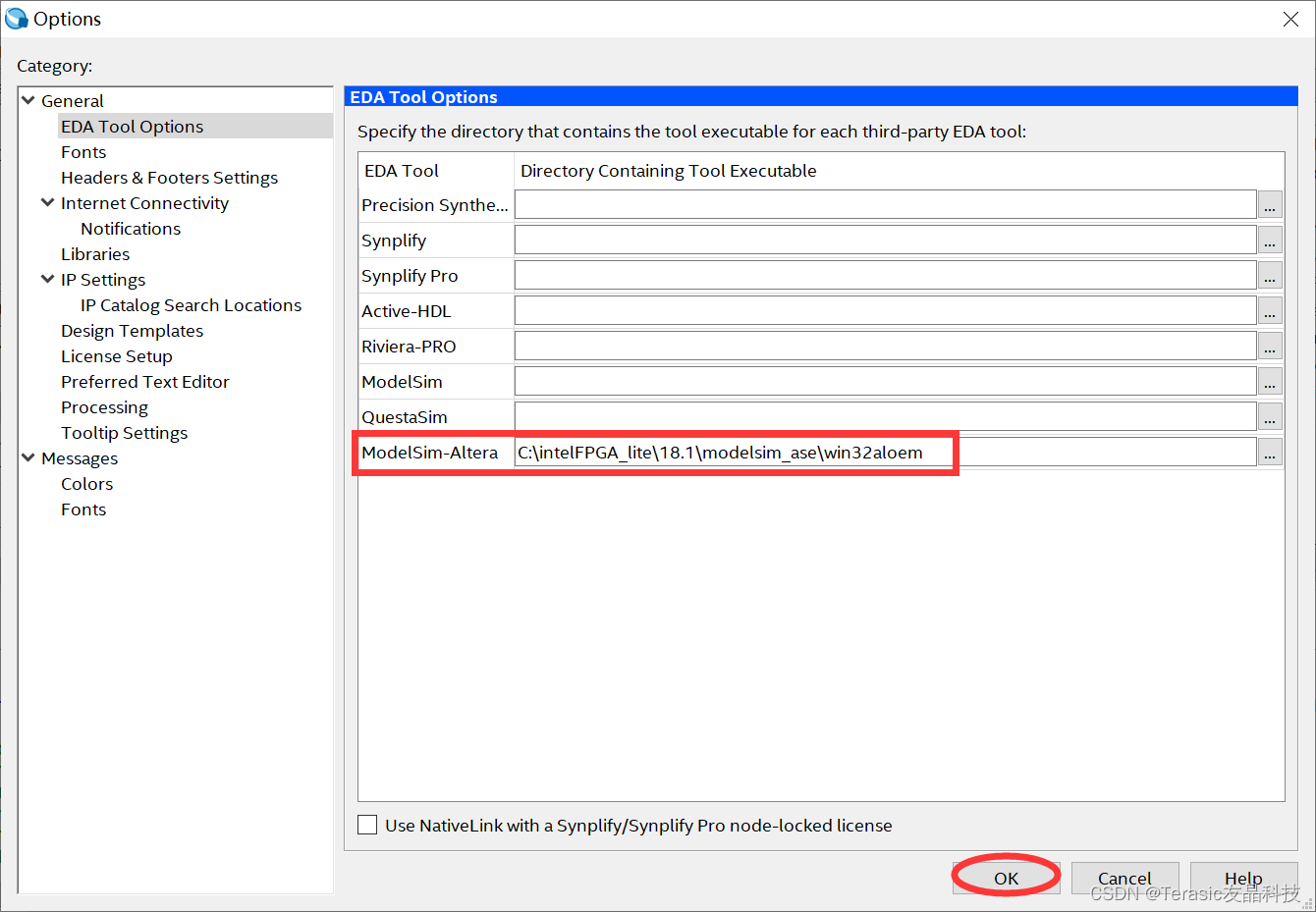

5、点击Quartus软件菜单栏的Tools --> Options,打开Options窗口,选择General中的EDA Tools Options,设置ModelSim-Altera的路径为C:\intelFPGA_lite\18.1\modelsim_ase\win32aloem(注意:这里的路径为Quartus的实际安装路径),点击OK。

6、点击Quartus软件菜单栏的File --> New --> University Program VWF,打开Simulation Waveform Editor窗口。

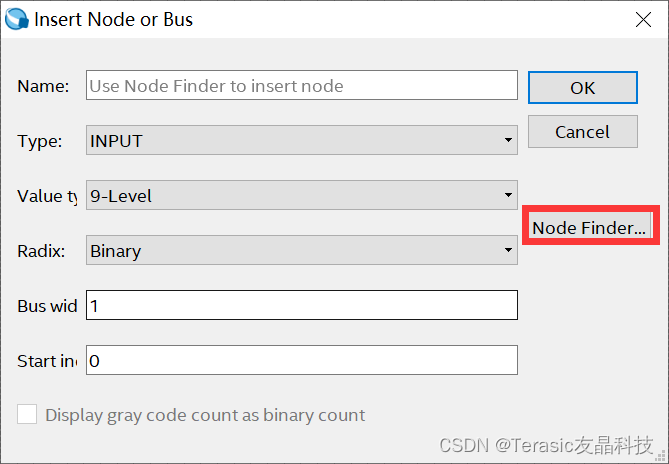

7、点击Simulation Waveform Editor窗口菜单栏的Edit --> Insert --> Insert Node or Bus,打开Insert Node or Bus窗口。

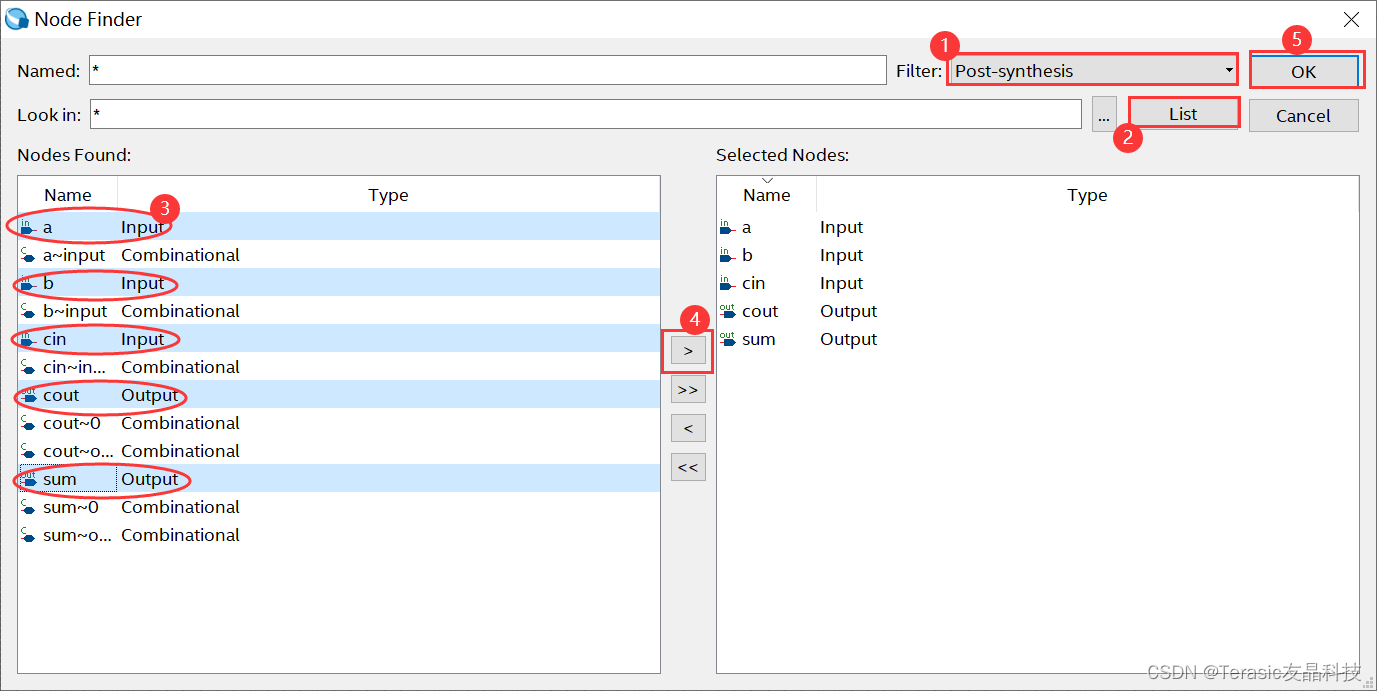

8、点击Node Finder按钮打开Node Finder窗口,按下图序号标注的步骤,添加输入、输出信号节点,最后点击OK按钮。

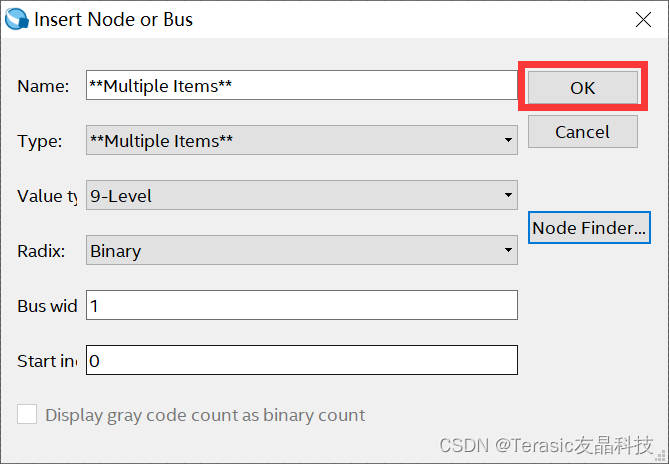

9、返回到Insert Node or Bus窗口,点击OK按钮。

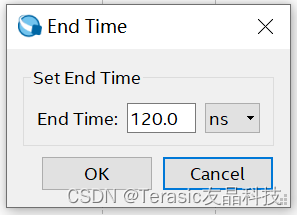

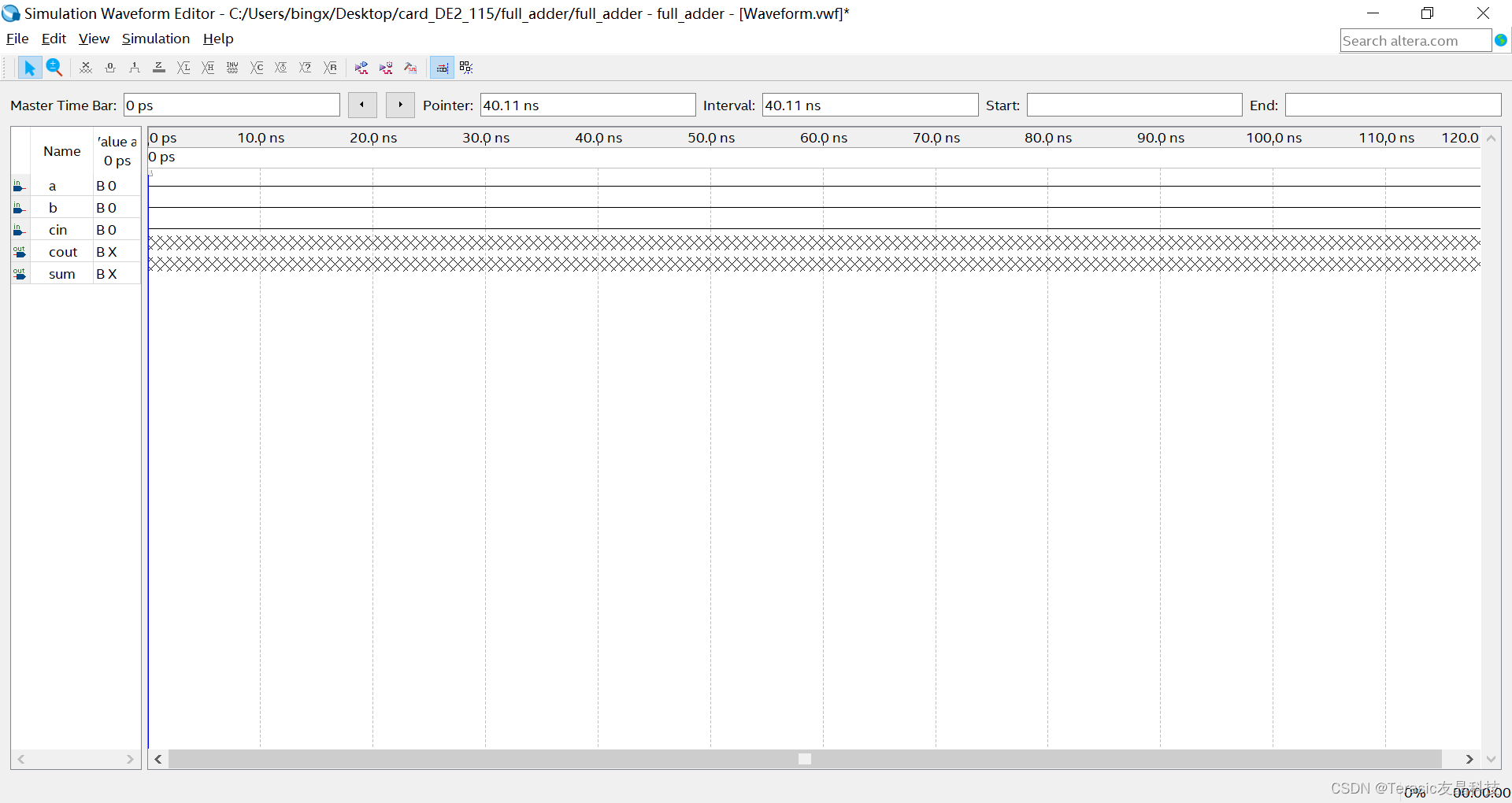

10、点击Simulation Waveform Editor窗口菜单栏的Edit --> Set End Time...,设置结束时间,举例设置为120.0 ns。至此,Simulation Waveform Editor窗口如下图所示。

11、在Simulation Waveform Editor窗口编辑输入信号节点a的值。如下图所示,在输入信号节点的波形区域单击鼠标左键不放并移动鼠标,释放后会看到一段阴影区域,点击Force High (1)按钮可以设置这段区域的信号节点值为1,点击Force Low (0)可以设置值为0;同样的操作可自行再设置b和cin的值。

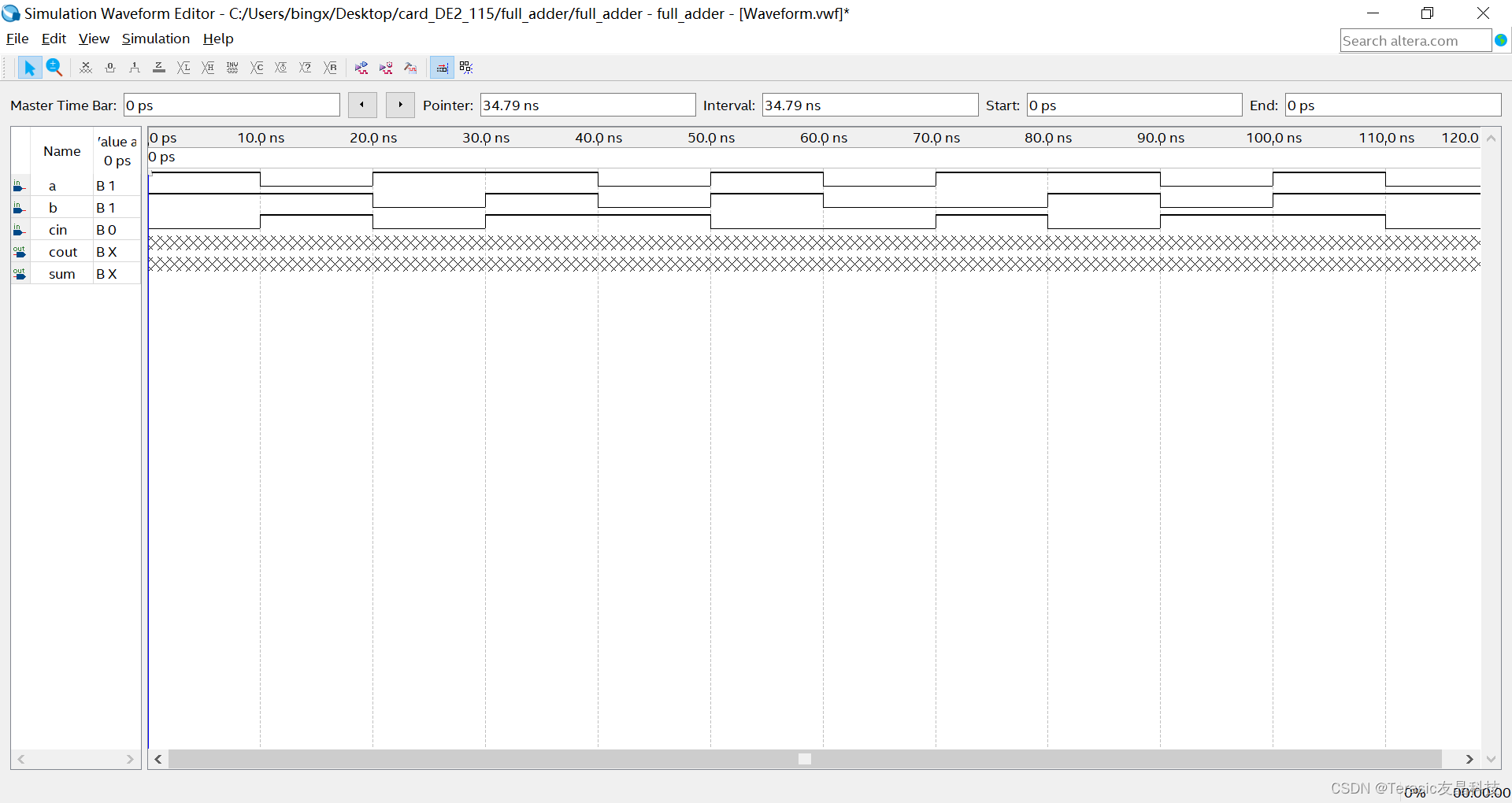

12、下图所示,举例设置了a、b和cin节点的值后的波形图。

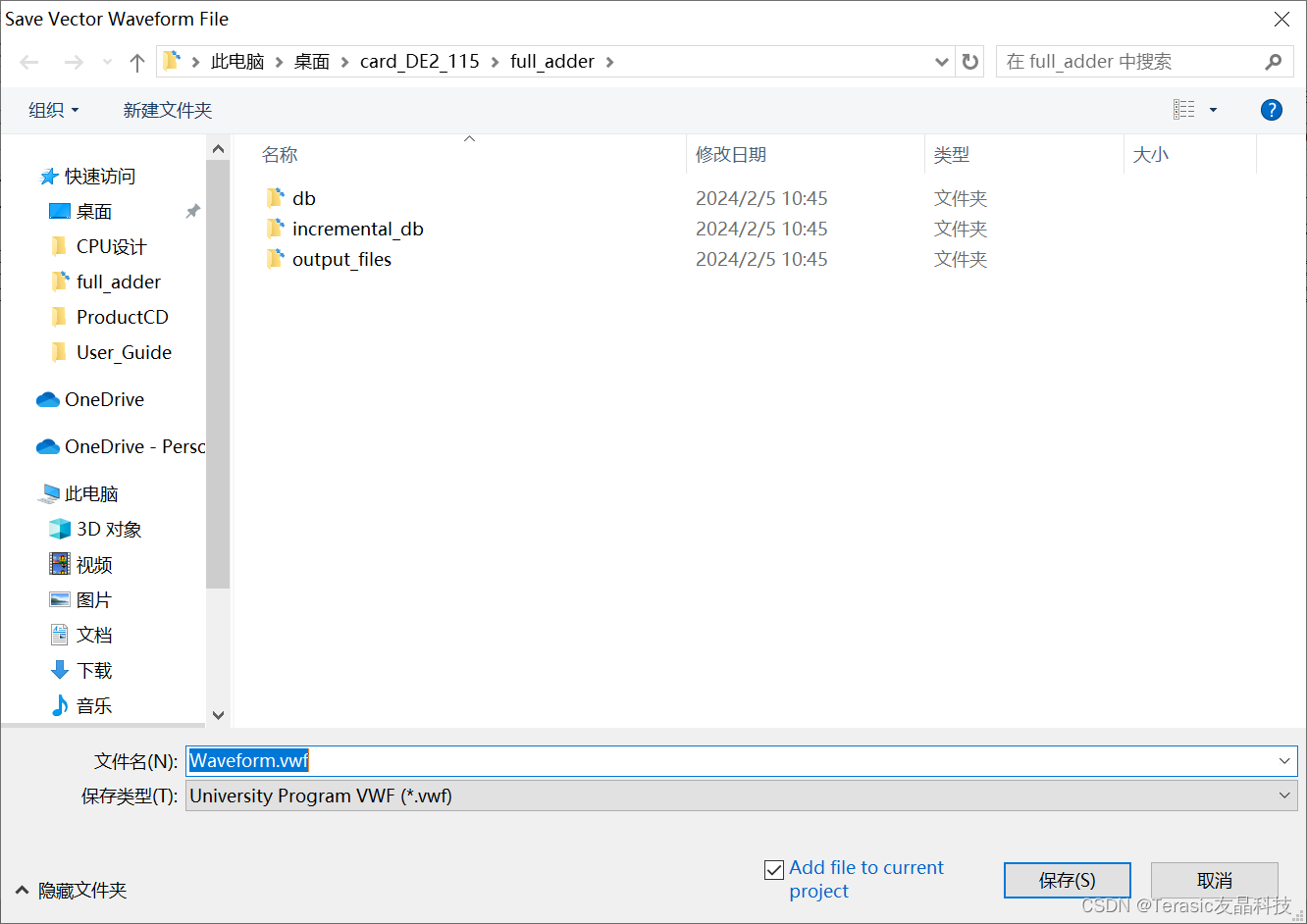

13、点击Simulation Waveform Editor菜单栏的File --> Save,保存文件并保持默认文件名Waveform.vwf不变。

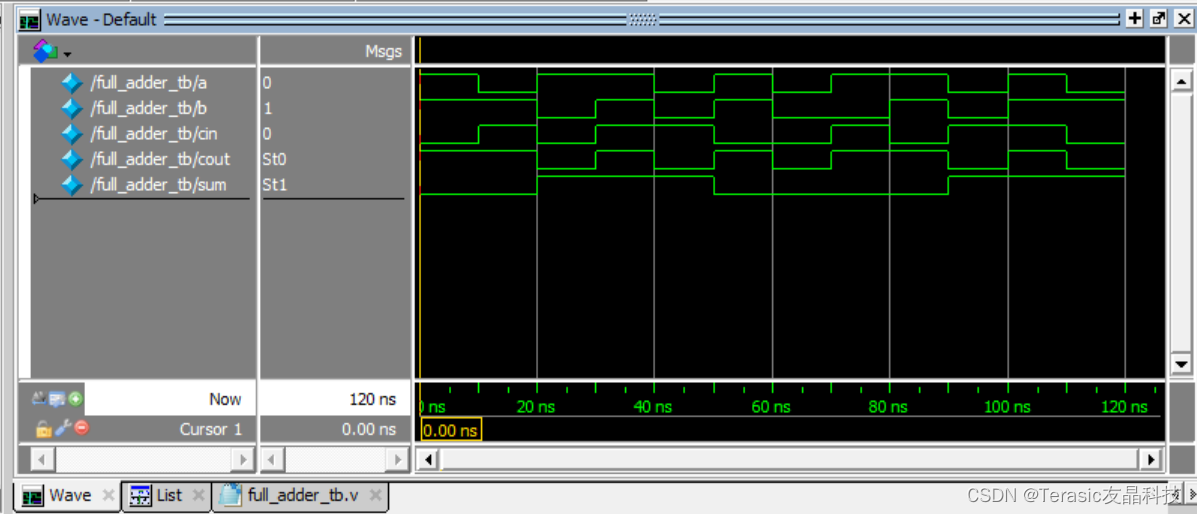

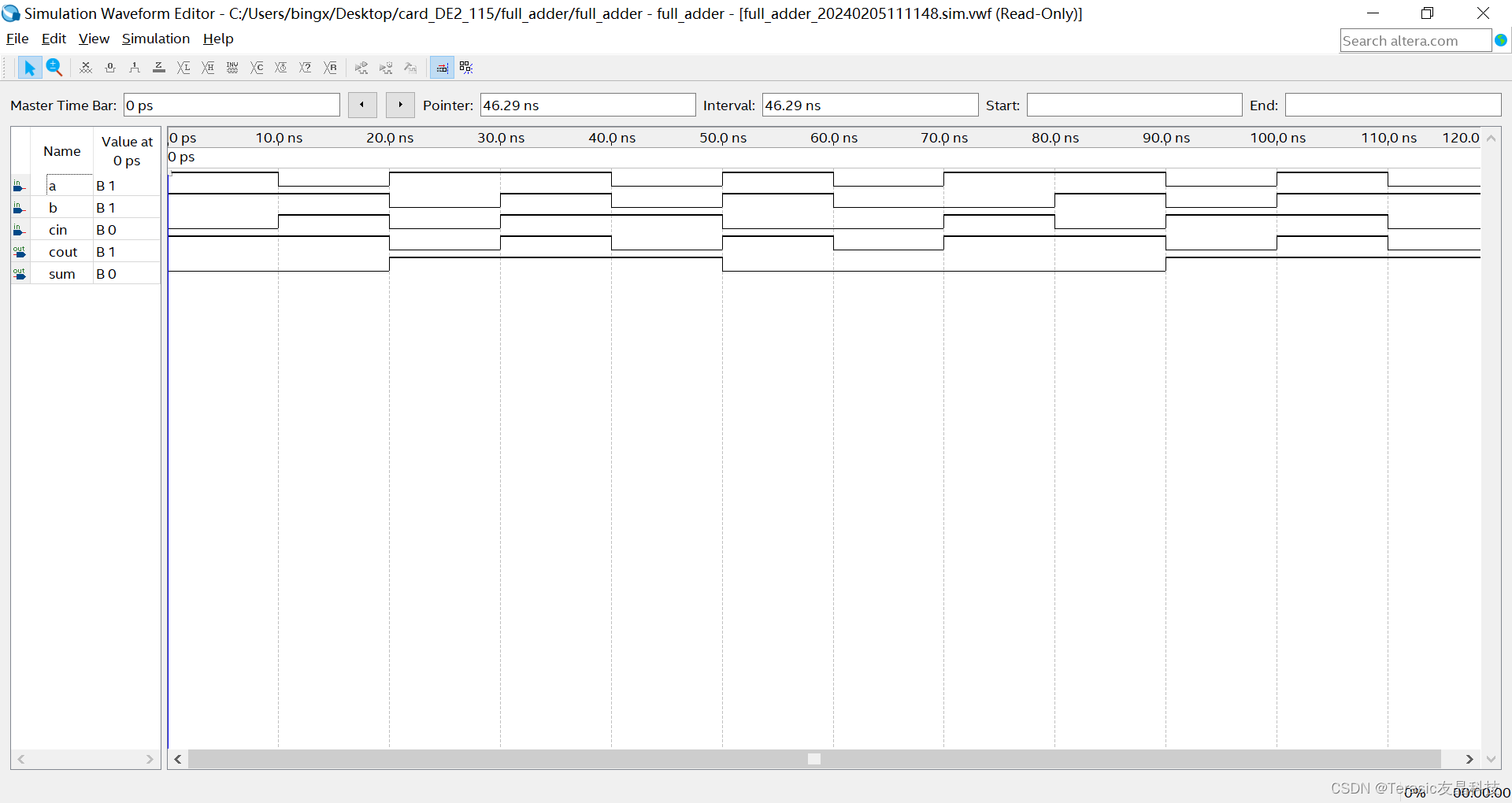

14、点击Simulation Waveform Editor菜单栏中的Simulation --> Run Functional Simulation,开始仿真,仿真后的波形图如下图所示。

五、实验现象与结果分析

仿真结果分析:

-

在0ns~10ns,a=1,b=1,cin=0,此时count=1,sum=0;

-

在10ns~20ns,a=0,b=1,cin=1,此时count=1,sum=0;

-

在20ns~30ns,a=1,b=0,cin=0,此时count=0,sum=1;

-

在30ns~40ns,a=1,b=1,cin=1,此时count=1,sum=1;

-

在40ns~50ns,a=0,b=0,cin=1,此时count=0,sum=1;

依次再分析50ns~120ns,根据结果可判断全加器功能仿真是正确的。

六、生成的Test bench验证

以上在Run Functional Simulation过程中自动生成了与波形文件对应的Test Bench文件,一般在工程的simulation\qsim文件路径里,名称为Waveform.vwf.vt。

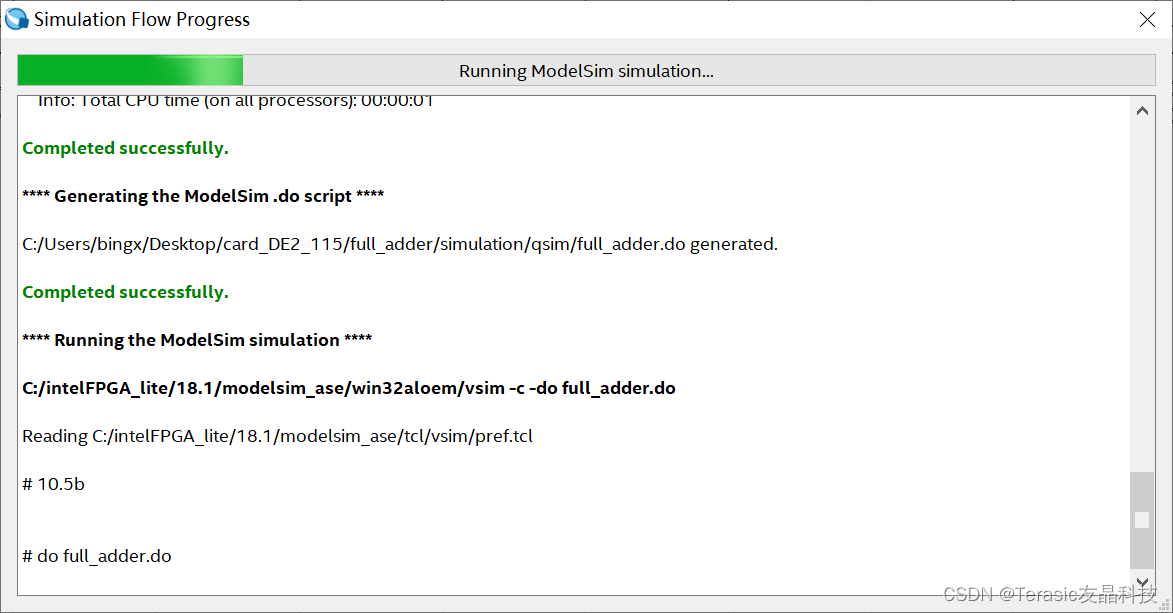

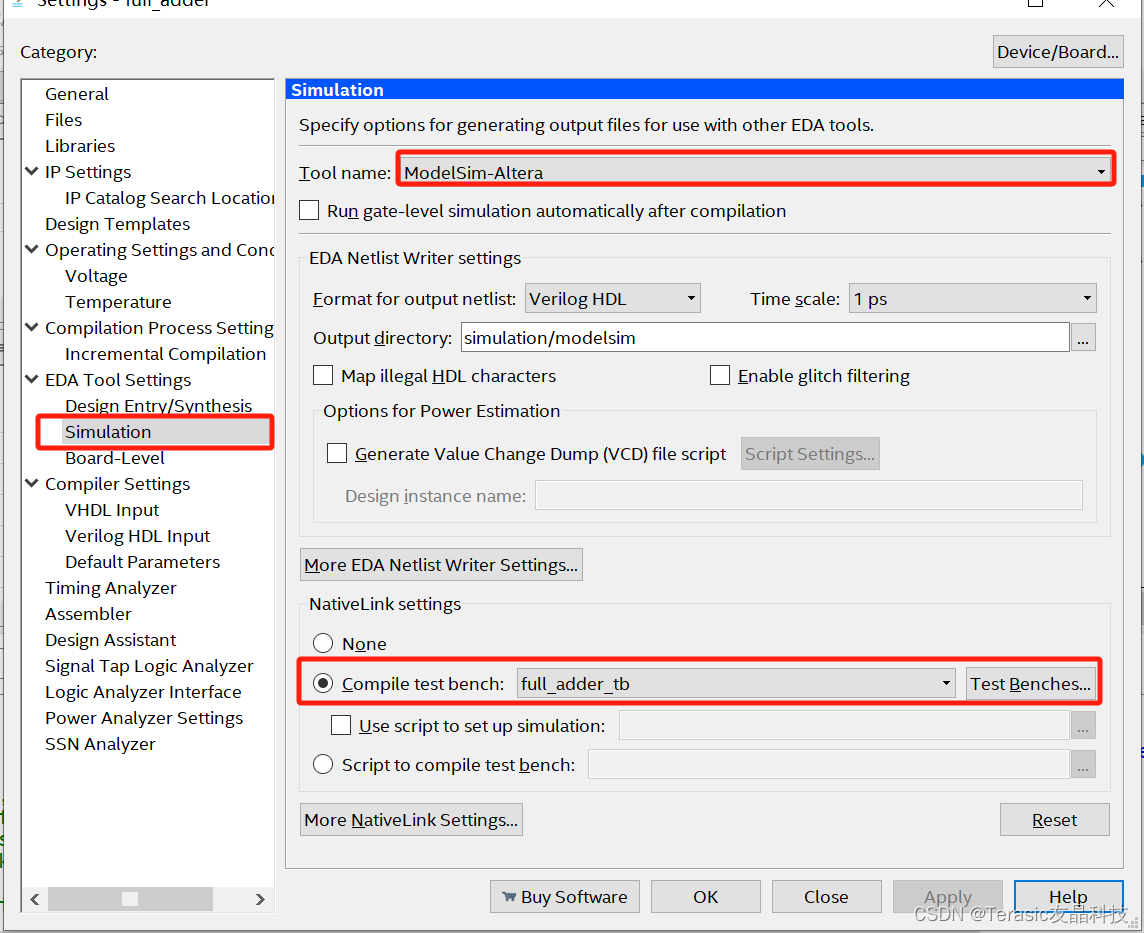

我们可以用该Test Bench文件再进行ModelSim仿真。将Waveform.vwf.vt命名为full_adder_tb,并修改格式为.v,再打开full_adder_tb.v将module名称改为full_adder_tb即可。ModelSim仿真所必须的设置和步骤此处就不再说明。

设置完成后点击Quartus Tools--Run Simulation Tools--RTL Simulation,即可仿真。可以看到仿真波形与以上的仿真波形一致。