热门标签

热门文章

- 1Java哈希表(散列表)解析_java hashtable函数

- 2java redis 面试题_Java面试题(Redis篇)

- 3数据结构——链表的实现(Java版)_java链表结构的实现

- 4使用 Ollama 本地运行各种 LLM_ollama glm4

- 5性能评测系列(PT-013):Spring Boot(K8s多实例) + GaussDB,高并发insert

- 6Python-层次聚类-Hierarchical clustering

- 7C++ 智能指针详解(发展历程,使用,模拟实现)_实现智能指针

- 8elasticsearch之Pipeline&Processor(管道处理数据)_elasticsearch processors

- 9LangChain+Fine-tune实现模型定制化_langchain、fine-tuning

- 10小程序模拟更新微信_微信小程序模拟更新

当前位置: article > 正文

FPGA流水灯闪烁_fpga灯闪烁间隔两秒是多少khz

作者:Monodyee | 2024-06-15 10:54:32

赞

踩

fpga灯闪烁间隔两秒是多少khz

本次设计是基于Xilinx旗下的Artix-7的开发环境下,首先需要设计流水灯的闪烁规则。本次设计采用的开发板只有四个LED灯,所以循环规则应该是0001→0010→0100→1000→0001...1000;本次设计流水灯闪烁为1S一次的间隔,由这些条件可以先进行模块的设计。

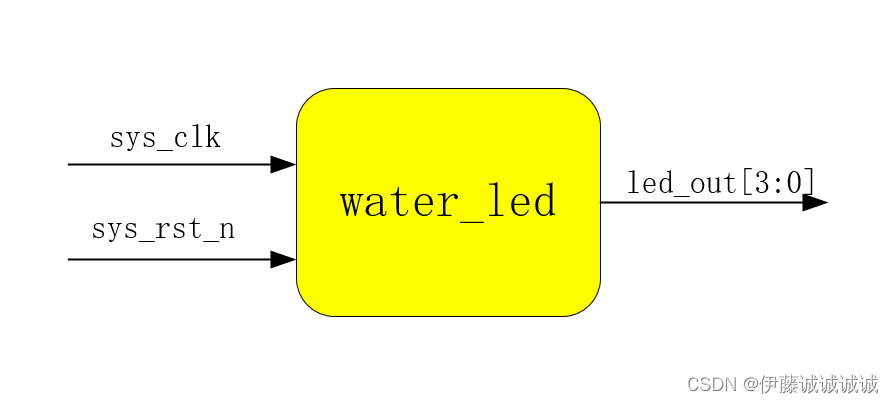

LED流水灯基本面板如下:

由上图模块可以知道,模块有两路输入一路输出,根据这个模块可以进行波形的绘制

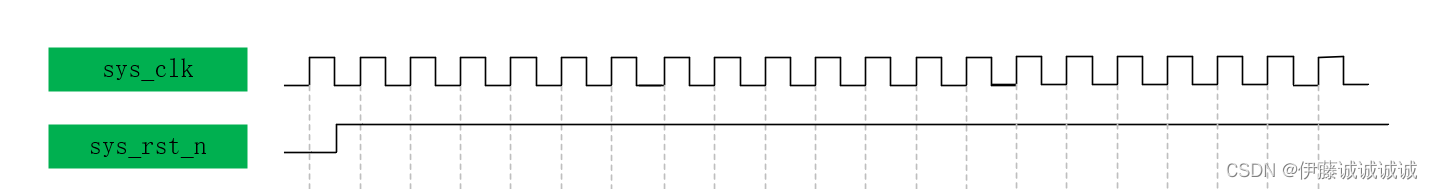

首先是时钟和复位的波形图

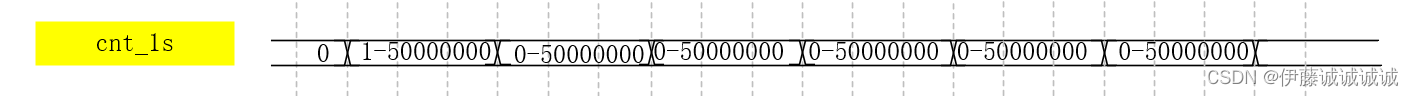

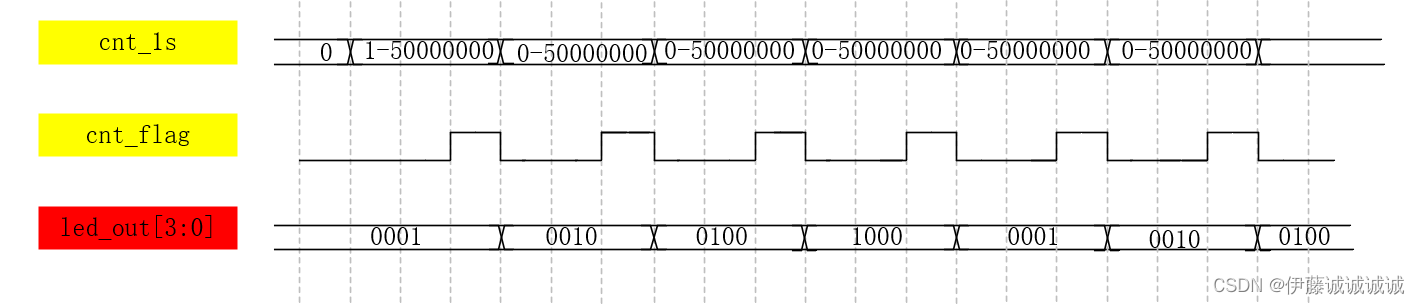

设置的延迟间隔为1S,时钟频率为50MHz,所以每秒计数等于1/(1/50_000_000),每秒计数为50_000_000 ,转换成二进制位26位,所以可以画出1s计数的波形

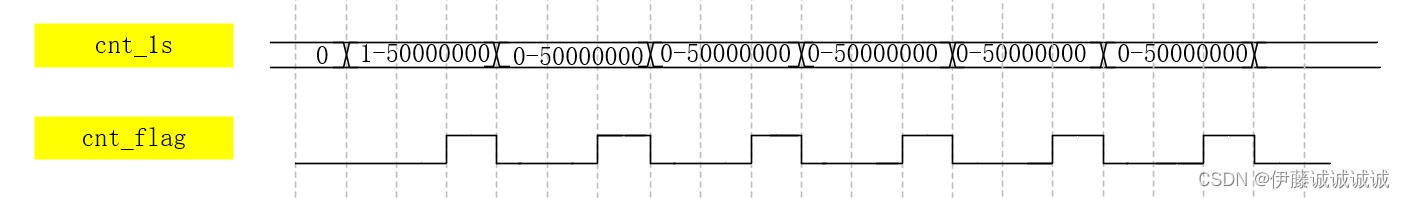

为了准确判断1S计数结束可以增加一个1S计数的标志位

标志位在计数到达最大值之前的一个时钟周期变成高电平,在计数到最大值之后变为低电平

然后是LED的输出

在1S延迟后进入下一个循环指令,由这个波形图就可以编写LED流水灯的模块代码了

在simulate source 这里添加测试文件testbench.v 文件

程序基本这样,纯手打没有进行验证,大概就是这个循环,接下来就是可以创建DXC文件进行管脚的约束,LED流水灯的实现基本就告一段落了。

本文内容由网友自发贡献,转载请注明出处:https://www.wpsshop.cn/w/Monodyee/article/detail/722041

推荐阅读

相关标签