FPGA——全加器的实现_全加器如何设置顶层文件

赞

踩

一.输入原理图实现1位加法器

1.创建工程

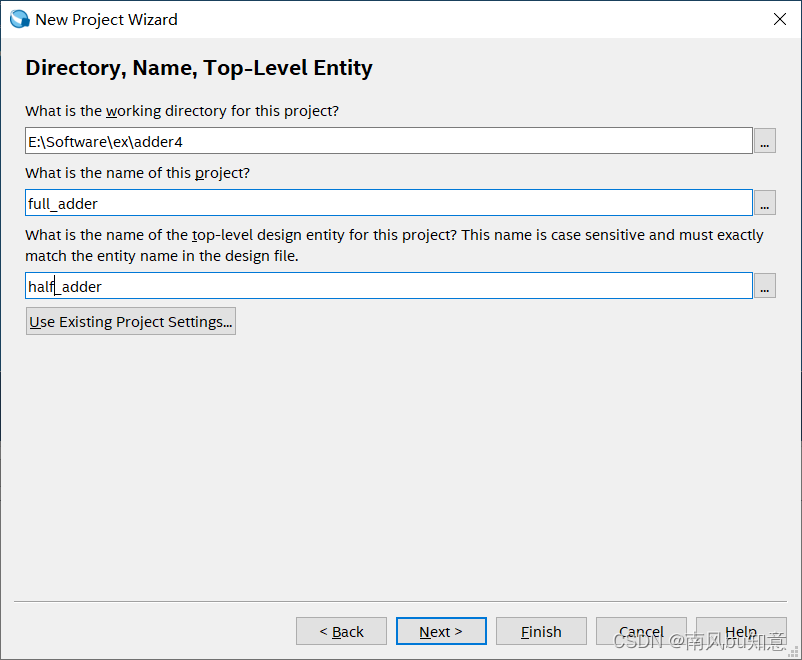

首先启动Quartus Ⅱ,new->NEW project Wizard,然后点击两次next,后如下图:

本项设计的文件夹取名为adder4,文件名取为half_adder

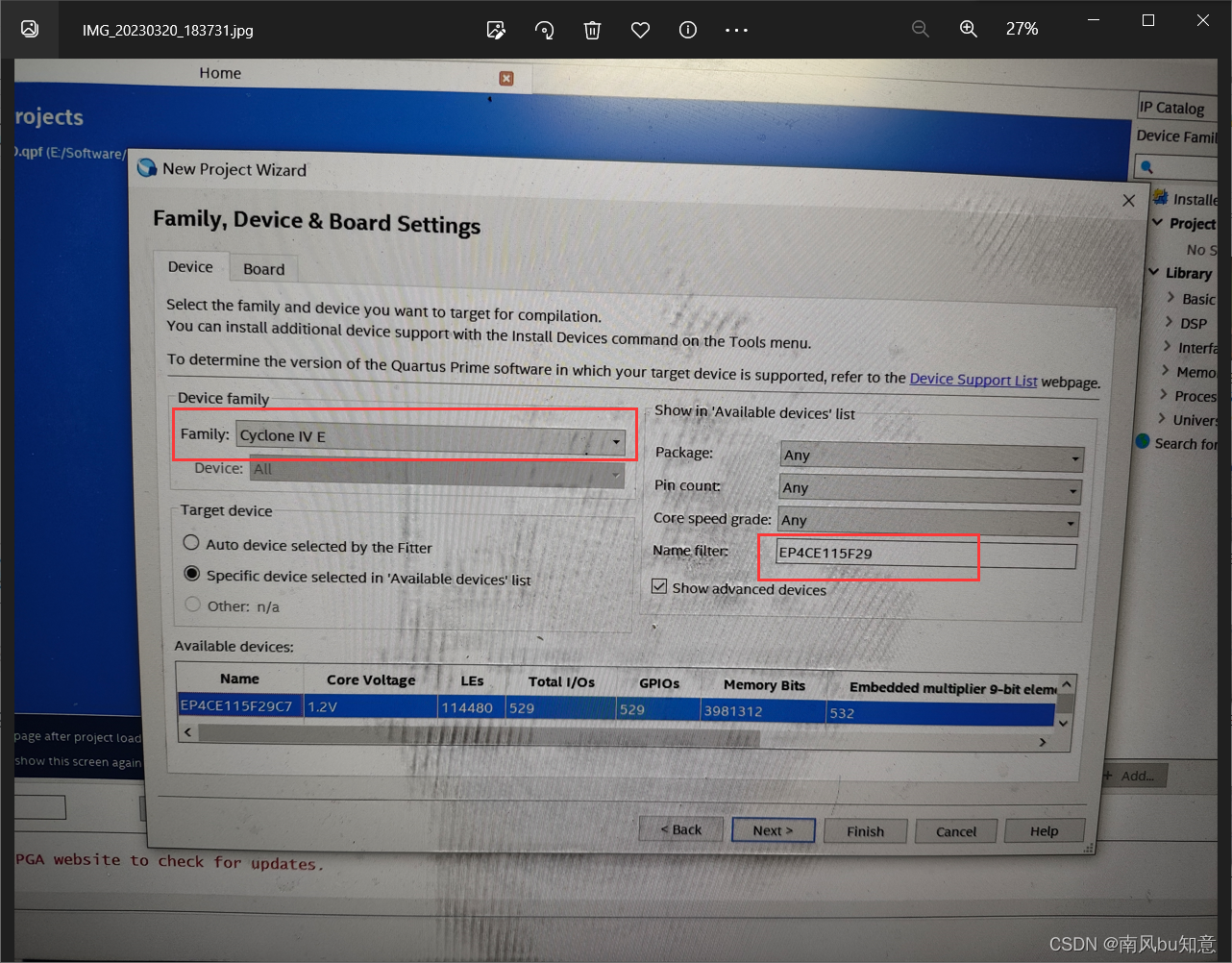

选择目标芯片: cycloneIVE系列的EP4CE115F29C7 ,如图:

选择目标芯片: cycloneIVE系列的EP4CE115F29C7 ,如图:

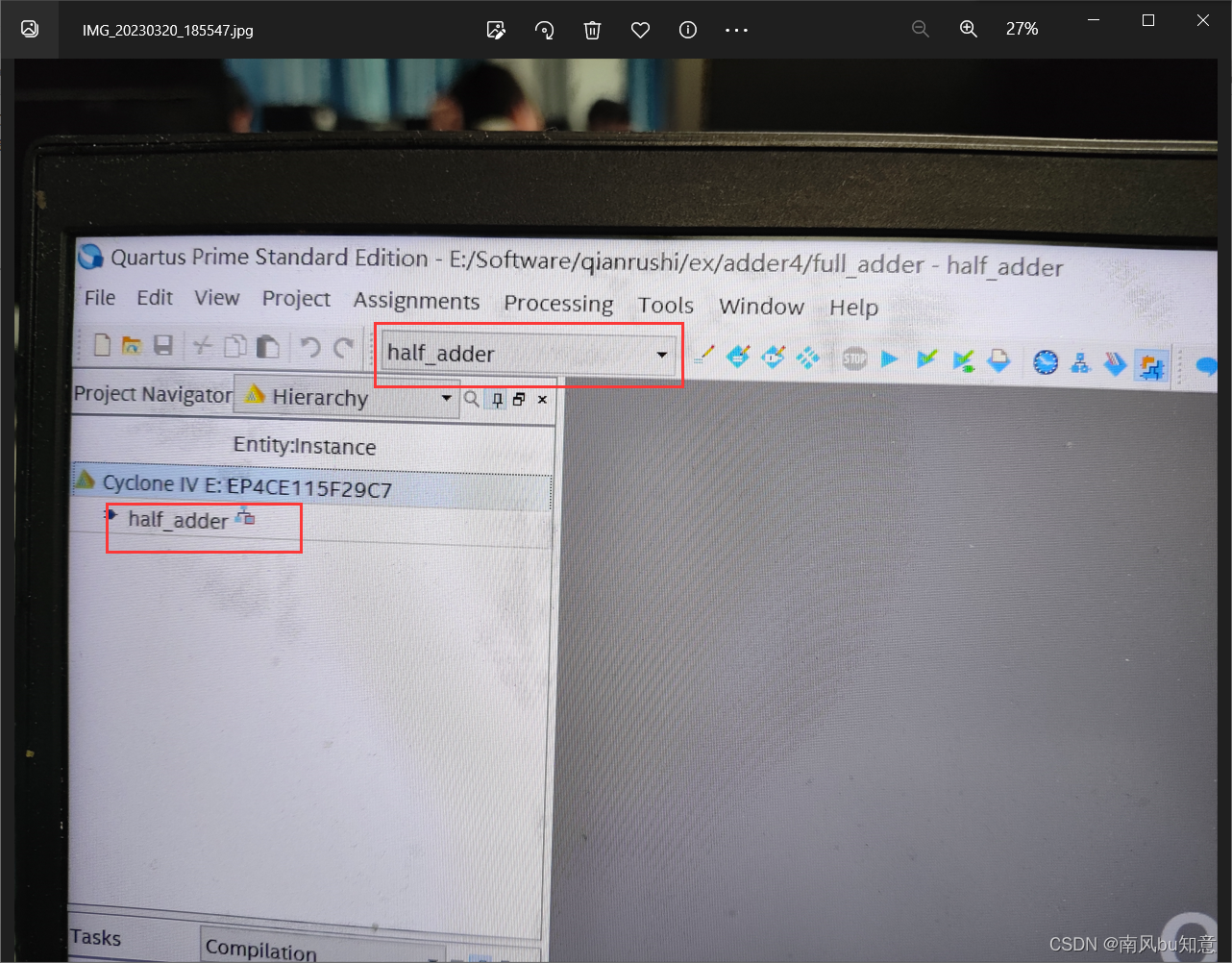

一直点击next,直到最后选择finish,此时界面上会出现顶层文件名和项目名:

2.新建原理图文件

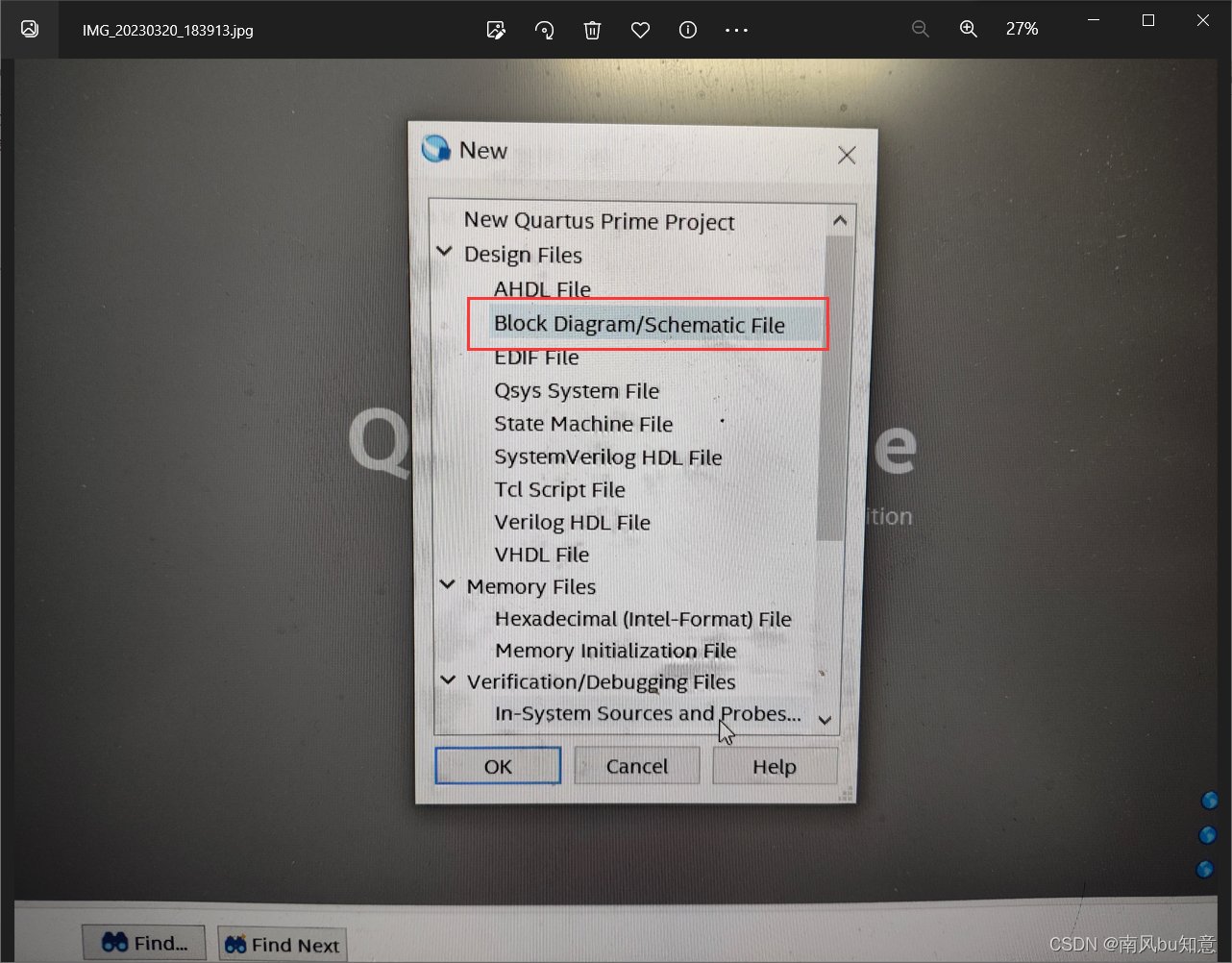

(1)新建原理图文件。打开QuartusII,选菜单“File”—“New”,在弹出的“New-”对话框中选择“Design Files”的原理图文件编辑输入项“Block block diagram/schematic File"按"OK"后将打开原理图编辑窗。

(2)在编辑窗中调入元件,完成半加器的原理图输入。

点击按纽或直接双击原理图空白处,从“Symbol”窗中选择需要的符号,或者直接在“name”文本框中键入元件名,如“and2”为2输入与门,点OK按钮,即将元件调入原理图编辑窗中。例如为了设计半加器,分别调入元件and2,not,xnor和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。然后分别在input和output的PIN NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b, co和s。

添加输入输出,完成效果:

(4)存盘编译。

选择菜单File - Save As,选择刚才为自己的工程建立的目录d : \adder4,将已设计好的原理图文件取名为:half_adder.bdf(注意默认的后缀是.bdf),并存盘在此文件夹内。然后点击进行编译,若无错误则可进行下一步,若有错进行原理图修改。编译完成后最下面的“message”框中信息如下:

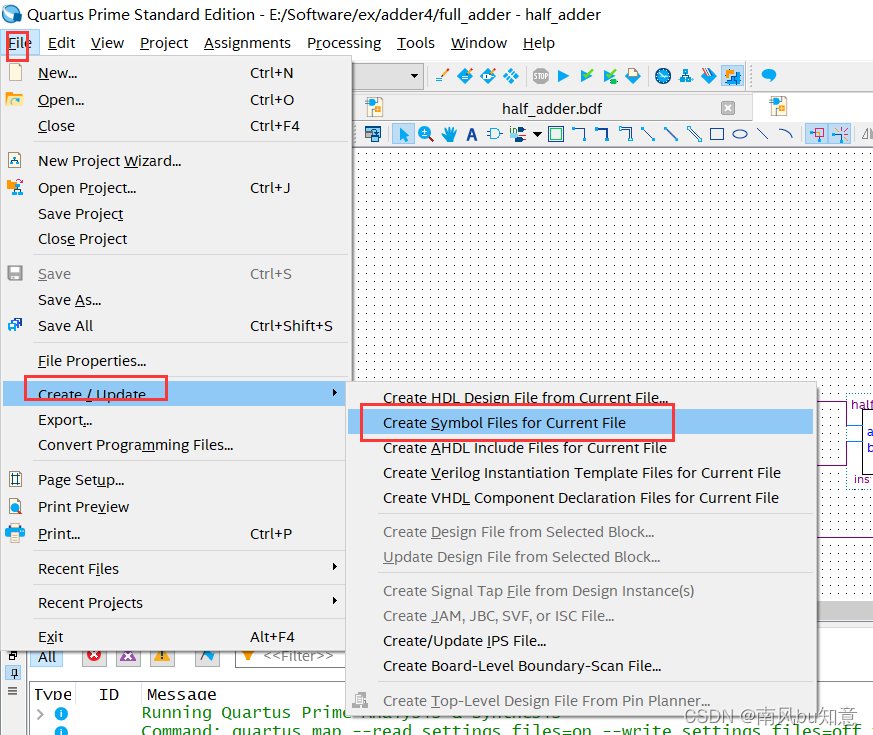

3.将设计项目设置成可调用的元件

为了构成全加器的项层设计,必预将以上设计的半加器half_adder.bdf设置成可调用的元件。方法图所示,在打开半加器原理图文件half_adder.bdf的情况下,选择菜中File中的Create/Update→Create Symbol Files forCurrent File项,即可将当前文件h_adder. bdf变成一个元件符号存盘,以待在高层次设计中调用。

使用完全相同的方法也可以将VHDL文本文件变成原理图中的一个元件符号,实现VHDL文本设计与原理图的混合输入设计方法。转换中需要注意以下两点:

(1)转换好的元件必须存在当前工程的路径文件夹中;

(2)该方法只能针对被打开的当前文件。

4.半加器仿真

(1)新建波形文件。如上面新建图形文件的方法,从“file”中选择“new”,然后从出现的对话框中选择“university program VWF”。点击“OK”。

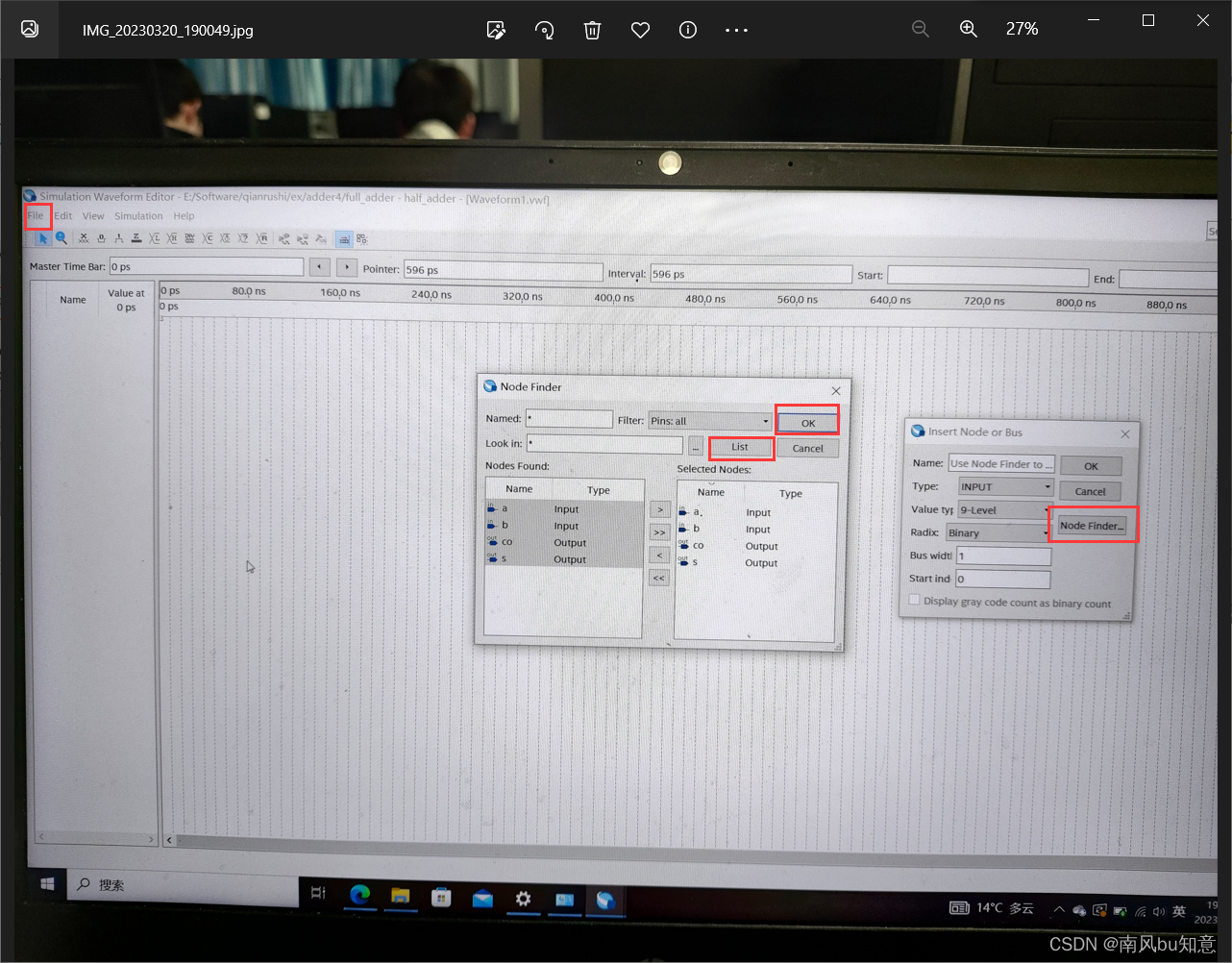

(2)添加信号

(3)编辑信号

保存文件并启动功能仿真:

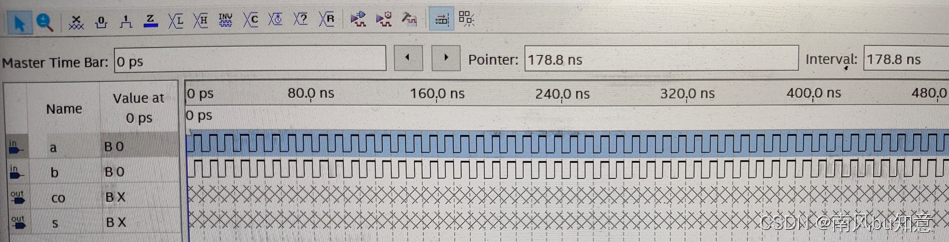

功能仿真结果:

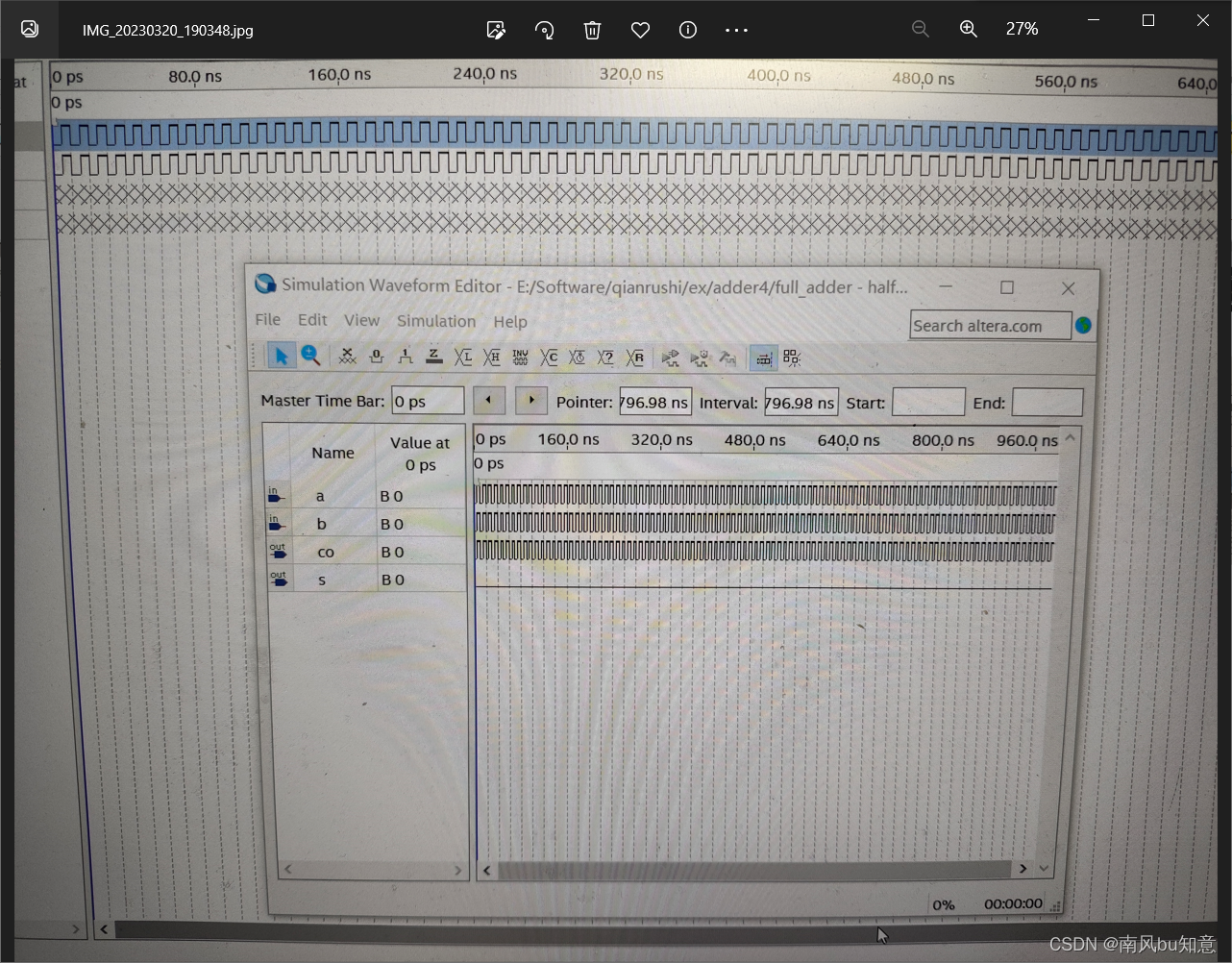

时序仿真结果:

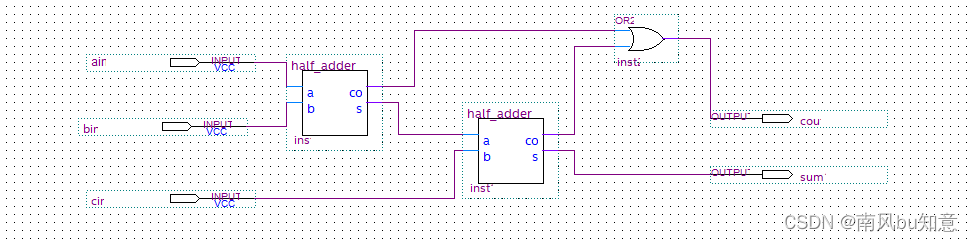

5.设计全加器顶层文件

为了建立全加器的项层文件,必须再打开一个原理图编辑窗,即新建一个原理图文件。方法同前,即再次选择菜单"File”→“new",原理图文件编辑输入项"Block Diagram/Schematic File"。

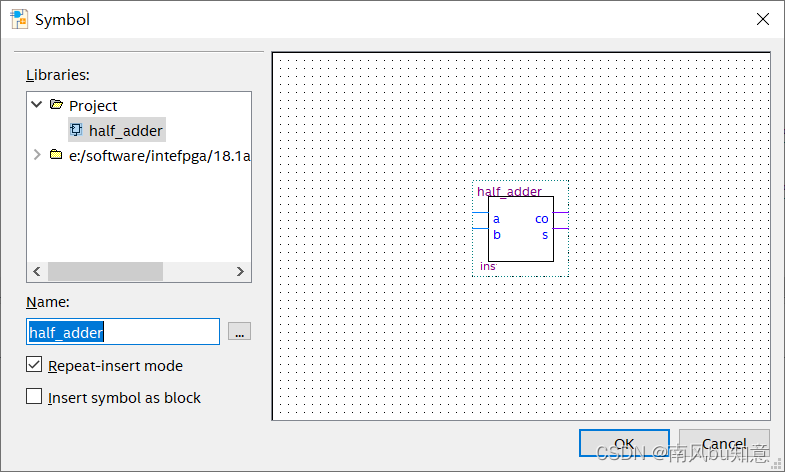

与调入元件的方法一样,即在新打开的原理图编辑窗双击鼠标,在弹出的“symbol”窗的“name”栏输入底层文件半加器的存储名“half_adder”调出半加器,如图

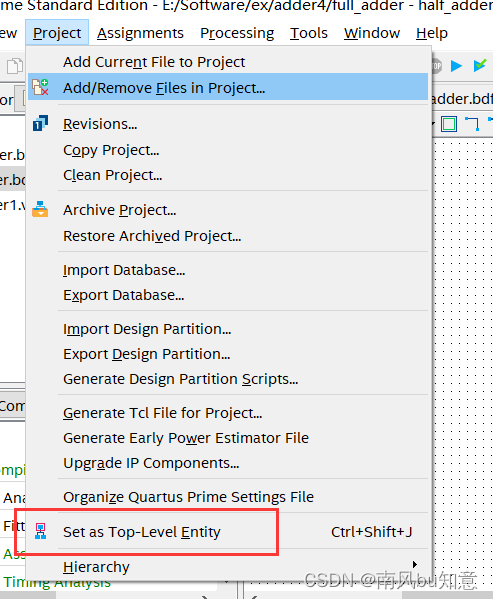

6.将设计项目设置成顶层文件并编译仿真

将顶层文件f_adder.bdf设置为顶层文件的方法: project→set astop_level entity。如图:

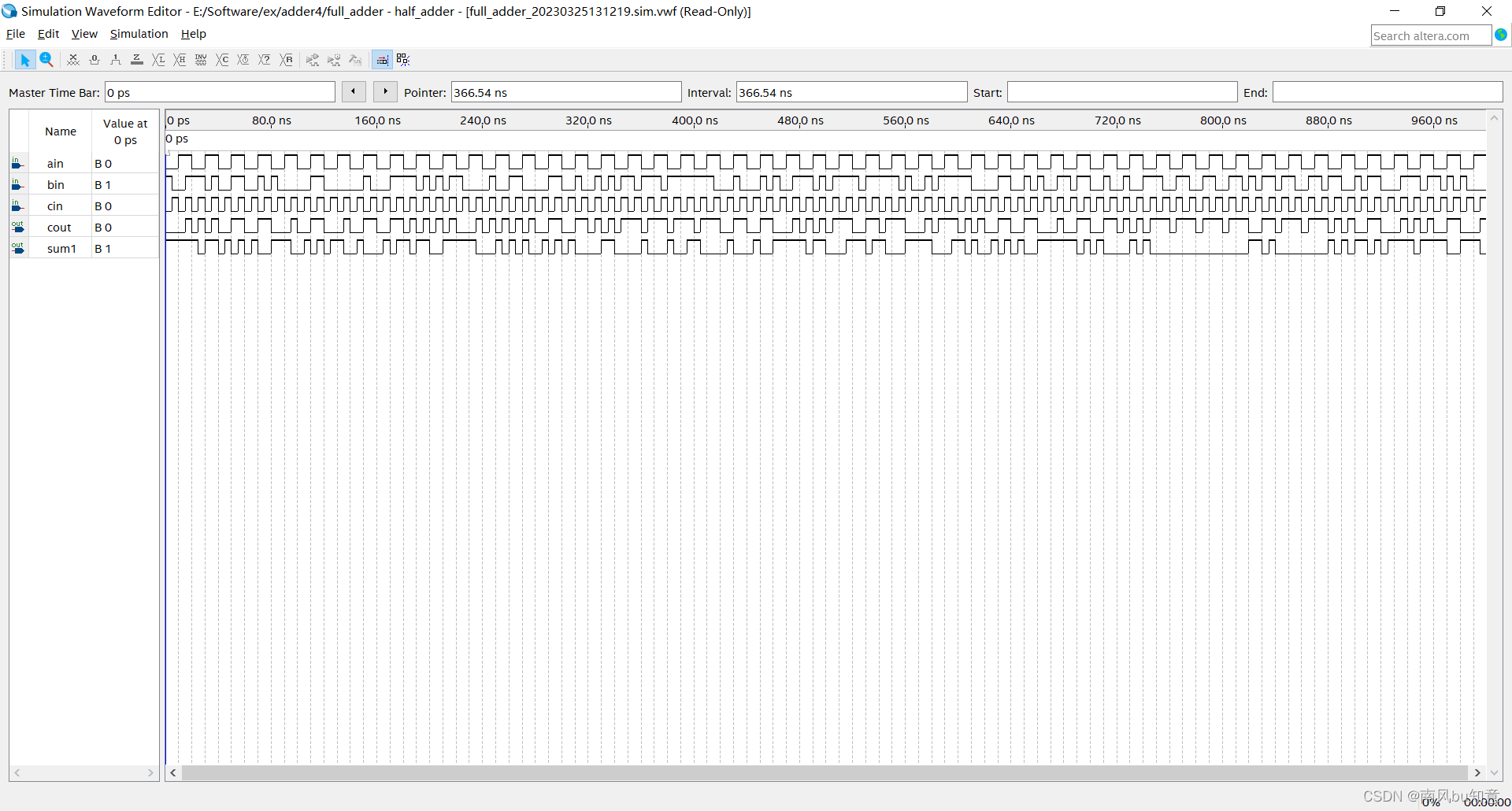

功能仿真

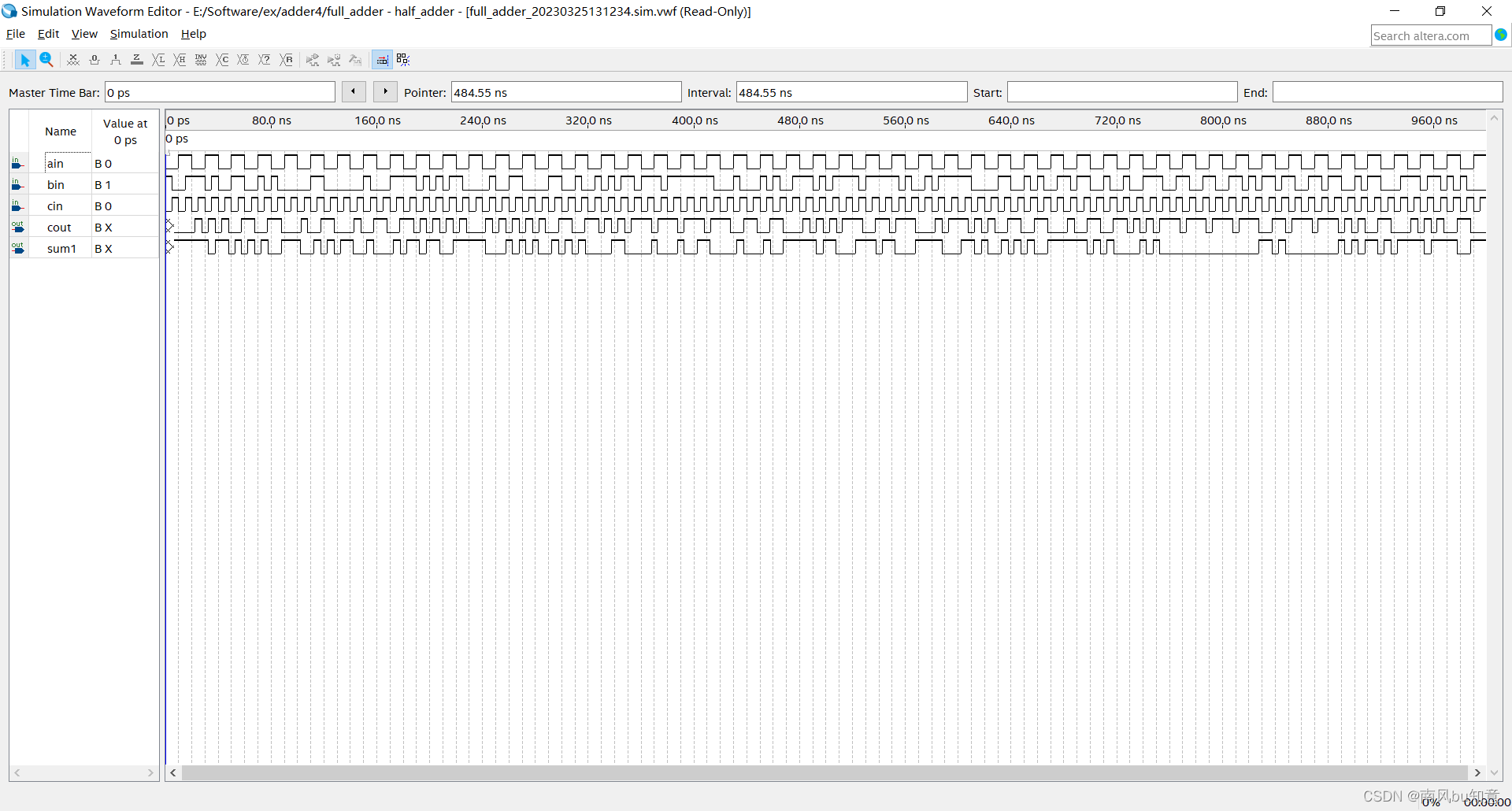

时序仿真

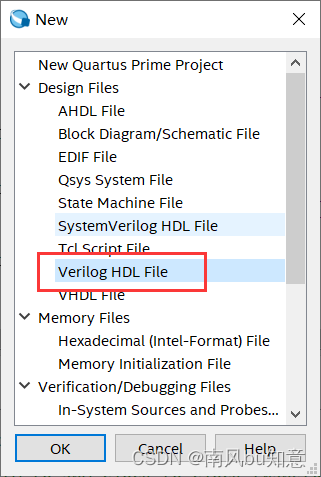

7.verloge编程

代码:

module full_adder2(

input ain,bin,cin,//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

output cout,sum//输出信号,cout表示向高位的进位,sum表示本位的相加和

);

assign sum=(ain^bin)^cin;//本位和输出表达式

assign cout=(ain&bin)|((ain^bin)&cin);//高位进位输出表达式

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

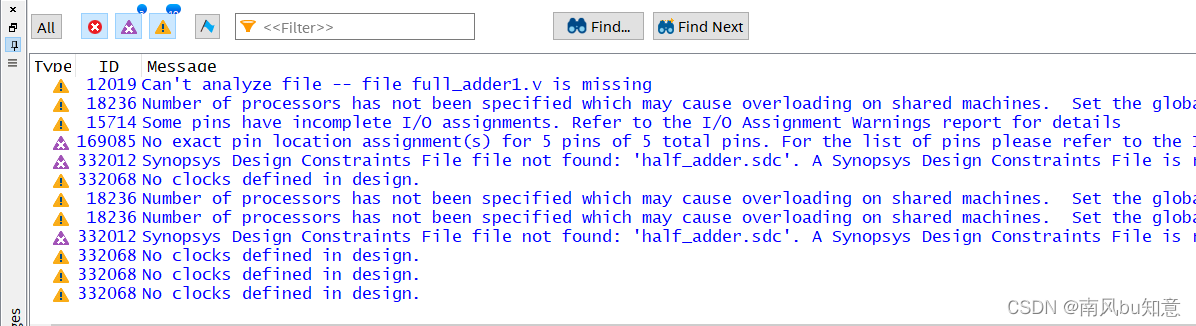

编译运行

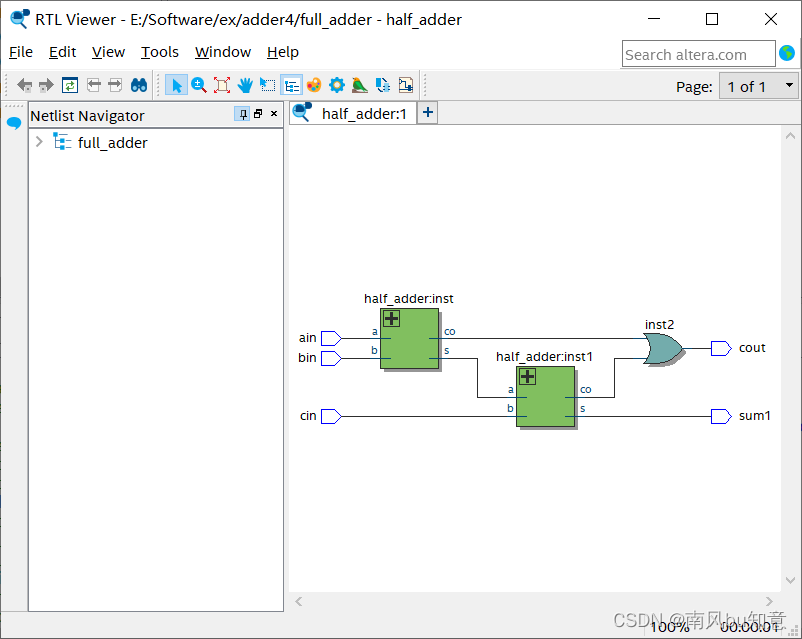

此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

8.板上验证

因器材不足下次补上

二.4位全加器设计

1、输入原理图方法设计4位全加器

将full_adder设置为可调用元件:

新建原理图文件:

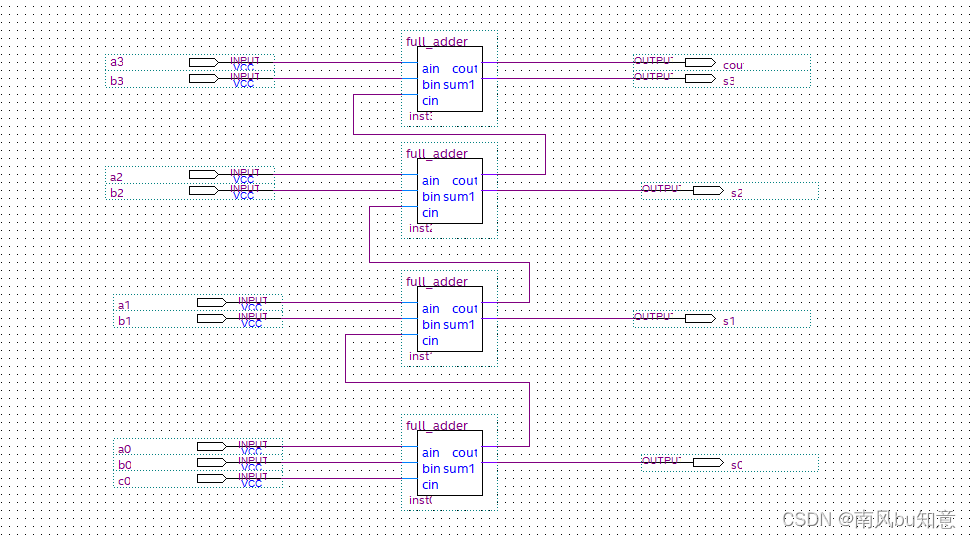

点击File->New,然后选择Block Diagram/Schematic File,选择元件full_adder,并绘制原理图:

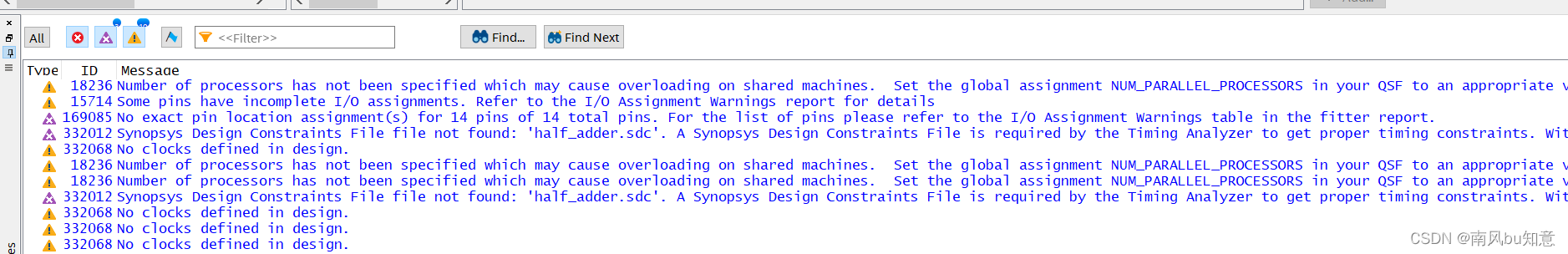

将原理保存至adder4文件夹下,并命名为full_adder4.bdf,将full_adder4.bdf设置为顶层文件并编译:

没有红色即为编译成功

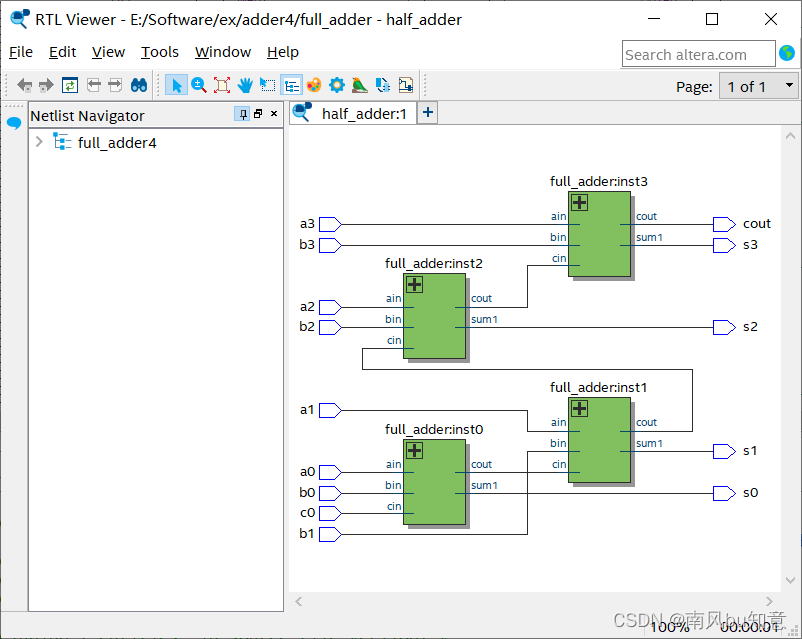

通过tool->Netlist Viewers->RTL Viewer,查看电路图:

仿真:

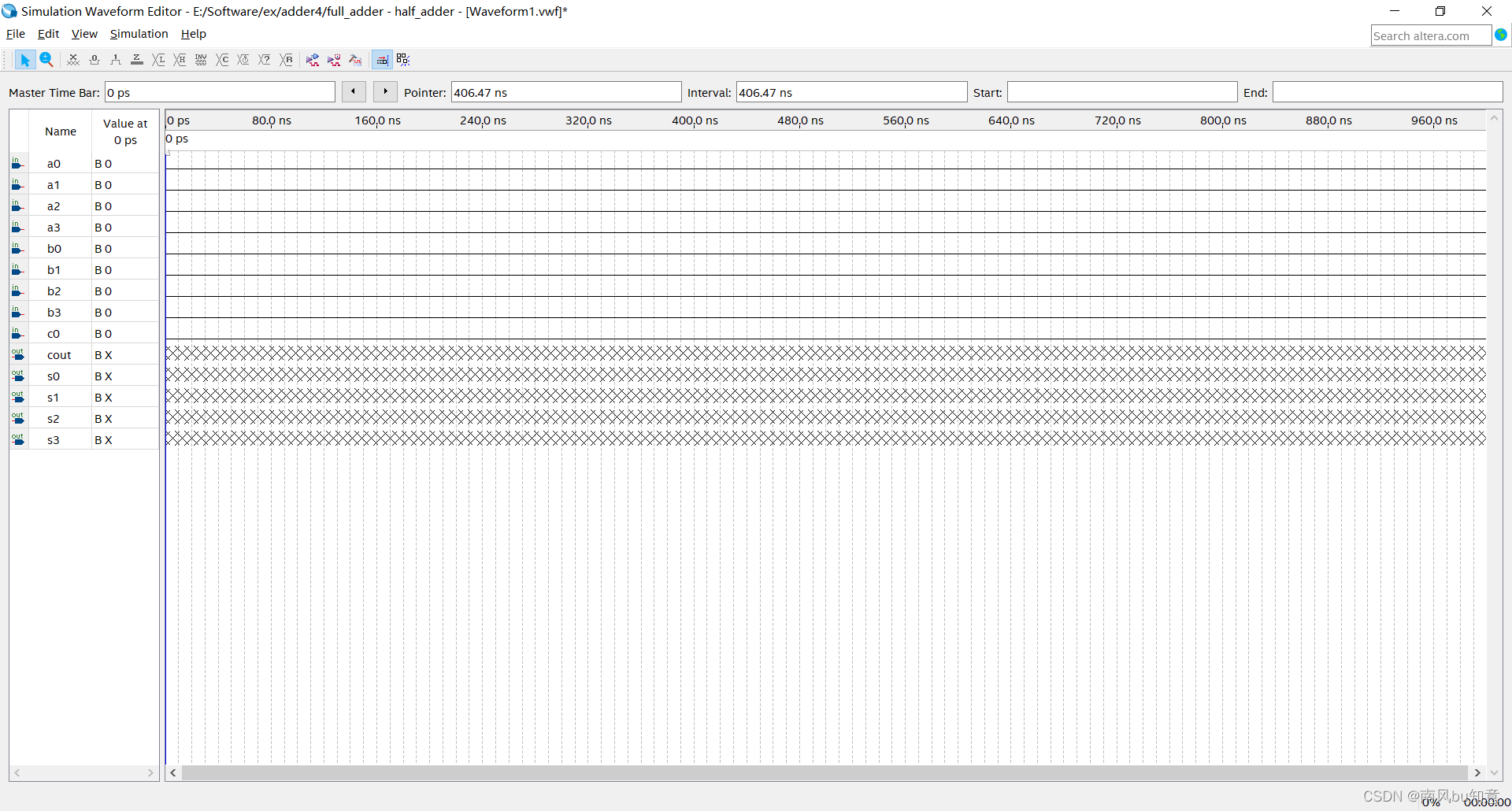

创建一个向量波形文件,并添加、编辑信号:

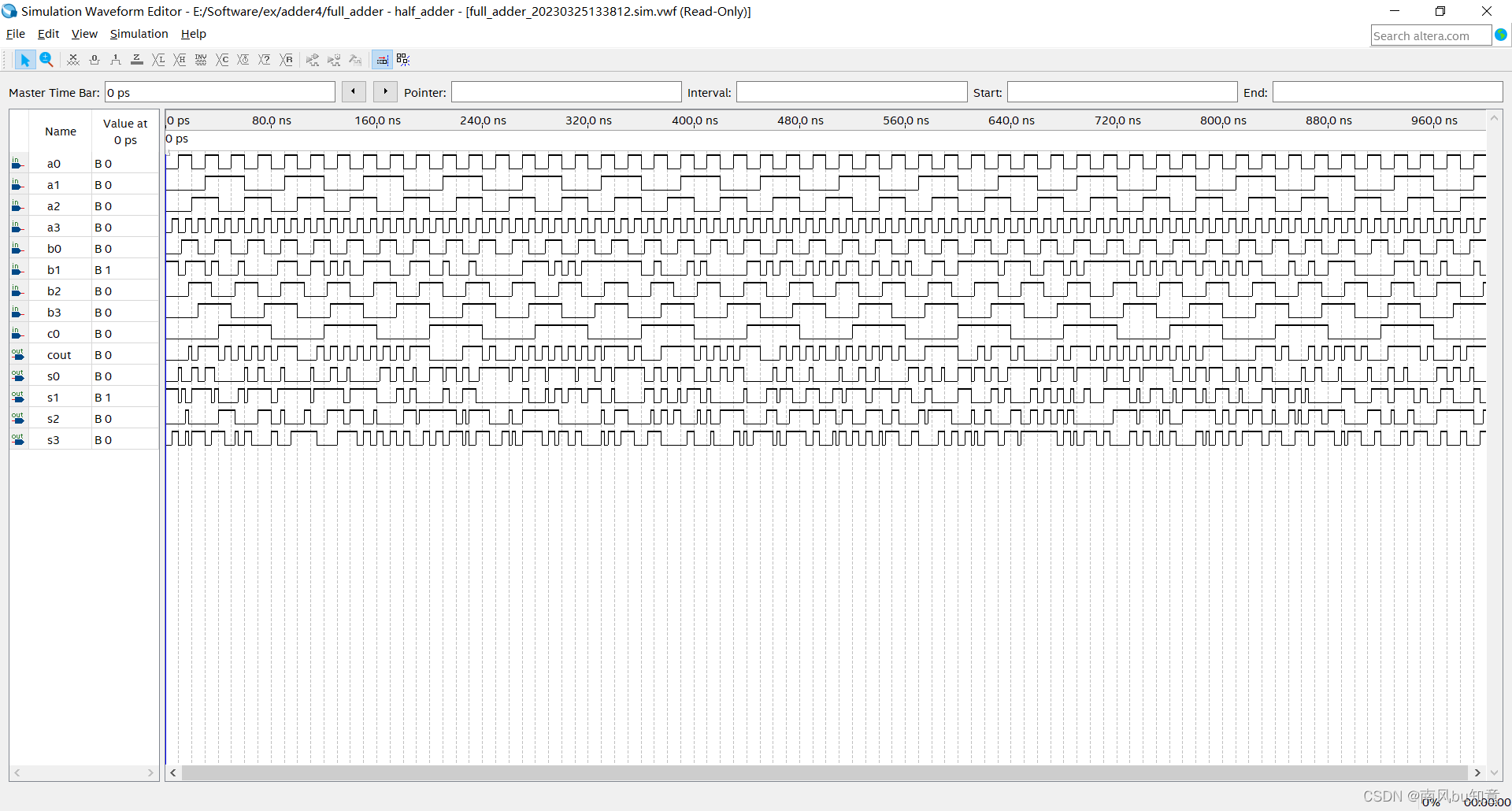

功能仿真:

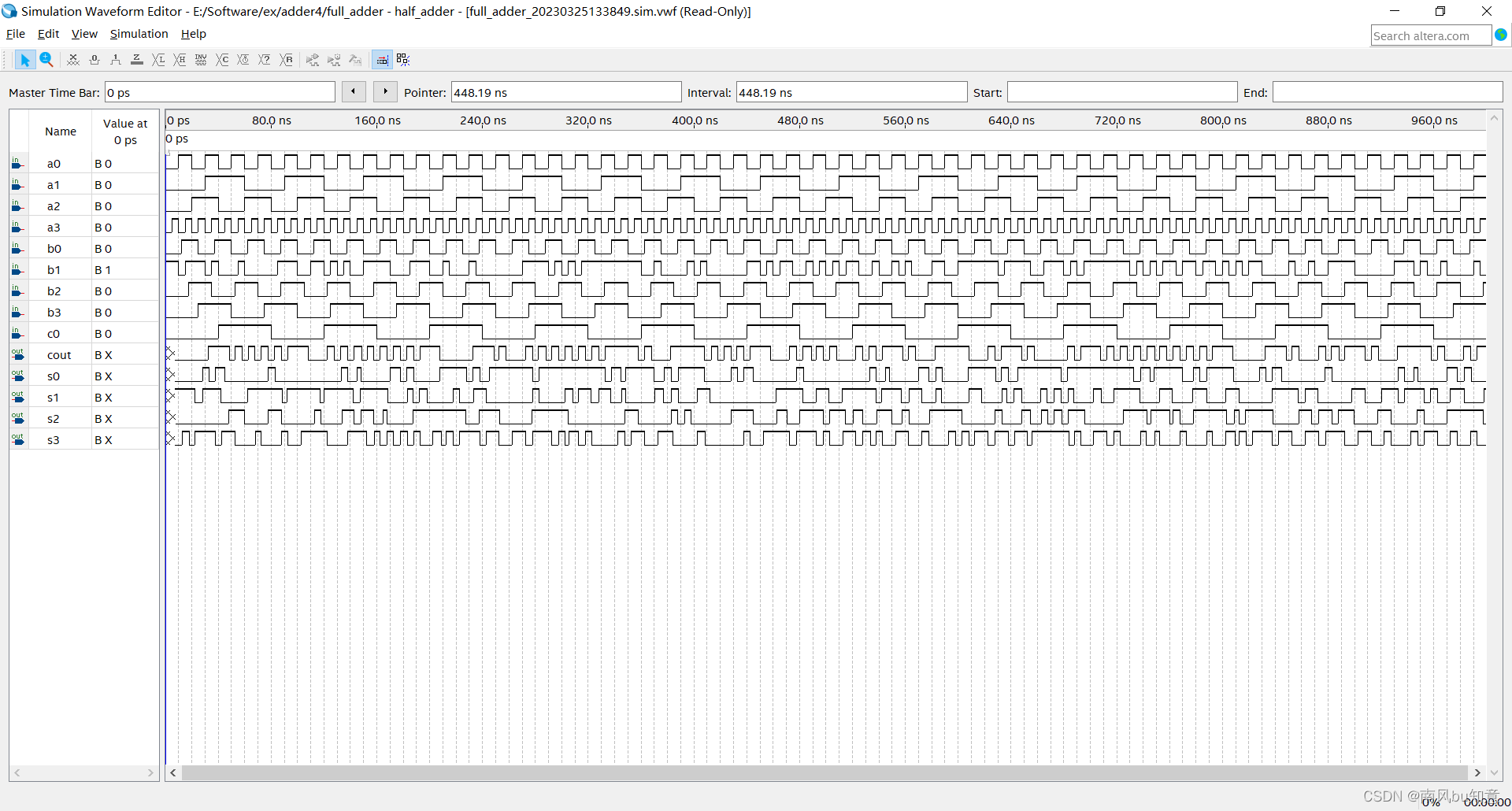

时序仿真

2、Verilog编程方法设计4位全加器

代码:

module Verilog ( num1, num2, cin, cout, sum ); input [3:0] num1; input [3:0] num2; input cin; output cout; output [3:0] sum; reg cout; reg [3:0] sum; reg add; reg [1:0] cnt; always @(num1 or num2 or cin) begin // 第一位 sum[0] = (num1[0] ^ num2[0]) ^ cin; cout = (num1[0] & num2[0]) | (num2[0] & cin) | (num1[0] & cin); add = cout; // 第二位 sum[1] = (num1[1] ^ num2[1]) ^ add; cout = (num1[1] & num2[1]) | (num2[1] & add) | (num1[1] & add); add = cout; // 第三位 sum[2] = (num1[2] ^ num2[2]) ^ add; cout = (num1[2] & num2[2]) | (num2[2] & add) | (num1[2] & add); add = cout; // 第四位 sum[3] = (num1[3] ^ num2[3]) ^ add; cout = (num1[3] & num2[3]) | (num2[3] & add) | (num1[3] & add); add = cout; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

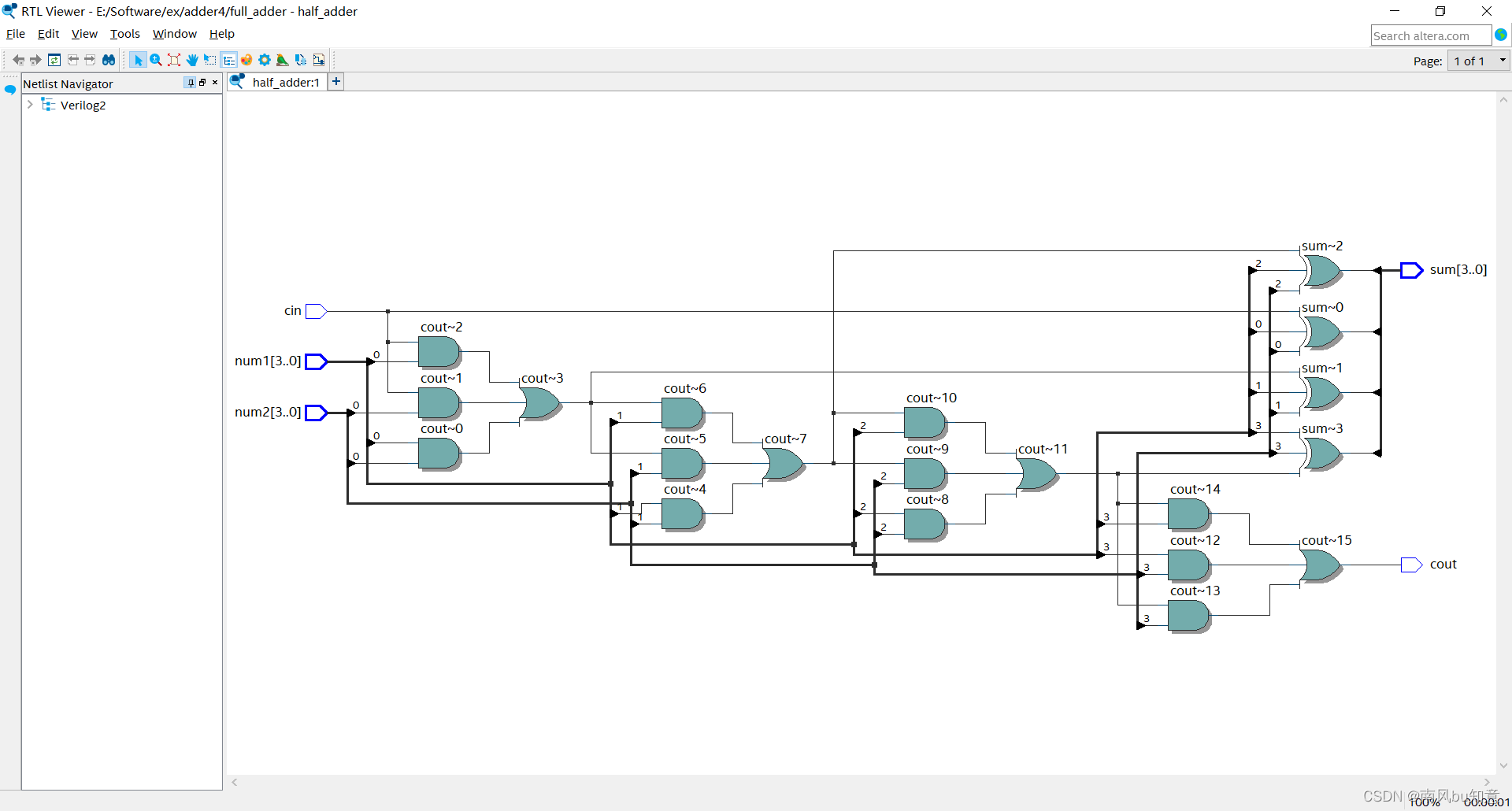

保存并编译,此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

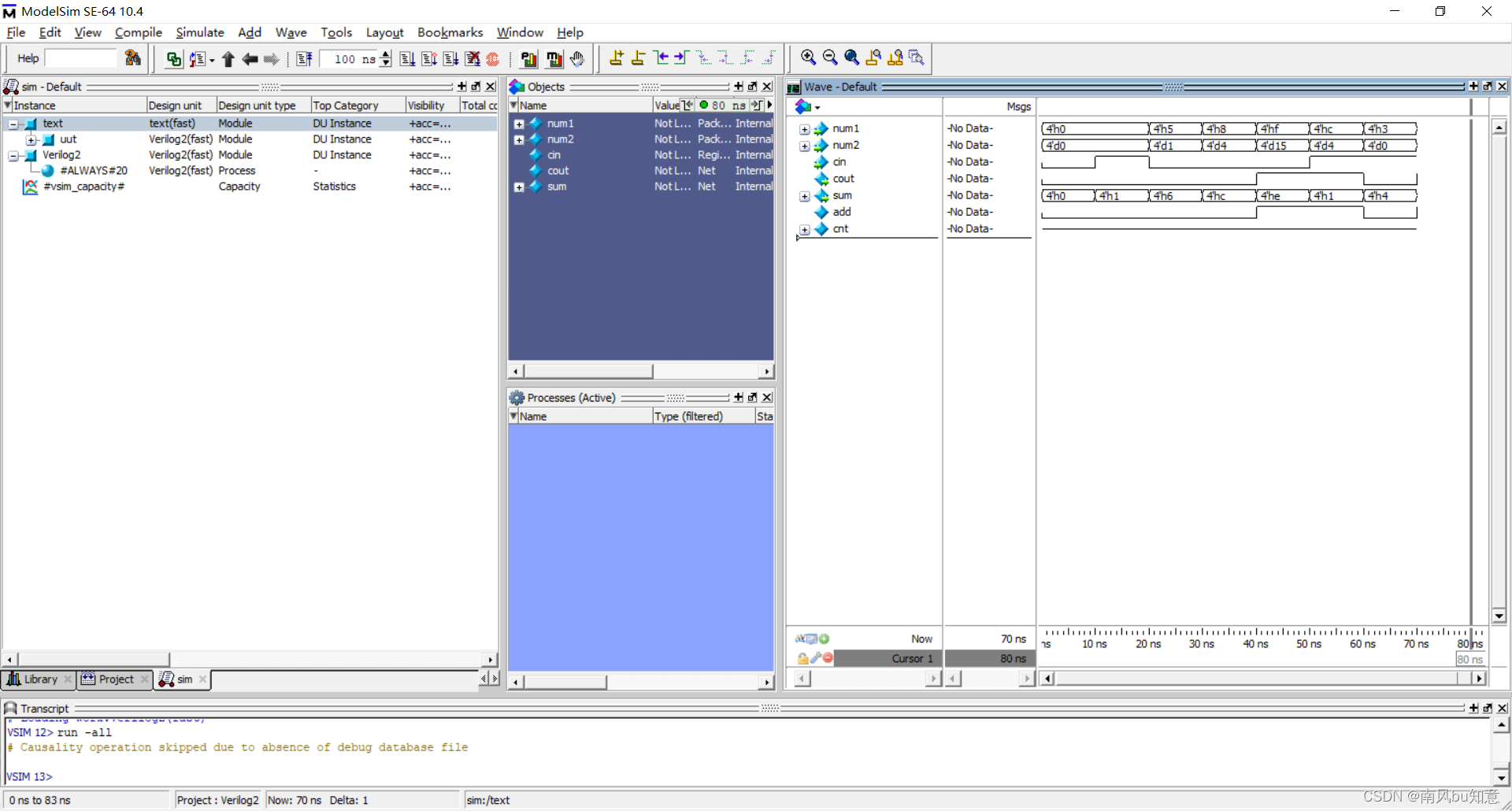

使用modelsim进行验证:

module four_tb (); reg [3:0] num1; reg [3:0] num2; reg cin; wire cout; wire [3:0] sum; four uut( .num1(num1), .num2(num2), .cin (cin), .cout(cout), .sum (sum) ); initial begin num1 <= 4'b0000; num2 <= 4'b0000; cin <= 0; #10 num1 <= 4'b0000; num2 <= 4'b0000; cin <= 1; #10 num1 <= 4'b0101; num2 <= 4'b0001; cin <= 0; #10 num1 <= 4'b1000; num2 <= 4'b0100; cin <= 0; #10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 0; #10 num1 <= 4'b1100; num2 <= 4'b0100; cin <= 1; #10 num1 <= 4'b0011; num2 <= 4'b0000; cin <= 1; #10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 1; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

验证结果:

3、上板验证

器材不足,后续补全