- 1飞桨Ai(一)基于训练后的模型进行信息提取

- 2Pytorch入门实战: 05-Pytorch实现运动鞋识别

- 3华为OD机试-考勤信息_od考勤信息 python

- 4CompletableFuture异步编程事务及多数据源配置详解(含gitee源码)_completablefuture.runasunc

- 5数字集成电路设计(六、Verilog HDL高级程序设计举例)_verilog hdl高级数字设计

- 6人工智能机器人 grok-1在github开源_grok-1 github

- 7Windows10安装多个版本的PostgreSQL数据库,但是均没有自动注册Windows服务的解决方法_win10安装两个版本的pg

- 8laravel实现AMQP(rabbitmq)生产者以及消费者_laravel amqp

- 9Personal Fedora 9 Installation Guide

- 10java.util.Concurrent包下面的常见类_concurrent包下的类

GRANDMICRO有容微分享关于几种PCIe(100MHz HCSL)时钟输出的实现方法和参考设计_pcie 100m参考时钟 芯片

赞

踩

GRANDMICRO有容微分享关于几种PCIe(100MHz HCSL)时钟输出的实现方法和参考设计由原厂授权一级代理分销经销通路供应商KOYUELEC光与电子0755-82574660,82542001为您提供方案设计,谢谢!

PCIe

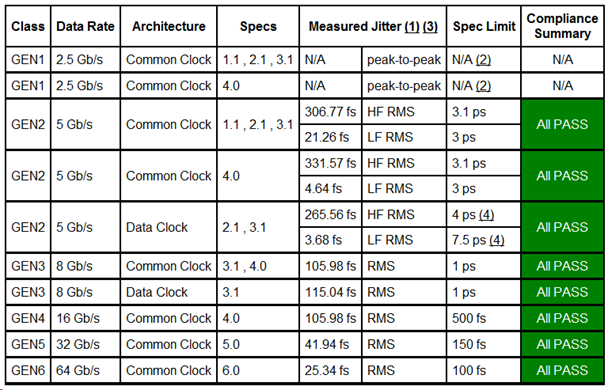

(Peripheral Component Interconnect express) 是一种高速串行计算机扩展总线标准,属于高速串行点对点双通道高带宽差分传输,有效提高数据传输的速度和准确性,PCIe协议下的参考时钟基本为100MHz HCSL(High-speed Current Steering Logic)电平接口时钟,要求确保数据传输的正确性和稳定性,解决时钟抖动、偏移和噪声问题。比如,PCIe Gen3要求收发端参考时钟频率稳定性在±300ppm以内、RMS抖动不超过1.0ps,Gen5要求频率稳定性±100ppm以内、RMS抖动不超过0.15ps:

一、PCIe时钟架构

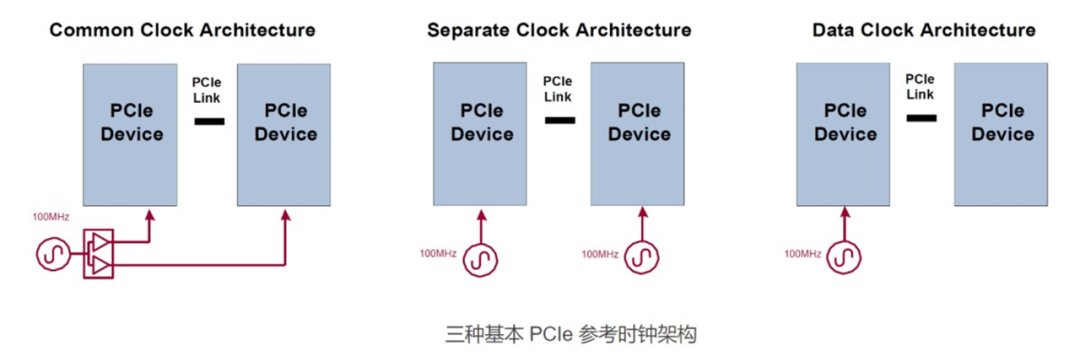

PCIe 时钟架构是指 PCIe 系统中收发端设备给定参考时钟的方案。PCIe 有 3 种时钟架构,分别为:

1. Common Clock Architecture (即常说的CC架构);

2. Separate Clock Architecture;

3. Data Clock Architecture;

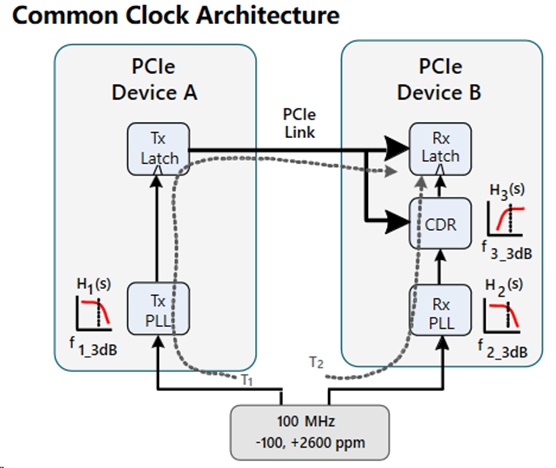

其中Common Clock Architecture (CC架构)是最通用参考时钟架构,其特点是在收发链路两端共享同一个参考时钟。

PCIe CC架构

二、几种PCIe(100MHz HCSL)时钟输出的实现方法和参考设计

01

使用有容微GM5528或GM5508时钟清抖器/时钟产生器芯片输出HCSL 100MHz时钟

GM5528/GM5508输出HCSL 100MHz时钟的相噪/抖动测试

GM5528/GM5508输出HCSL 100MHz 抖动数据 vs PCIe时钟标准要求

可见:GM5528/GM5508输出的HCSL 100MHz时钟符合PCIe Gen1/2/3/4/5/6 (CC)标准

(*说明:GM5528支持多达14路输出,GM5508支持多达8路输出)

02

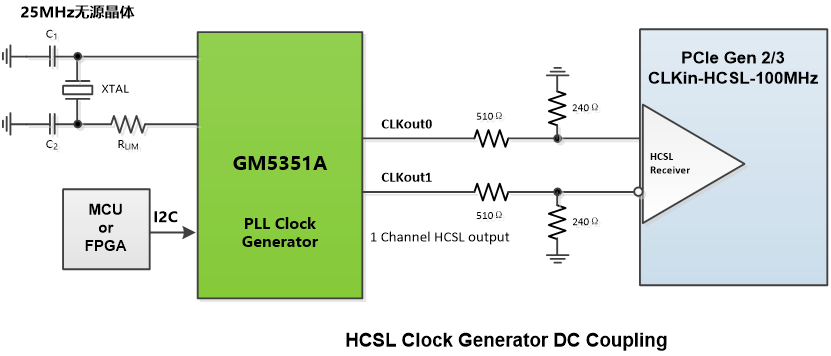

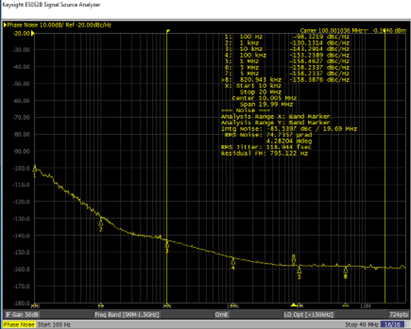

使用有容微GM5351A时钟产生器芯片输出HCSL 100MHz时钟

GM5351A时钟产生器芯片本身是3路2.5KHz-250MHz之间任意频率的单端输出,但是可以使用双通道(一般使用CLKout0和CLKout1,因为这两路输出PIN脚相邻便于设计)做反相配置实现HCSL的差分输出,且达到PCIe Gen2/Gen3标准:

GM5351A输出HCSL 100MHz 抖动vs PCIe时钟标准要求

03

使用有容微GM50301/GM50304时钟缓冲器芯片输出HCSL 100MHz时钟

GM50301/GM50304输出HCSL 100MHz抖动测试

可见:GM50301/GM50304输出的HCSL 100MHz时钟符合PCIe Gen1/2/3/4/5/6 (CC)标准

(*说明:GM50301支持多达10路HCSL 100MHz输出,GM50304支持多达4路HCSL 100MHz输出)