- 1十款开源的数据库管理工具

- 2无人机组装调试步骤(保姆级别教程)

- 3Mysql 关于修改 “时间” 时报错Incorrect datetime value: '' for column 'createtime'_incorrect datetime value: '2023-06

- 4内网穿透(frp和proxychains4)

- 5初始Java篇(JavaSE基础语法)(7)抽象类和接口(上)

- 6OceanBase—01(入门篇——使用docker安装OceanBase以及介绍连接OB的几种方式)_docker oceanbase

- 7WPF CommandBinding CommandParameter 用法_wpf textblock将当前控件的text传入commandparameter

- 8linux 命令读db文件格式,使用linux的db_load命令生成db数据库

- 9Android14音频进阶之AAOS之CarAudioService如何衔接AudioControl服务(七十四)

- 10数据结构选择题判断题(PTA)_可以用带表头附加结点的链表表示线性表,也可以用不带头结点的链表表示线性表,前者

AG16KL144A与AG10KL144的调试注意事项_ag10kl144h 程序

赞

踩

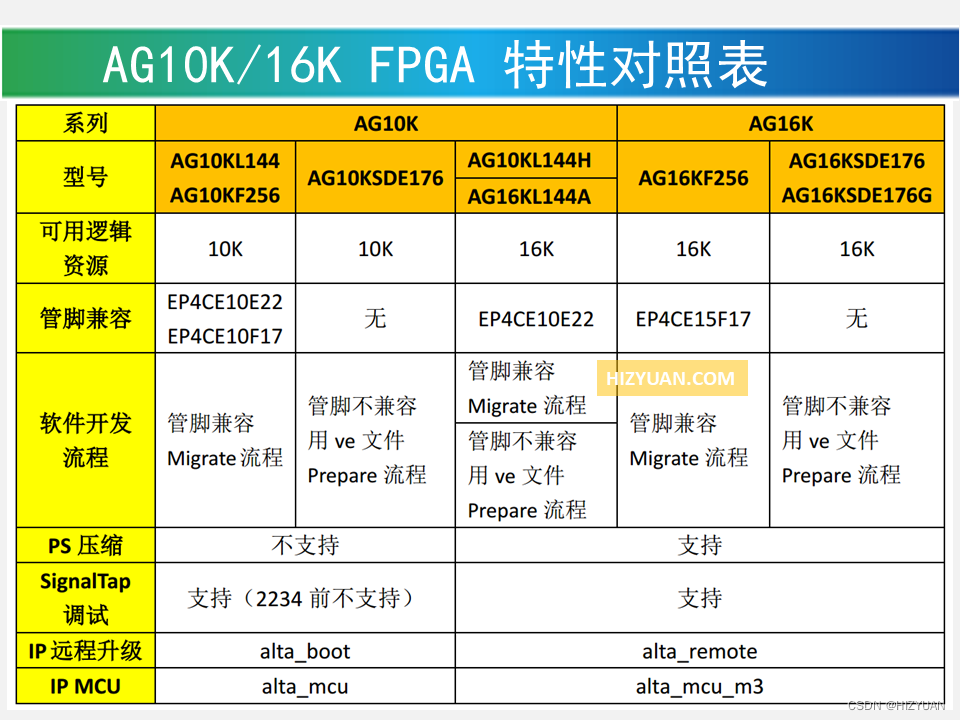

为了适应客户产品升级的升级迭代需求,AGM的推出了逻辑资源更大的AG16KL144A,是逻辑资源升级的型号,芯片管脚与AG10KL144 / AG10KL144H完全兼容,同时也兼容ALTERA EP4CE10E22等器件。

AG10KL144H 为 AG10KL144 管脚兼容型号,但实际逻辑资源可以达到 16K LEs,也可使用 AG16K IP。 如果仅用 10K,可以遵循原兼容型号设计转换流程(参考海振远科技提供的 Manual_supra.pdf),即采用 Quartus 的 EP4CE10E22 工程来转换,只是 Supra 内型号选择 AG10KL144H。如用到 16K LEs,需要采用非兼容型号的 prepare 设计流程, Supra 里选择 AG16KL144A 这个新型号。AG16K具有更优异的特性。

特性

- 高密度架构与16K的LEs

- 高达504Kbits的RAM空间

- 最多56个18 × 18位嵌入式乘法器,每个可配置为两个独立的9 × 9位乘法器

- 每个器件提供4个锁相环,提供时钟倍增和相移

- 高速差分I/O标准支持,包括LVDS, RSDS, mini-LVDS, LVPECL

- SSTL、SSTL- ii IO标准,支持DDR、DDR2

- 支持单端I/O标准,包括3.3V、2.5V、1.8V、1.5V LVCMOS和LVTTL

- 通用封装选项,LQFP-144, -176和FBGA-256

- 两个12位SarADC(嵌入式温度传感器)

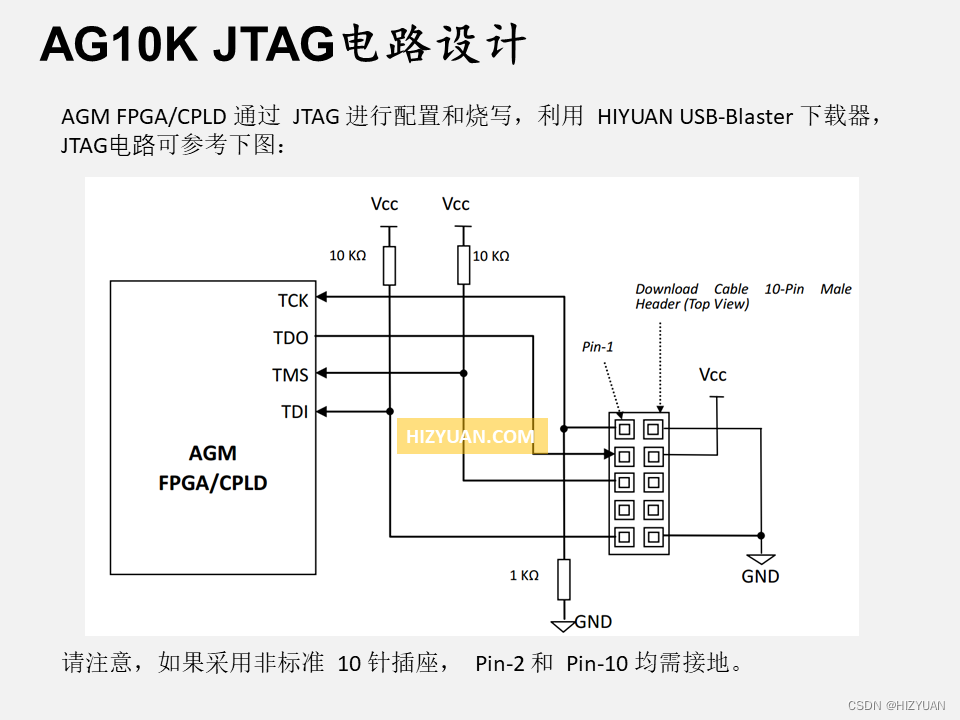

- 灵活的器件配置,通过JTAG和SPI接口

- 支持远程更新,由“双启动”式实现

- 支持芯片上的信号调试

AG16KL144A与AG10KL144兼容。

AG16KSDE176/AG16KSDF256/AG16KSDE176G器件是AG16K FPGA绑定64MBit 32位166MHz SDRAM:

- AG16KSDE176、QFP-176封装支持2层PCB(低成本)设计。AG16KSDE176引脚对引脚兼容AG10KSDE176。

- AG16KSDF256, FBGA-256包支持152个用户IOs和3个额外的ADC IO。

- AG16KSDE176G、QFP-176封装支持2层PCB(低成本)设计,支持139个用户IOs。

AG16KDDF256器件是AG16K FPGA结合128MBits 16位200MHz DDR-SDRAM, FBGA-256封装支持170用户IOs。

关于AG16K的调试及设计代码移植方面,有以下几方面需要注意的事项。

一、在线调试功能

在 DateCode 2234 日期之后的 AG10K 芯片已支持 Quartus II 中的 Signal Tap 功能,编译烧录后可使用,同 AG16K。

二、AG10KL144H (AG16KL144A) 转换注意事项

AG10KL144H 为 AG10KL144 升级型号,封装管脚兼容(同样兼容 EP4CE10E22)。 性能更优,增加部分功能特性。 内部与 AG16K 一致。

芯片丝印: 根据不同批次, 有 2 种,均为正确标识:

1. 型号标识为 AG10KL144H

2. 日期编码(DATE CODE) 后加 H,如 2302-H,型号标识仍为 AG10KL144

3. 最新型号标识为 AG16KL144A,如需要样品测试可以联系海振远科技。

三、原 AG10KL144 设计替换为 144H,需要注意以下事项:

1. Supra 原工程需要重新编译, Device 选择 AG10KL144H,其它设置可以不变。

2. AG10KL144 PLL IP 的复位控制可以省去,如已加入也可正常使用。(参考上节 1.PLL)

3. AS 口烧写 FLASH 用 XXX_master_as.prg 文件, SPI 端口不需串接电阻。(参考上节 5. AS 口在线烧写 FLASH)

4. PS 烧写可以支持数据文件的压缩。(参考上节 10. 烧写文件压缩)

5. 原 AG10KL144 的 Dual-Boot IP(alta_boot)需要用 Remote-Upgrade IP(alta_remote) 替代, 功能更强大, 具体可以参考 Manual_remote.pdf 文档。

6. 原 AG10KL144 的 MCU IP(alta_mcu)需要用(alta_mcu_m3) 替代。

7. 如果原 AG10KL144 设计 MSEL[0..2]串接了电阻到 VCC 或 GND,请改为 0 欧或直连,否则可能会导致 Supra 烧录 FLASH 错误。(参考上节 15. MSEL 配置模式选择)

8. 新增支持 Quartus II 中的 Signal Tap 功能,编译烧录后可使用。

四、AG10KL144H 如何升级使用 16K LEs

AG10KL144H 为 AG10KL144 管脚兼容型号,但实际逻辑资源可以达到 16K LEs,也可使用 AG16K IP。 如果仅用 10K,可以遵循原兼容型号设计转换流程(参考海振远科技提供的 Manual_supra.pdf),即采用 Quartus 的 EP4CE10E22 工程来转换,只是 Supra 内型号选择 AG10KL144H。

如果希望用到 16K LEs,需要采用非兼容型号的 prepare 设计流程,类似 AG10K/16KSDE176 系列。 Supra 里选择 AG16KL144A 这个新型号。

五、 软件开发流程(Compatible 模式)

先用 Quartus 基于 Cyclone IV EP4CE15F23 为基础完成原始设计。管脚位置分配可先清空。新建一个文本格式的管脚分配文件,命名为.ve。(可以用记事本编辑),编辑 ve 文件加入 FPGA 的 IO位置设置,这里需要参考 AG10KL144 的管脚位置, ve 文件格式如下(管脚设计名称+空格+封装管脚名称),例如:

| rst PIN_24 clk PIN_23 led[0] PIN_31 led[1] PIN_32 …… |

新建一空目录作为 AG16KL144A 的项目目录。 打开 AGM Supra 软件, 在此目录中新建工程。 执行 Tools-Prepare。选择原 Quartus II 项目目录, Device 选 AG16KL144A,并选择编辑好的 ve 文件后,点击 Run。正确运行后会生成 af_prepare.tcl 等文件。

AGM FPGA的主要型号:

TQFP封装:

CPLD——AGRV2KL100, AGRV2KL64,AGRV2KL48;

FPGA——AG6KL144, AG10KL144, AG10KL144H, AG16KL144, AG16KL144A;

SOC —— AG10KSDE176, AG16KSDE176, AG16KSDE176G,这几个型号都是内置SDRAM和Cortex-M3,广泛应用于LED接收卡等场合。

BGA封装: AG10KF256, AG16KF256;

目前各个系列FPGA和MCU,都有相应的开发板及相应配套的开发指导教程。