- 1MySQL基础总结_mysql根据性别对员工进行分组

- 2Context Capture10.20 安装教程(附安装包)

- 3在线设计数据库表用Itbuilder,极简易用真香!!!_数据库表设计工具

- 4uniapp:完成商品分类页面(scroll-view),左侧导航,右侧商品_uniapp左侧导航右侧内容

- 5一篇文章教会你搭建Hive分布式集群_hive集群搭建

- 6数据库系统概述之数据库的安全性_]链路加密所需密码设备数量相对较少,容易被非法监听者发现并从中获取敏感信息

- 7【Android】保留elevation层级效果,舍弃阴影效果

- 8从零开始学习大模型-第一章-大模型是什么_大模型如何入门教程

- 9卷王之王---MySQL最强篇 面试必备_卷王 数据库

- 10计算机程序员的职业能力_程序员需要掌握的技能

两级跨导放大器(OTA)设计思路(一)_七管两级ota设计参数调整,满足

赞

踩

首先先介绍:跨导放大器(operational transconductance amplifier, OTA)是一种将输入差分电压转换为输出电流的放大器,因而它是一种电压控制电流源(VCCS)。 跨导放大器通常会有一个额外的电流输入端,用以控制放大器的跨导。 高阻的差分输入级、可配合负反馈回路进行工作的特性,使得跨导放大器类似于常规运算放大器。

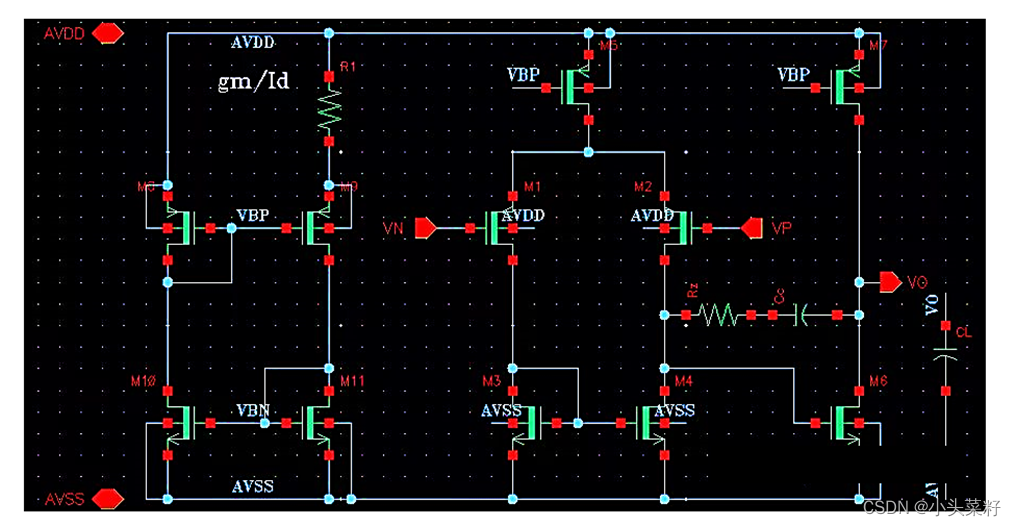

两级Miller补偿OTA

OTA的设计一般分成两个步骤,其一是根据设计需求选择需要的电路结构,其二是根据电路指标结合计算结果确定电路中器件尺寸并进行仿真迭代。

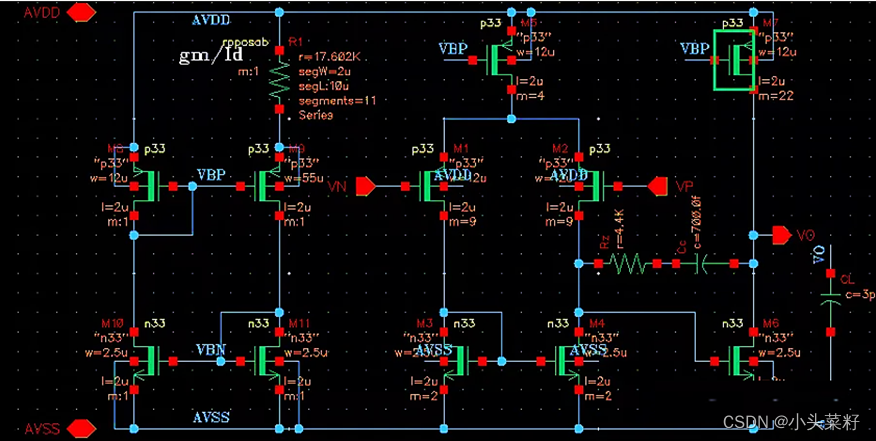

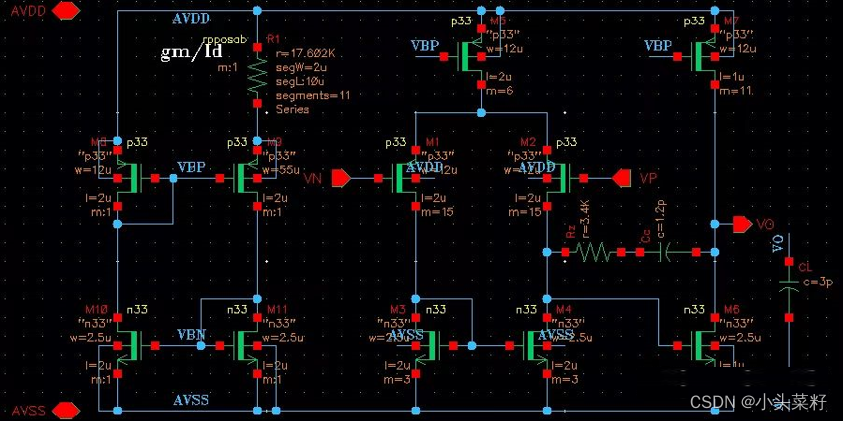

上述电路是最简单的两级OTA结构,左侧结构是电流偏置产生电路,中间是五管结构的差分输入对,右侧是共源极输出,其中包含一个跨接在第二级输入与输出之间的补偿结构。

两级OTA设计指标

| 参数名 | 指标 |

| 负载电容 | 3pF |

| 电源电压 | 2.8V |

| 静态功耗 | <2mW |

| 开环直流增益 | 80dB |

| 相位裕度 | >60° |

| 转换速率 | >30V/us |

| 输入共模电压 | 1.4V |

| 单位增益带宽积 | >30MHz |

根据上面的设计指标,结合相应的计算公式,以gm/Id作为参数重新表示各指标的计算公式。

开环直流增益:

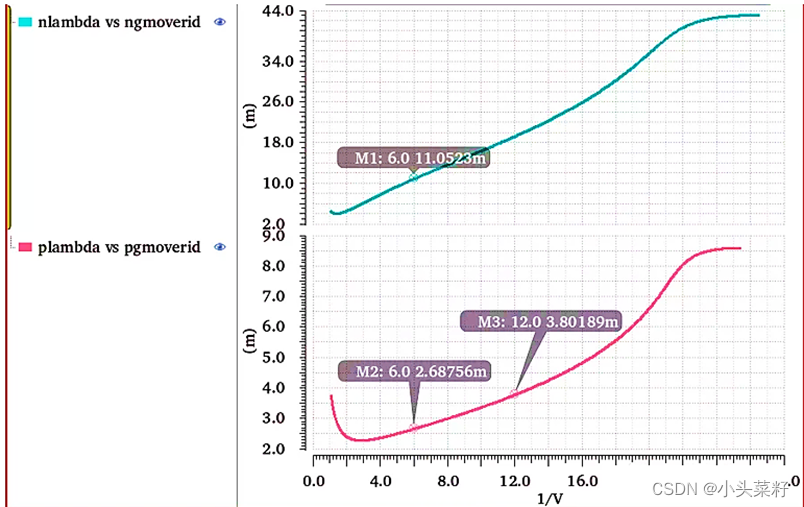

开环增益跟第一级、第二级电路的gm/Id值有关,同时与NMOS、PMOS的沟道长度调制系数 λn 和 λp 有关(假设所有MOS管的栅长一致,相同类型的MOS管沟道长度调制系数一样)。

通过选取器件栅长同时调整 M2 和 M6 的gm/Id值即可调整该电路的开环直流增益。

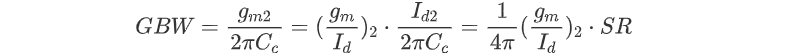

单位增益带宽积和转换速率的关系:

注意:上面公式成立的条件是摆率由第一级电流和Miller电容限制,除此之外摆率还有可能受输出节点限制,所以第二级静态电流会取得相对大一些,保证摆率不会受到第二级偏置电流和输出节点电容的限制。

根据单位增益带宽积和转换速率的关系公式,可以由单位增益带宽积或者转换速率的指标确定第一级输入管gm/Id的最小范围。

另外,根据参考资料推导,可以确定满足相位裕度要求时Miller电容 Cc 满足:

![]()

根据输入电压和功耗要求,可以求出所有支路电流之和需要满足: Itot ≤ 700 μA 。

参数计算

前面已经有了各指标的表达式,下面可以首先选取某个参数作为初始设计指标,小目习惯以开环直流增益做为设计起点。

为了提高电流镜结构电路的匹配型,需要让所有电流镜结构的MOS管工作在饱和区同时保持gm/Id值一致,这里为了利用之前设计的电流源偏置电路,取所有MOS管的L=2um.

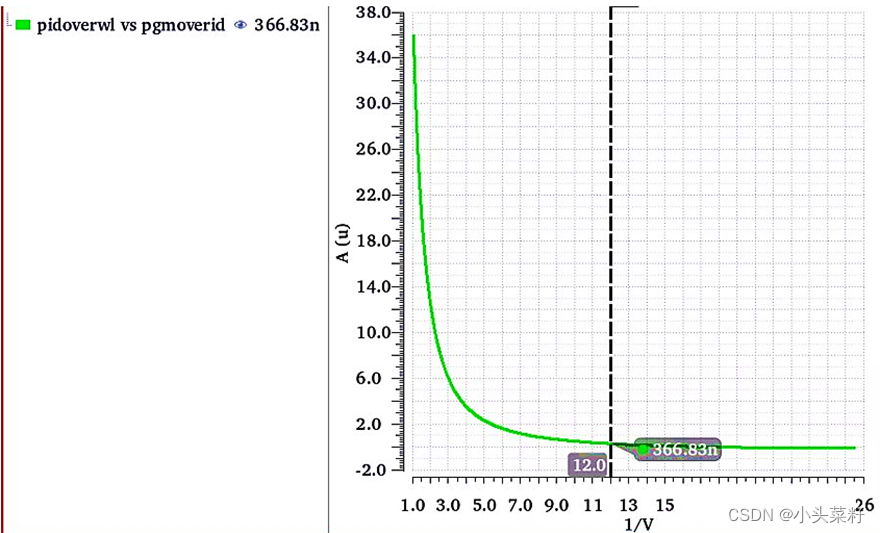

选择 M3−7 的gm/Id=6,为了提高输入对管的匹配性(输入管取稍小的过驱动电压),并且获得一定的电压增益,取 M1−2 的gm/Id=12.

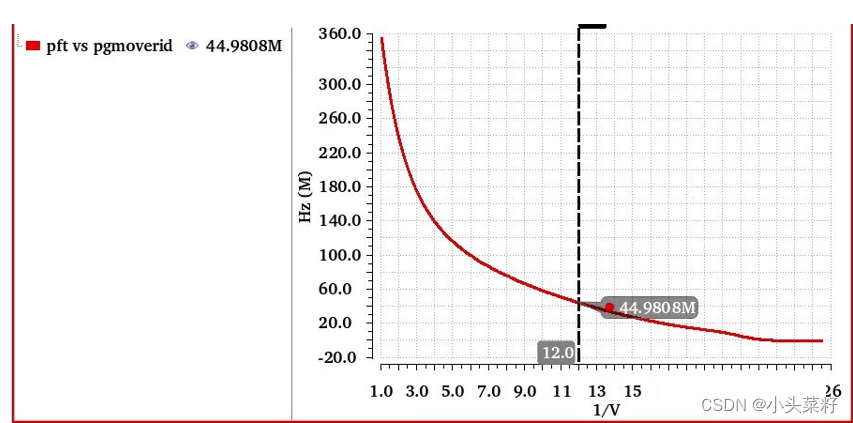

通过曲线可以看到,满足上面参数的MOS管对应的沟道长度调制系数分别为: λn=0.012 和 λp=0.004 (同一类型的器件取最大值,留出一定裕量).

经过公式验证,按照上面的参数取值,开环直流增益的手算结果大约为:109dB,满足设计指标中80dB的要求。

取Miller电容为0.7pF,根据SR的要求,可以得到第一级电路的静态电流最小约为:21uA,第二级电路的静态电流最小约为:110uA.

结合电流源偏置电路的输出电流(10uA),为了方便这里分别取第一级电路的总静态电流为40uA;第二级电路的总静态电流为220uA.

通过GBW和SR的表达式,结合输入对管的gm/Id取值,可以计算电路的SR大约为:57V/us,GBW值满足设计指标,大约为:54MHz左右。

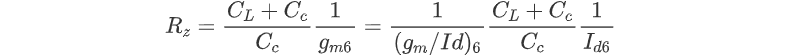

用调零电阻产生的零点抵消第二极点的位置,根据公式:

按照上面电流与gm/Id的取值,代入公式,可以计算调零电阻取值约为:4K.

确定器件尺寸并仿真验证

按照器件gm/Id的值可以计算器件的尺寸,具体内容如下面器件标注所示。

电流镜和电流负载的尺寸可以直接根据电流源偏置电路的尺寸按比例计算,输入对管的尺寸查表计算。

按照图中标注的尺寸,对电路进行仿真分析,分别进行dc、tran、stb仿真,验证实际仿真与设计值的偏差。

首先确认所有器件工作在正确状态,各器件的gm/Id仿真值与设计值对比:

其中输出级电路电流值与设计偏差较大,但是对设计指标影响不大,先不做调整,可以看到总体来看仿真值与设计值偏差不大。

设计结果与指标对比

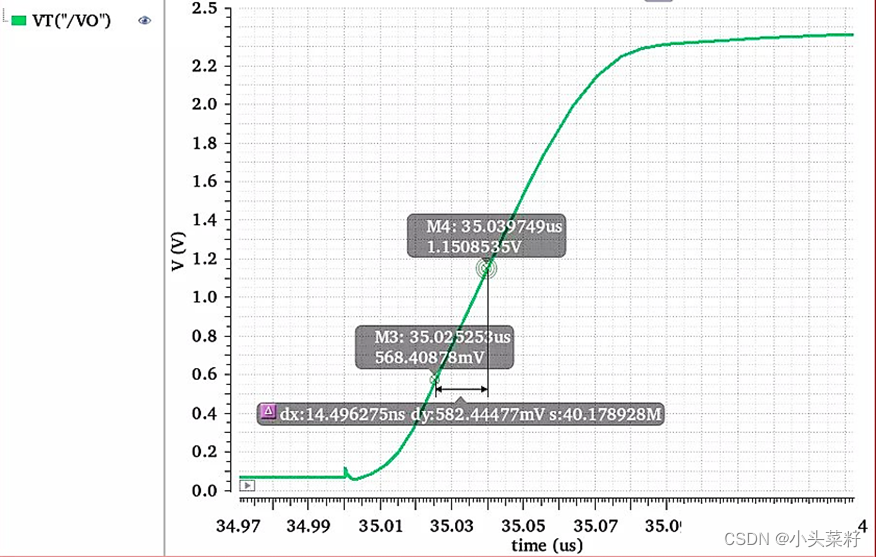

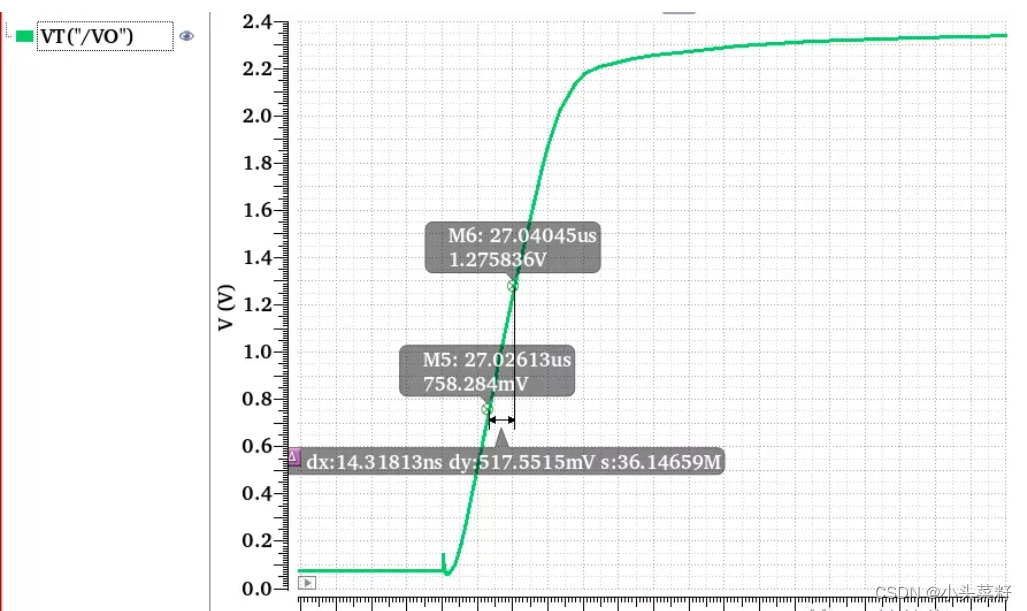

通过查看瞬态仿真结果,计算电路的压摆率是否满足设计指标并思考设计与仿真结果之间的误差来源。

仿真得到的SR约为40V/us,按照计算应为57V/us,通过查看仿真结果,实际第一级输出节点电容值大约为1.1pF,按照仿真得到的电流:41.7uA计算,SR大约为:38V/us,与仿真值比较接近。

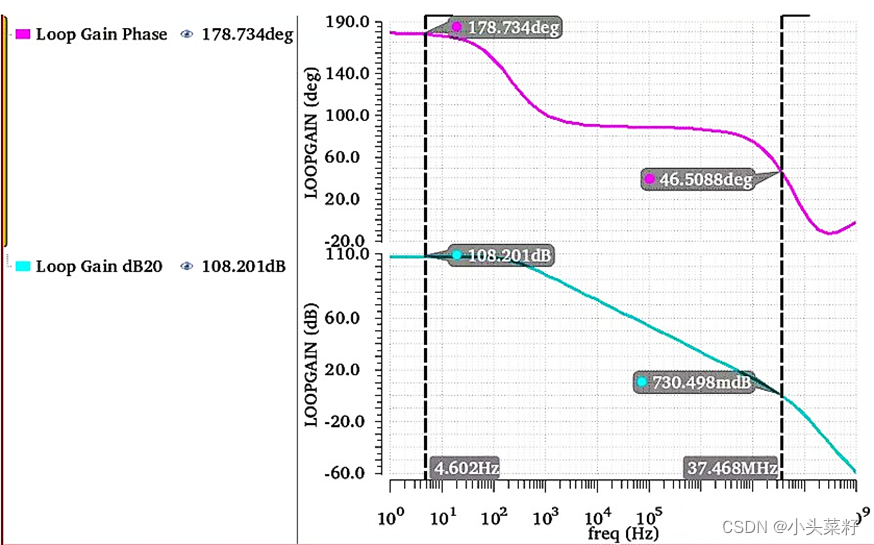

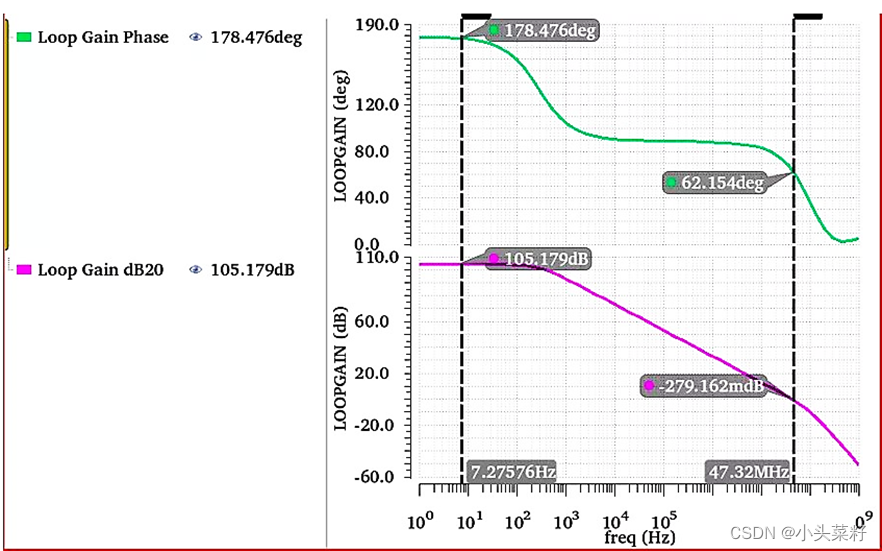

通过stb仿真验开环直流增益,从仿真结果可以看到,设计的电路开环直流增益为:108dB,增益带宽积大约为:37MHz,相位裕度大约为:45°。

开环直流增益的差别很小,因为我们在估算增益时虽然把器件的沟长调制系数取大了,但是实际电路仿真结果中器件的gm/Id值比设计值偏低。

增益带宽积(GBW)的差异与SR的差异一致,一方面由于第一级电路的输出节点电容比预估的大,另一方面由于第一级器件L=2um,从ft曲线可以看到,在此条件下PMOS管的速度本身受限达不到预期值。

相位裕度的设计差异和仿真差异最大,考虑到手算时并未考虑到Miller电容对次极点的影响,可以留更大的设计裕度,将Miller电容取到1.2 pF甚至更大.

同时由于输出级器件L=2um,输出阻抗较大,也有可能造成次极点所处频率不高,可以考虑取输出级器件L=1um,并调整W保证gm/Id值不变。

Miller电容的增加导致输出摆率在第一级输出受限,可以提高第一级电路的电流,比如将电流从 40 uA提高到 60uA.

第二次迭代仿真

在第一次仿真的基础之上,重新调整部分指标,其中Miller电容取到1.2pF,第一级电路的静态电流增加到60uA,第二级器件L=1um。

器件尺寸如上图中所示,再次仿真,验证设计指标与仿真结果的差异,首先通过tran仿真验证SR.

由于在增大Miller电容的同时提高了第一级电路的偏置电流,所以摆率受影响比较小,依然在设计预期内。

stb的仿真结果显示,由于减小了第二级电路的器件L所以增益有所下降,但是相位裕度达到设计目标。

同时可以使用SR与GBW的公式或者直接使用GBW的计算公式验证仿真结果与计算值是否匹配,此时SR的值应取第一级输出节点的SR,通过仿真得到大概为56MHz左右,与公式相吻合。

至此,我们采用gm/Id的设计方法完成了一个简单OTA的设计,并且通过两次仿真迭代满足了前面给出的设计指标,设计中虽然理论计算与仿真结果有一定偏差,但是考虑寄生效应和单极点系统的等效过程,误差尚可接受。

每个人的电路设计习惯都不一样,本文的分享只是给大家提供一个设计思路,仅供参考,有其它更合理的想法欢迎大家在留言中分享。