- 1语音中的响度,音调与音色的决定因素_基波分量和谐波分量的表达式

- 2LoRa无线通讯,让光伏机器人实现无“线”管理

- 3python如何生成互动窗口_10年Python大牛倾力打造系统学习互动活动流程图

- 4Three.js-光线投射(raycaster)

- 5大厂调整考勤,996不再是福报,程序员该乐了?_互联网大厂会重回996工作制

- 6图解Java数据结构之队列_java 队列 数据结构

- 7[渝粤教育] 江苏医药职业学院 急救护理 参考 资料_二、单选题10、患者男性,45岁。特殊工种,炎热夏天在高温下工作数日,近日出现

- 8vue使用axios中post/get请求params/data总结_axios get params

- 9PaddleNlp无法安装解决方案_juypter paddlenlp

- 10数据结构基础

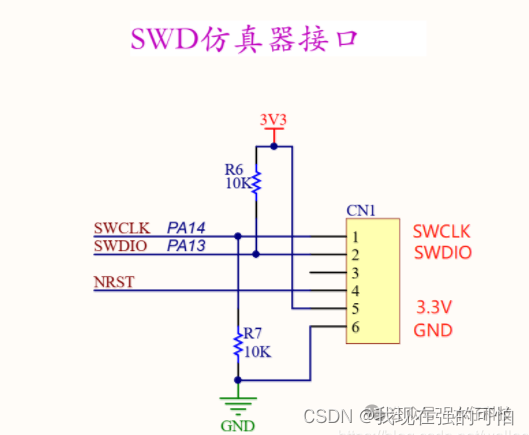

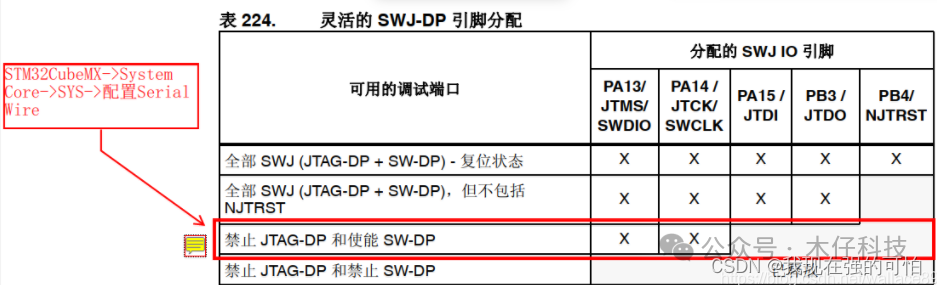

STM32单片机的SWD下载口为什么要加上下拉电阻_swclk

赞

踩

在STM32单片机中,SWCLK(Serial Wire Clock)和SWDIO(Serial Wire Data Input/Output)是调试接口SWD(Serial Wire Debug)中的两个关键信号线,用于实现微控制器与调试器之间的通信。

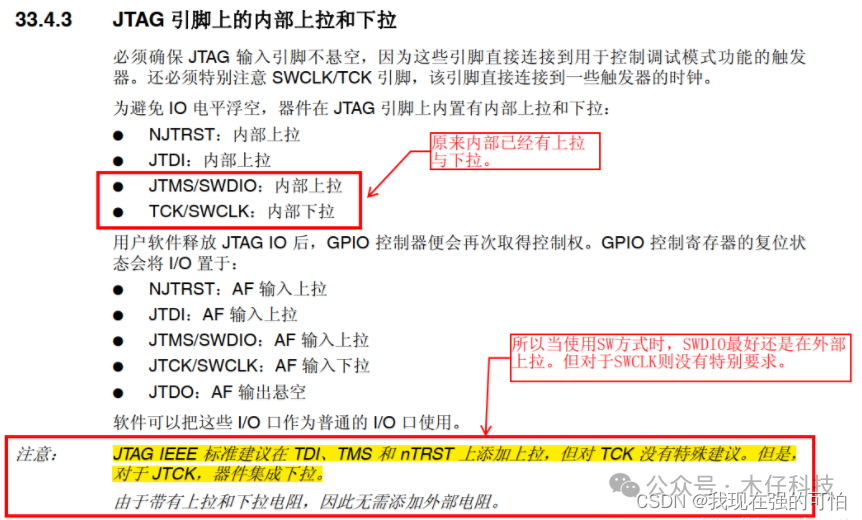

SWCLK(时钟线)加下拉电阻到GND的原因:

- 保持状态:

•当SWD通信不活跃时,SWCLK线如果没有外部信号驱动,如果没有下拉电阻,其状态可能会处于未知状态(浮空)。添加下拉电阻可以使SWCLK在不使用时保持稳定的低电平状态。

- 减少噪声:

•下拉电阻可以抑制SWCLK线上的噪声,防止线路在没有明确驱动时因外部干扰等原因而随机翻转。

- 确保信号清晰:

•在SWD通信中,时钟信号的边沿触发数据采样。下拉电阻有助于保证时钟信号的上升沿和下降沿更加陡峭,从而提高通信的可靠性。

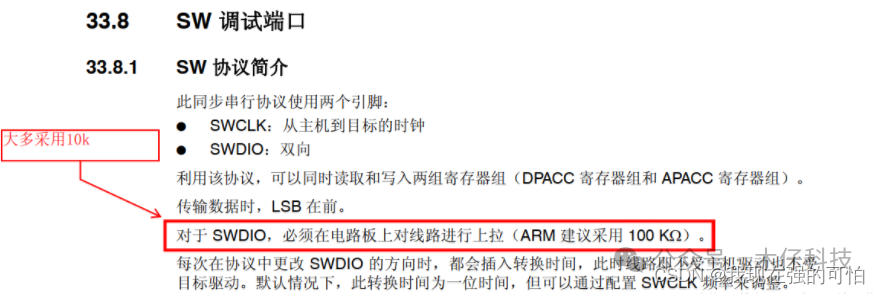

SWDIO(数据线)上拉到3.3V的原因:

- 保持状态:

•同样地,SWDIO在未被驱动时,上拉电阻使其保持高电平状态,明确了数据线的默认状态。

- 提高噪声免疫能力:

•上拉电阻可以帮助抵抗线路噪声,确保在没有数据传输时,SWDIO维持在一个确定的逻辑电平,避免因噪声干扰导致的误判。

- 匹配逻辑电平:

•单片机内部通常工作在3.3V的逻辑电平,上拉电阻到3.3V是为了与MCU的逻辑电平匹配,确保数据线在高电平状态下有足够的电压。4. 提高信号质量:

•对于开放式集电极(Open Drain)或推挽输出(Push-Pull Output)的I/O口,上拉电阻可以提供一个确定的高电平电压,提升信号的品质和稳定性。

SWCLK和SWDIO可以不带上下拉电阻吗?

STM32单片机的SWCLK和SWDIO引脚在设计上内部通常带有弱上拉和下拉电阻,这意味着在某些情况下,不额外添加外部上下拉电阻也可以正常工作。

但是,为了确保更好的信号完整性、降低噪声干扰和提高通信可靠性,尤其是在长距离传输、嘈杂环境或者某些特定应用场景下,通常建议在设计时在外围电路中添加合适的上下拉电阻。

对于SWCLK(Serial Wire Clock)引脚,通常会建议添加外部下拉电阻,尤其是在线路没有被驱动时,下拉电阻可以确保时钟信号有一个稳定的低电平状态,防止线路浮动造成不确定状态。

对于SWDIO(Serial Wire Data Input/Output)引脚,虽然内部有一定的上拉能力,但如果线路较长、环境噪声较大,或者需要提高通信稳定性时,外部上拉电阻可以增强信号质量,尤其是在SWDIO作为输入时,外部上拉电阻能够提供一个清晰的高电平状态。

当然,在决定是否添加外部上下拉电阻时,还需要参考具体的应用环境、线路长度、电磁兼容性要求以及STM32芯片数据手册的建议。在很多实际应用中,为了保险起见,开发板和产品设计中往往会保留上下拉电阻

本文转自-----木仔科技 公众号