- 1成为鸿蒙生态开发者,从这门认证起步_鸿蒙职业认证怎么弄

- 2全开源外卖小程序源码搭建教程附源码下载_外卖小程序源码下载

- 3vivado 物理优化_vivado ultraram

- 4大数据面试题—包含真实面经(压力拉满)_大数据 群面

- 5就算不偷盗,也让你看看计算机里常用的有那些软件--常用软件序列号

- 6LabVIEW阀门运动PCT测试

- 7数学建模常用代码总结-Python&MATLAB_数学建模 代码

- 8昇思MindSpore 25天学习打卡营|day5

- 9unity发布webGL压缩方式的gzip,使用nginx作为web服务器时的配置文件_unity gzip

- 10Leecode热题100---104:二叉树的最大深度(广度/深度优先)

ZYNQ7000 学习(三十一)PL 中断 PS 的原理和实现_ps与pl中断

赞

踩

实现步骤

1 PL 与 PS 交互方式

(1)PS配置 PL.

(2)PS通过 AXI总线读写 总线读写 PL的寄存器或者储。( 的寄存器或者储。( 的寄存器或者储。( AXI LITE 读写外设的寄 读写外设的寄 存器, AXI FULL 读写 PL部分的片内或者外存储器)。 部分的片内或者外存储器)。 部分的片内或者外存储器)。

(3)PL中断 PS。

(4)PL主动读写 PS部分的 DDR3存储器。

2 中断原理介绍

中断是一种外设通过打正在进行 CPU处理的程序, 而立即执行中断服务处理的程序, 而立即执行中断服务来实现外设与处理器之间的深度耦合方式。 下图为 UG585 介绍的 ZYNQ 的中 断处理器框图

这里看到虚框内的 PL部分可以通过 SPI 这部分,产生中断最终可以通过 这部分,产生中断最终可以通过 这部分,产生中断最终可以通过 这部分,产生中断最终可以通过 ICD灵活分配到两个处理器上。

每一个中断 源或者组都对应ID,处理器运行程序通过 ,处理器运行程序通过 ,处理器运行程序通过 ID号来 区分是哪个具体中断 源产生的,UG585列出了中断源与中断号的对应关系。

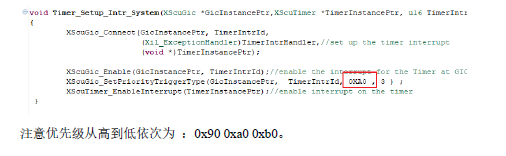

另外我们也可以在 VIVADO的配置里面找到这种对应关系。用中断号起来 的配置里面找到这种对应关系。用中断号起来 之后,在处理器 看来就是和其他中断(比如我们之前将的 GPIO中断和 中断和 私有定 时器的中断)同样对待了,注册程序和处理框架也就基本一。 时器的中断)同样对待了,注册程序和处理框架也就基本一。 时器的中断)同样对待了,注册程序和处理框架也就基本一。 PS端程序 的编写是类似。

一, 关于触发方式以及边缘模下保持时间。

PL中断 PS触发方式可以在 PS端编程控制对应寄存器设置为高电平触发和上升 端编程控制对应寄存器设置为高电平触发和上升 边缘触发。在这个我们认为中断源的满足和不分别用 1和 0表示。 高电平就是中断的条件满足了,表现为逻辑 高电平就是中断的条件满足了,表现为逻辑 1。上升边缘触发表示之前从中断没 。上升边缘触发表示之前从中断没 有发生到中断的这个跳变,也就是从逻辑 0到逻辑 1的跳变。在 的跳变。在 Z7系统中 允许设置 PL的中断触发方式。 的中断触发方式。

当设置电 当设置电 平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高平触发时候, 只要中断条件一直满足也就是请求线上电高则触发处理器产生中断。

当设置上升边缘触发时候,且仅中断条件从不满足到的跳变也就是 当设置上升边缘触发时候,且仅中断条件从不满足到的跳变也就是 当设置上升边缘触发时候,且仅中断条件从不满足到的跳变也就是 中断请求线表现成了一个上升边缘,并且保持高电平至少 2个 CPU_2X3X周期 (也就是说 4个以上处理器的时钟周期)。 就会产生触发处理器产生中断。

这两种中断触发方式强调的侧重点不一样,电平触发强调的是特定中断事件之要没有撤销就要反复进行处理。比方说在具体应用中一个来自外界的报警信号,只要报警信号存在说明危险没有被消除,需要继续中断处理器,继续处理。上升,缘触发方式强调特定中断事件发生了,对于这个此次特定发生的中断事件,处理器只要做一次处理就可以。如果外设还要再次请求中断处理器,则需要将中断再次产生一个上升边缘进行进行请求。

这里我们将做结合例子来加深一下认识。