热门标签

热门文章

- 1win10远程桌面连接-出现身份验证错误解决方法_authentication error! right click on forts -> prop

- 2Spark Partition方式_spark repartition 能保证同一个key的数据分配到一起

- 3CSS选择符和可继承属性

- 4苹果电脑关于网络参数的查询_macos ifconfig

- 5计算机网络——网络传输优化实战_tcp syncookies

- 6kafka数据库oracle对比,互联网行业“中年”危机_kafka数据库类似的数据库

- 7古墓丽影:暗影缺少winmm.dll文件无法启动全方位深入解决方案介绍_古墓丽影暗影win11无法启动

- 800后说我不会自动化测试,3个问题直接给他问趴下..._100条自动化测试脚本需要多少工程师执行

- 9[转载]静态成员函数能不能同时也是虚函数?

- 10CANoe -选项卡 和 功能区_canoe快捷键

当前位置: article > 正文

【FPGA】Verilog 编码实现:与非门 | 或非门 | 异或门 | NAND/NOR/XOR 行为验证_nor xor

作者:不正经 | 2024-06-14 00:11:07

赞

踩

nor xor

写在前面:本章主要内容为了解和确认 NAND/NOR/XOR 门的行为,并使用Verilog实现,生成输入信号后通过模拟,验证每个门的操作,并使用 FPGA 来验证 Verilog 实现的电路的行为。

本章目录:

0x03 4-input AOI(AND OR Inverter) gate

Ⅰ. 前置知识

0x00 与非门(NAND)

如果所有输入均为High (1),则输出为Low (0),在其他情况下,将产生High (1) 输出。

- NAND 是 AND 运算符的否定结果

布尔表达式中以 "负乘法" 形式表现:

![]()

0x01 或非门(NOR)

如果所有输入均为 Low (0),则输出为 High(1),其中一个输入为高 (1) 则产生低功率 (0)。

- NOR 是 OR 运算符的否定结果

布尔表达式中以 "否定合" 形式表现:

![]()

0x02 异或门(XOR)

如果 两个值不相同,则异或结果为1。如果 两个值相同,异或结果为0。

![]()

Ⅱ. 练习(Assignment)

0x00 4-input NAND gate

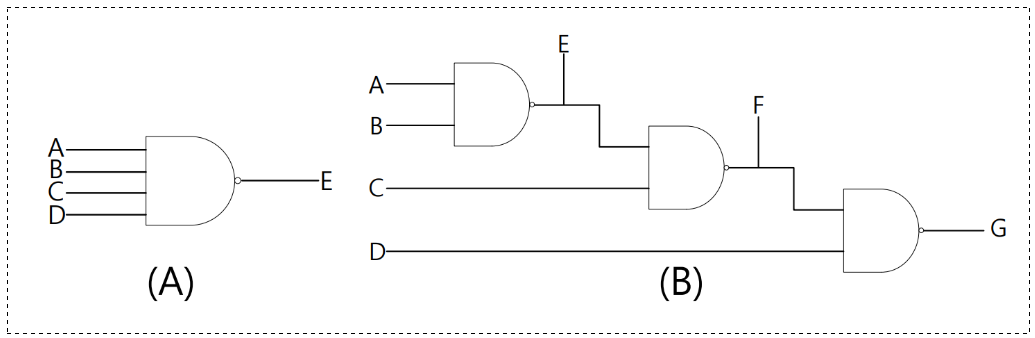

比较 AB 的布尔表达式,完成 A 和 B 的 Verilog 代码,通过 Simulation 结果进行比较。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/不正经/article/detail/715388

推荐阅读

相关标签

Copyright © 2003-2013 www.wpsshop.cn 版权所有,并保留所有权利。