- 1【科学计算包NumPy】NumPy数组的基本操作_numpy库对数组的操作与运算

- 2云原生最佳实践系列 5:基于函数计算 FC 实现阿里云 Kafka 消息内容控制 MongoDB DML 操作_函数计算 fc,创建函数,这里能够配置我云服务器中自己搭建的mongodb吗

- 3码农的自我修养 - ARM编译器的区分_宏定义判断是不是mingw

- 4iptables使用limit控制新建连接速率_iptables limit

- 5turbo码_信息论-Turbo码学习

- 6【已解决】git 设置不参与合并的文件_git不合并某个文件

- 79款最新文生图模型汇总!含华为、谷歌、Stability AI等大厂创新模型(附论文和代码)_文生图大模型有哪些

- 8Java获取当前时间的几种方式_java获取当前日期

- 9二、buildroot-2015.02编译根文件系统支持Qt_buildroot 2015

- 10(附源码)SSM学生宿舍管理系统JAVA计算机毕业设计项目_宿舍管理系统怎么在其他电脑运行

闲话电子设计之100条

赞

踩

1、BUCK芯片延时上电的方法:

1)缓启动芯片

2)SS引脚电容变更引起延时

3)RC阻容延时

电容谐振峰,受电容自身参数影响。

2、反射/EMI

源反射=(Zs-Zline)/(Zs+Zline)

终端反射=(Zload-Zline)/(Zload+Zline)

有损耗=传输线模型

无损耗=TLine传输线模型

过冲/振铃,EMI源头

地弹,是EMI的主要源头之一

3、DDR3

DDR3的VREF,需要重视稳定电压,周边是否干净

1)上电后,不停的刷,静态DRAM

2)上电后,不听的刷,动态DRAM

3)误码仪:E5052A,信号分析仪

4)DDR:同步,需参考时钟

5)TTL/CMOS:不适合高速

A:电平高,信号边沿较长,不适合速度高于200MHz以上信号

B:传输距离短:信号为单端信号,传输路径易受干扰

C:功耗高:器件有静态功耗/动态功耗

因为电平高,所以进化出 高速电平,一般采用差分技术,比如 LVDS(3.125Gbps)/LVPECL(±800mV 10Gbps)/CML(±800mV 10Gbps);

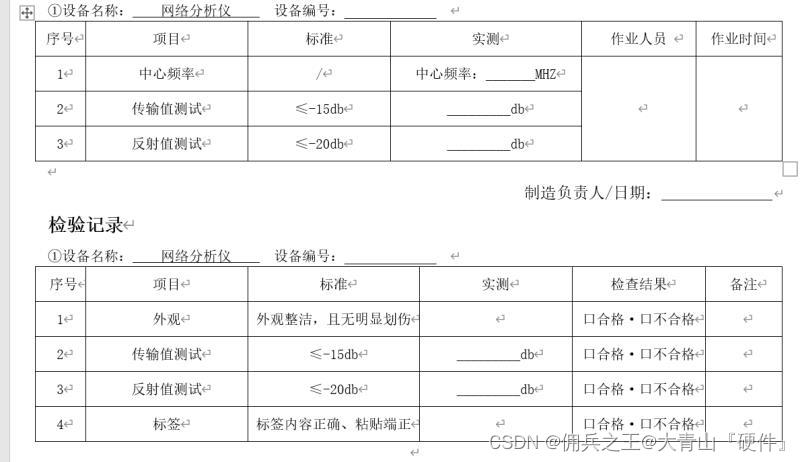

6)线宽(50Ω/同层/),线长,线间距,包地,叠层

波形的低电平过高,C过大/R过大

扇出越多,驱动力越慢

根据负载情况,选择驱动力

ESR小一些,适合高频使用

过孔载流有限

磁珠摆放位置

叠层的厚度差异

5、FPGA编程-Verilog

先看RTL图,再看仿真

6、过孔,也称为金属化孔

7、数据:抖动/skew/Tr/建立/保持/Tf

8、ESD:阻抗路径,R变小/C变小/Shield/安规/EMC/PDN/

9、ZYNQ:

1、标注 data的专用引脚,没有标注data0、data1等,是否可以随意调换,没有固定线序,还是有专用文档,有固定的设置?

2、PS端专用引脚,是否可以作为常规IO引脚,

3、PS端专用引脚,PS部分程序控制这些引脚,还是PL和PS都可以控制这些引脚?

10、10AX027H4F34I3SG(Altera功耗计算):

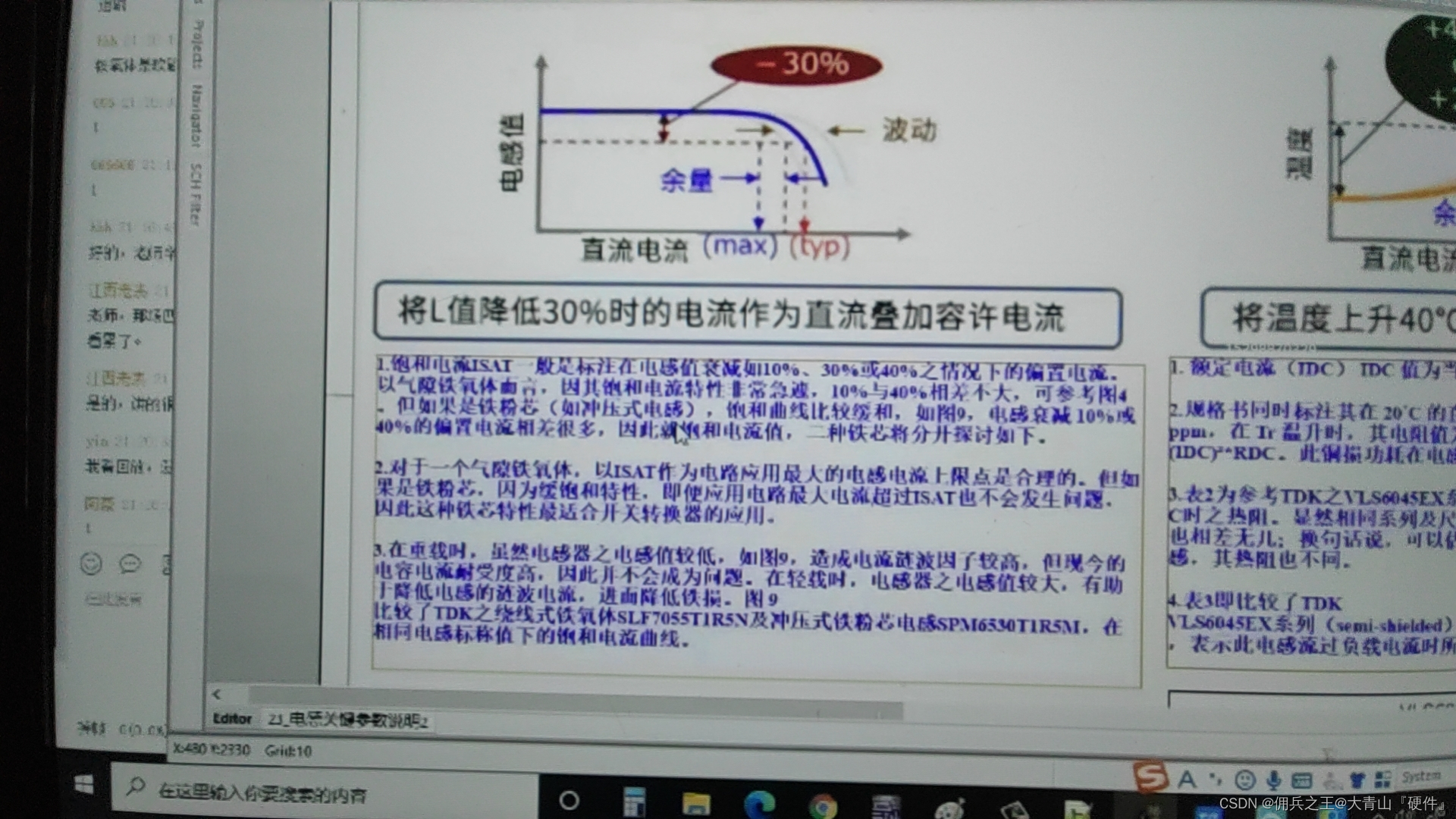

11、电感

1)

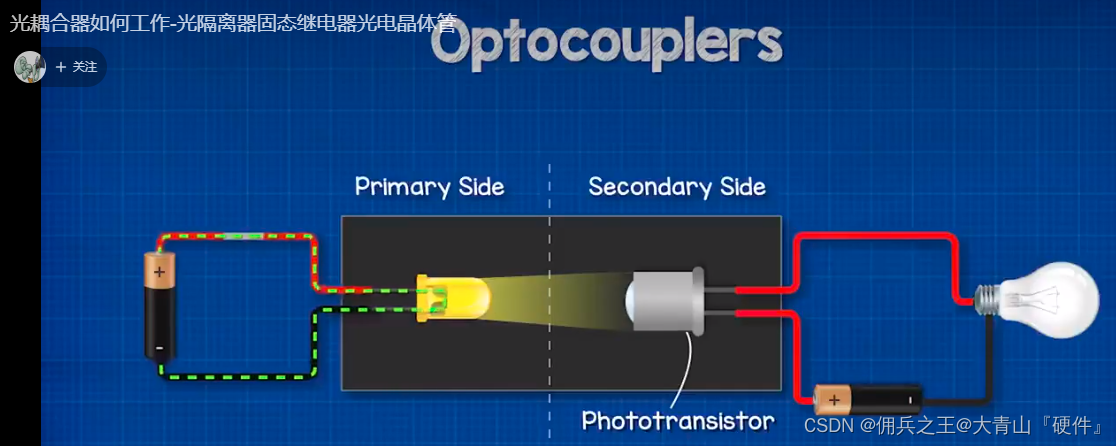

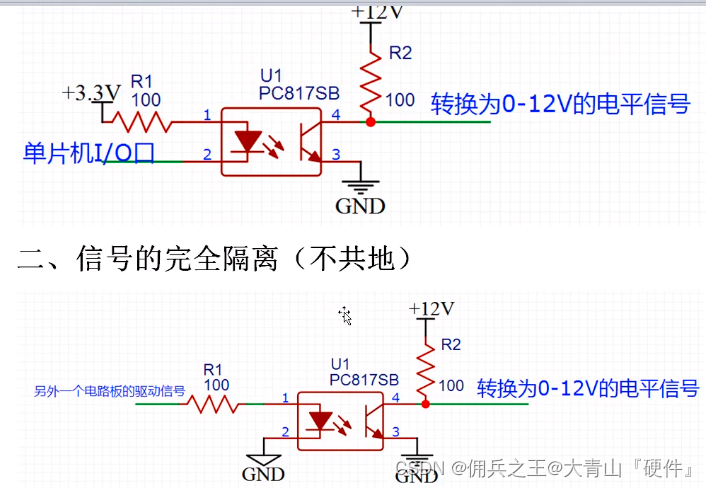

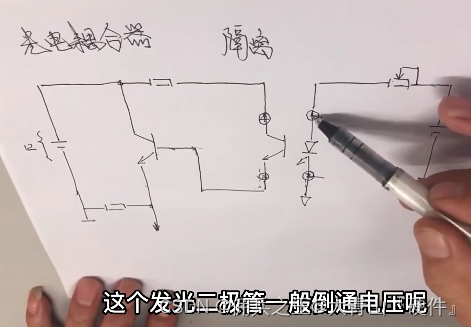

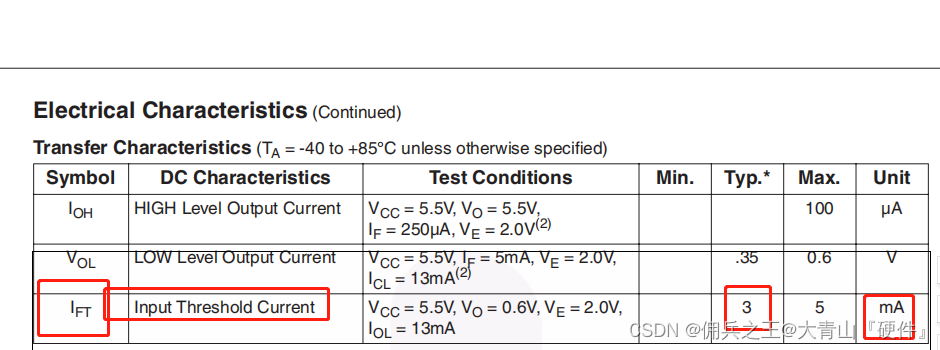

12、光耦工作:

出乎意料的,温度影响了光耦启动

IF有范围需求

13、RS-232/422/485标准

13.1RS232

1) RS-232电平标准:

逻辑“1”电平:-3V~-15V

逻辑“0”电平: +3V~+15V

2) RS232传输距离

因为电气干扰传输线,不加缓冲器,最大传输距离15米(距离短);

3)RS232传输速率

---->为了解决上面的问题,RS422/485出现;

RS422:

1)RS422电平标准:

2) RS422传输距离

3)RS422传输速率:

传输速率:10Mbps

传输距离极限4000英尺(1英尺=12inch英寸=304.8mm,4000英尺=1219米),此时速率100Kbps;

最多接10个接收器

RS-422是一种单机发送、多机接收的单向、平衡传输规范,被命名为TIA/EIA-422-A标准。

---->为了解决单机发送、双向通信,出现了RS485

RS485:

1)RS485电平标准:

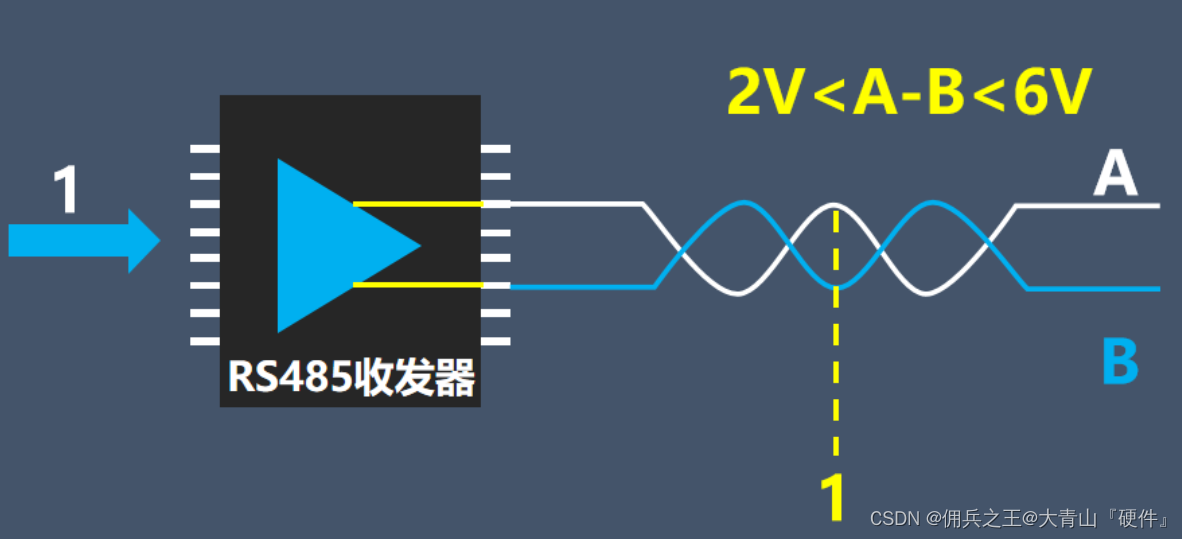

TX传输时,输出端A/B之间的电平标准

逻辑“1”:VA-VB=+2V~+6V

逻辑“0”:VA-VB=-2V~-6V

三态:高阻

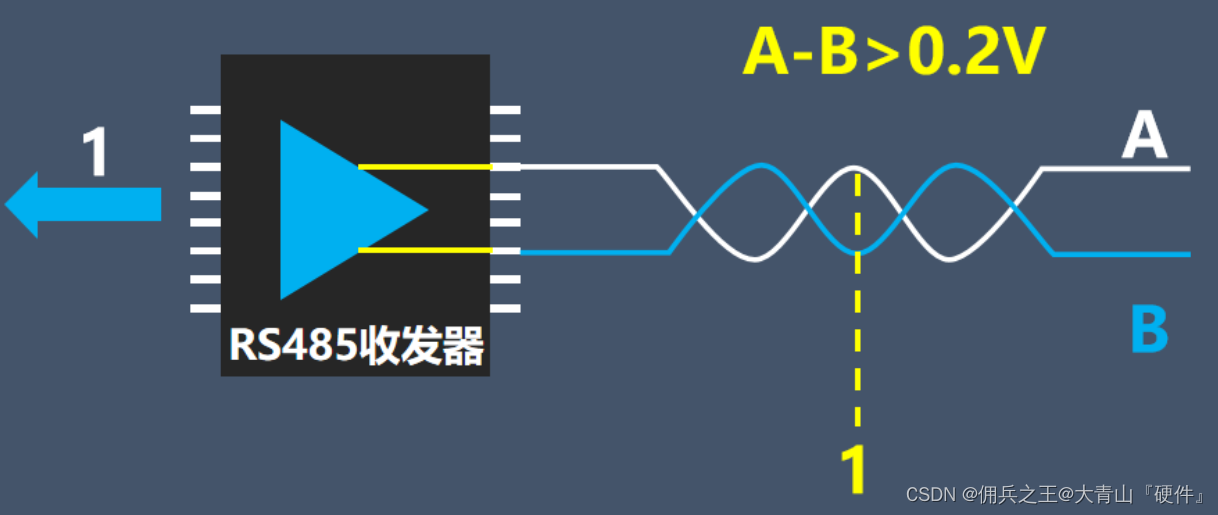

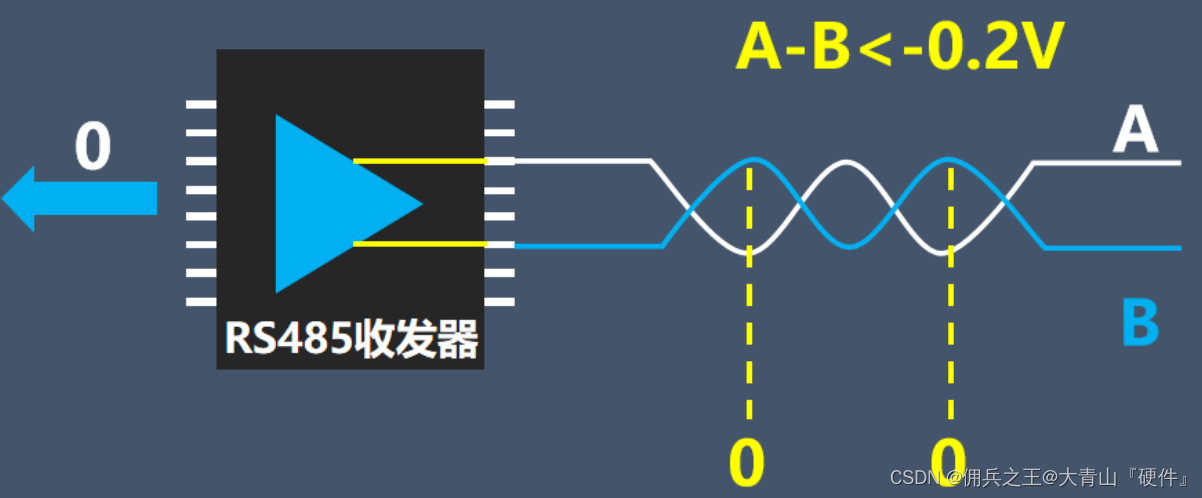

RX接收时,输出端AB之间电平:

逻辑“1”:VA-VB>200mV,RX端为高电平;

逻辑“0”:VA-VB<-200mV,RX端为低电平

三态:没有信号传输时,-200mV< VA-VB <200mV;

2) RS485传输距离

最大传输距离1219米时,传输速率20Kbps

最大传输速率10Mbps

双绞线15米时传输速率1Mbps

如果采用光耦隔离,通信速率一般还受到光耦响应速度的限制;

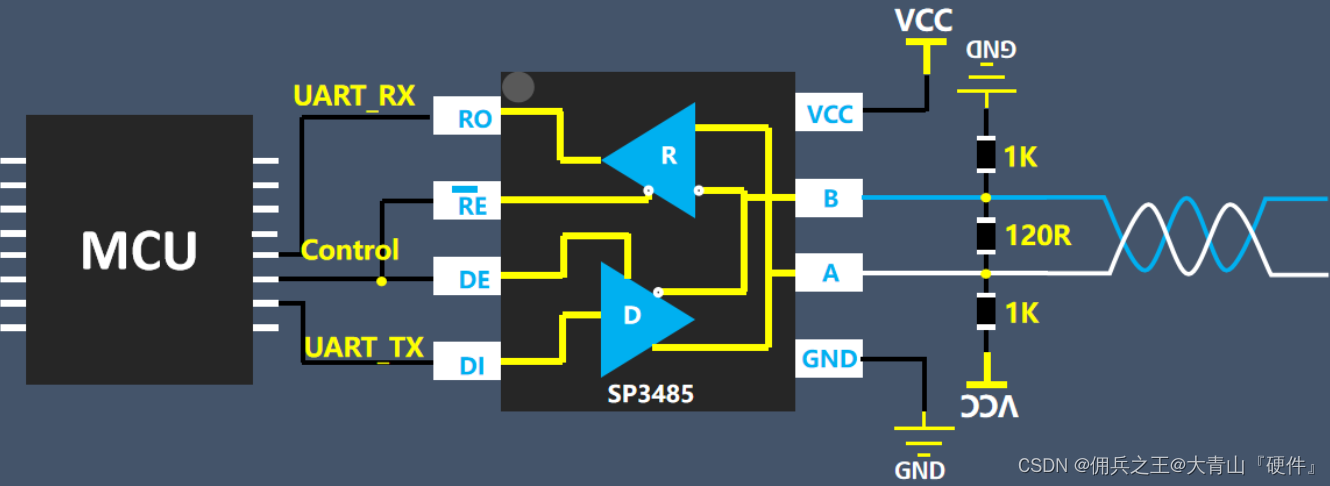

多个RS485,A/B端需要各加1个终端匹配电阻,阻值为传输线缆的特征阻抗,一般为120Ω;

一条总线最多可接256个 485设备

终端匹配电阻丝为了消除在通信线缆中的信号反射

1)阻抗不匹配/不连续引起

2)收发器与传输电缆之间的阻抗不匹配,主要是空闲时,整个网络数据胡乱

有了该电阻,增强通信抗干扰性,提升可靠性,通信顺畅;

3)RS485传输速率

RS485:半双工方式,增加了多点、双向通信能力,即允许多个发送器连接到同一条总线上,同时增加了发送器的驱动能力和冲突保护特性,扩展了总线共模范围。

RS-232、RS-422与RS-485标准只对接口的电气特性做出规定,而不涉及接插件、电缆或协议,在此基础上用户可以建立自己的高层通信协议。

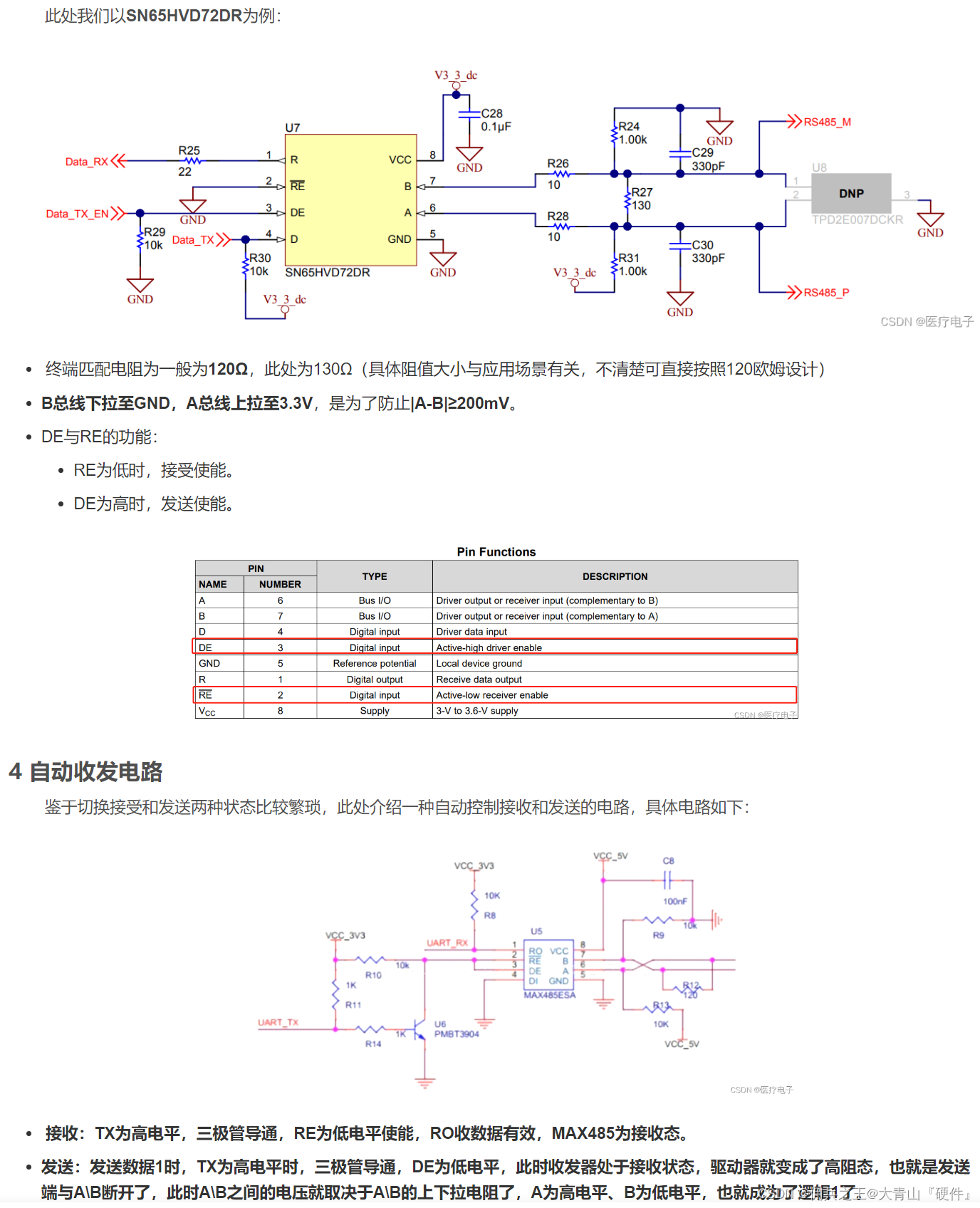

RS485芯片:SP481E/SP485E/SP3485/3.3V供电的工业芯片MAX3485/5.0V供电的MAX485

总线空闲时控制信号应该为低电平,使485收发器芯片处于接收状态。如果A和B都处于高阻,其状态是不确定的,可能会导致RX上接收到错误的随机数,所以这个电路中A信号一般加上拉电阻,B信号一般下拉电阻。

A和B之间的120欧电阻的作用是消除485总线上的信号反射,一般在485总线的两端加就可以了,不用每个设备节点都加。

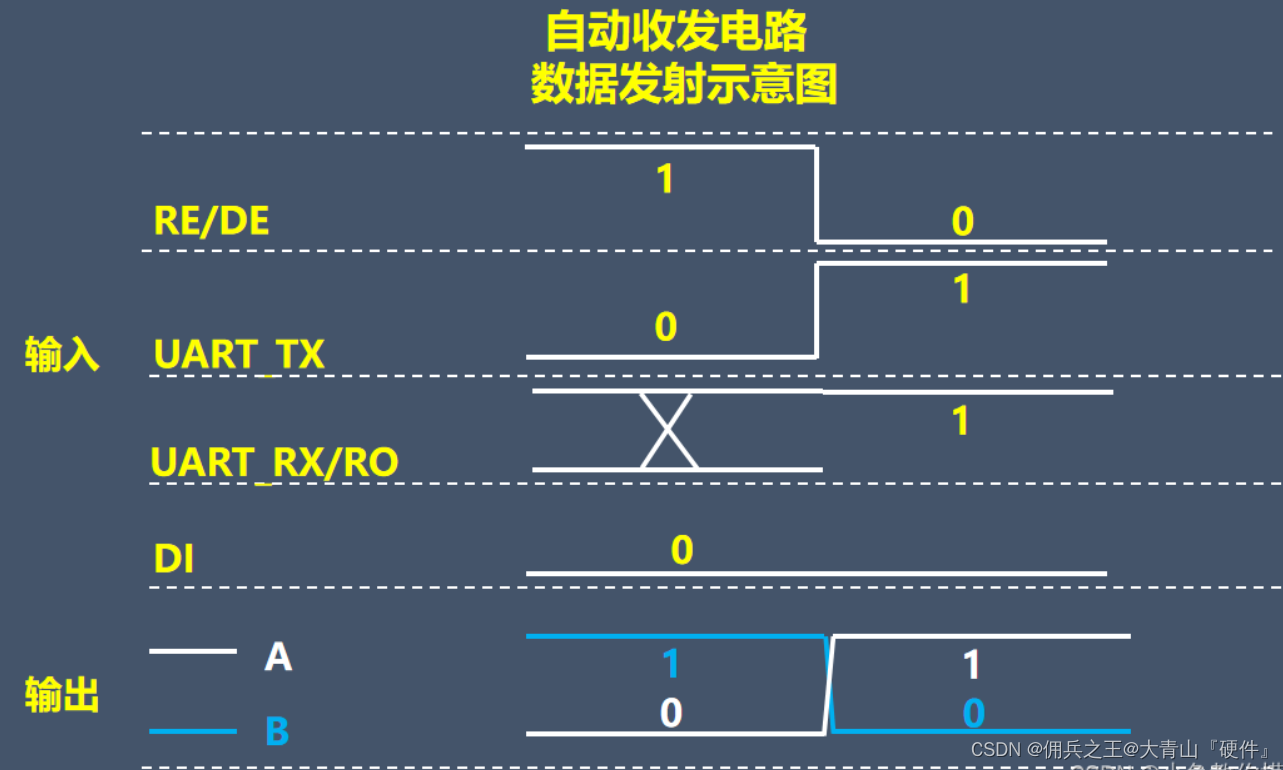

自动收发电路

与上面电路有所不同的是自动收发电路的RE和DE信号接到一起,由TX控制其电平,TX为高电平时,RE和DE为低电平;TX为低电平时,RE和DE为高电平。DI是接到一个固定的低电平。

当TX为低电平,Re和DE就为高电平,发射使能,RX为一个高阻状态,RX电平由外部上下拉决定,一般RX为高电平。DI为低电平,所以输出的A电压小于B电压(也就是输出了485的逻辑0)

当TX为高电平,Re和DE就为低电平,接收使能,A和B本来应该是高阻的状态,又因为A有上拉电阻,B有下拉电阻,所以A电压大于B电压(也就是输出了485的逻辑1),这时RX是高电平

X不发送数据时,TX默认为高电平,Re和DE就为低电平,接收使能,

当485总线上A电压-B电压大于200mV时,RX为高电平,

当485总线上A电压-B电压小于-200mV时,RX为低电平。

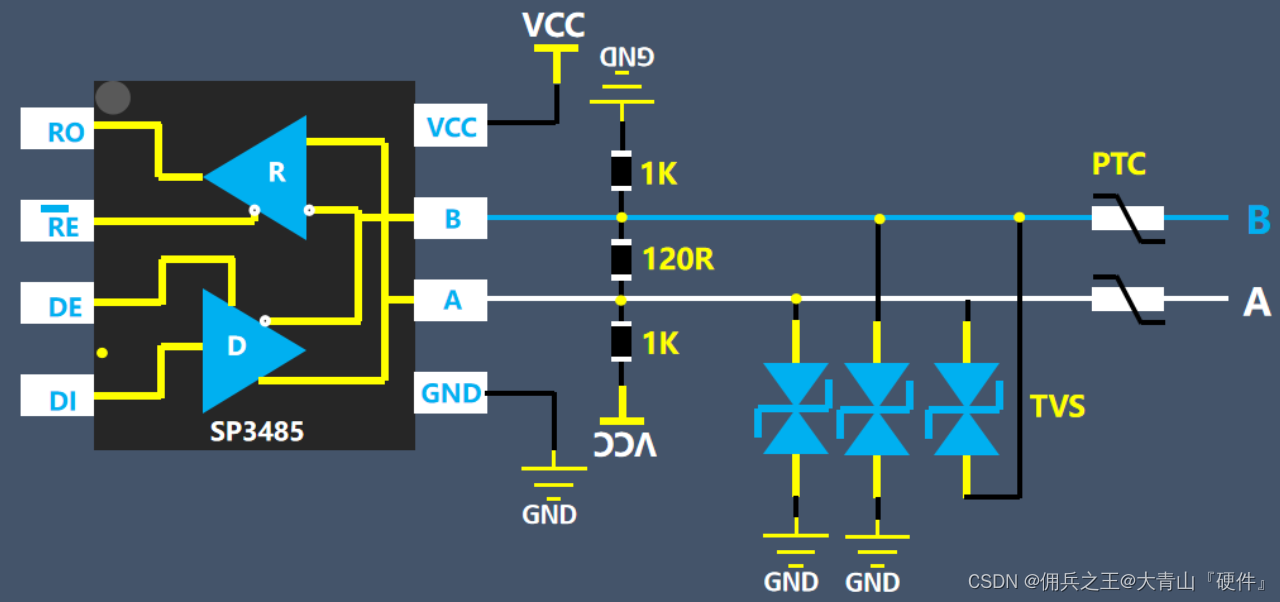

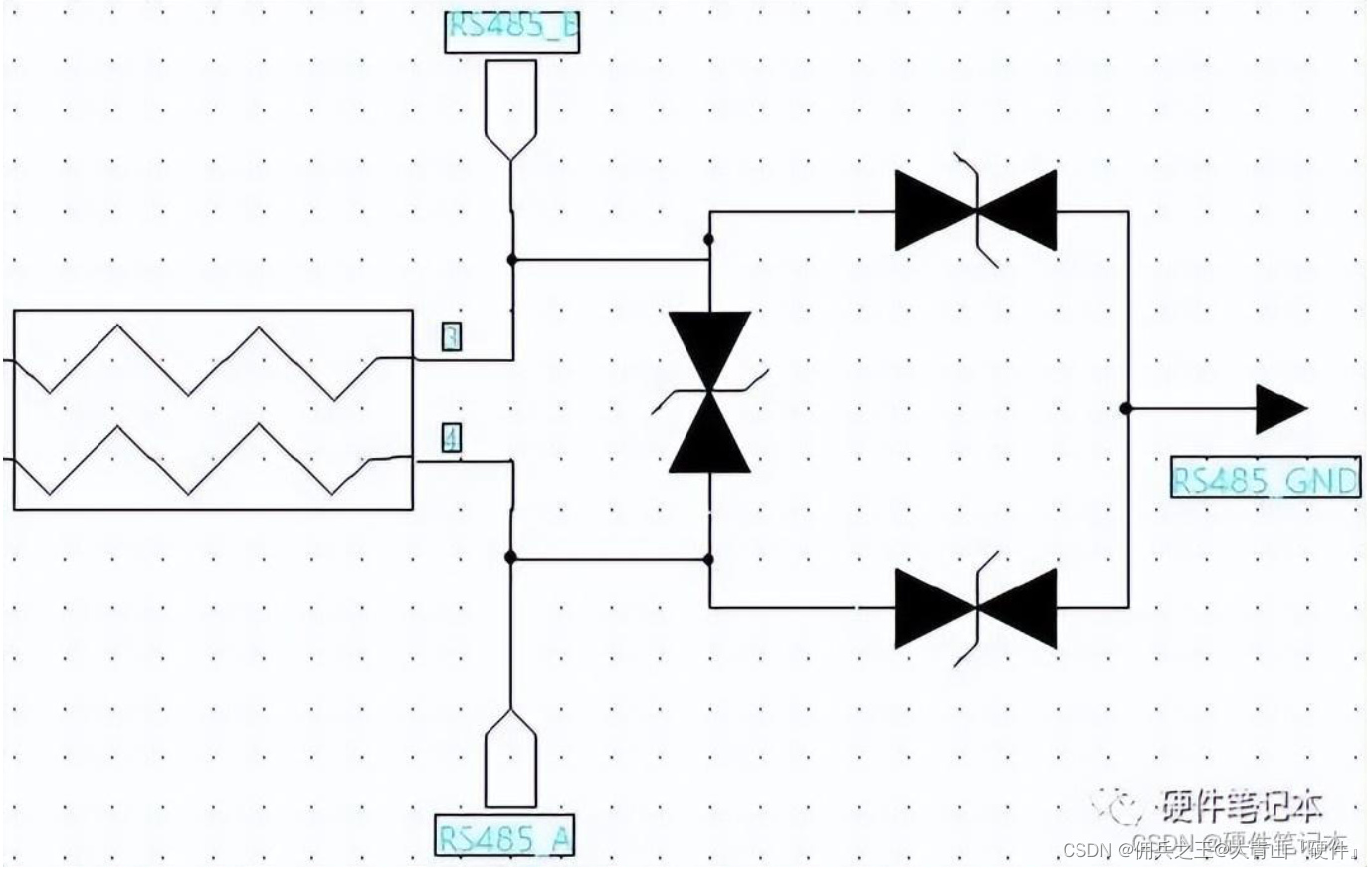

对于485接口的ESD和浪涌防护,一般会在信号线上加TVS管,然后也可以在信号线上加上PTC自恢复保险丝。

工业设计

485需要做防雷考虑、瞬态过电压抑制、阻抗匹配等,一下是常用设计,可供参考。

(1)芯片部分

(2)接口部分

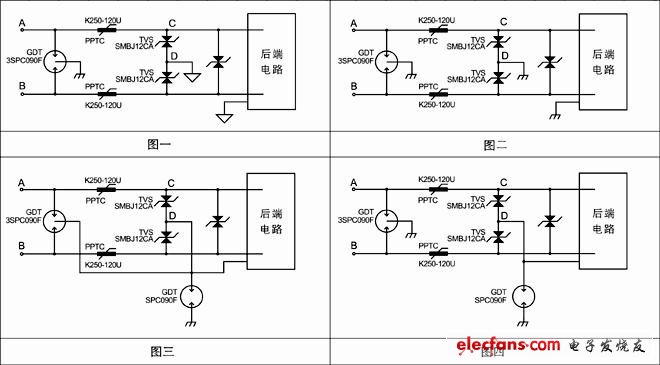

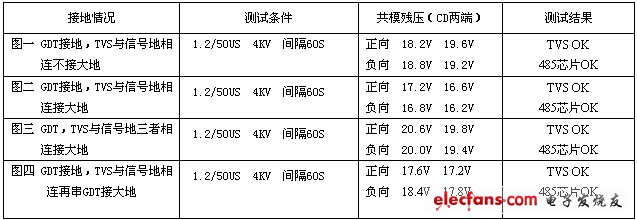

下面就是四种RS485防雷保护接地电路原理图,GDT(陶瓷放电管)接地,TVS(瞬态抑制二极管)接地,后端电路的是信号地,大家从图中可以很方便的看到接地的情形。

关于上面四种方案的测试数据

电缆为什么会有分布电容,会有什么影响?有什么解决办法?电缆达到一定的长度,电容效应就会显现出来。电容结构就是靠近两个电极,中间是绝缘部分。这就是分布电容。低频时对电路几乎没有影响。高频就要考虑分布电容的影响。 根据初中物理电容原理知识可知,两导线之间的距离越小,电容量越大。485传输线一般使用双绞线,两线之间的距离小,电容效应就越明显。在某些特殊的时候,信号0使得分布电容有充足的充电时间,而信号1到来时,由于分布电容电荷的存在,来不及放电,导致信号传输错误,从而使整个网络性能降低。 解决这个问题有两种办法:A.降低数据传输的波特率;B.使用分布电容小的电缆,提高传输线的质量。

6.电缆为什么会有分布电感,会有什么影响?

一定长度电缆本身具有的电感值,这是根据电磁感应原理,导线的电感与长度成正比。电缆越长,电感越大。根据XL=2πfL,当输入信号频率一定时,电感越大,感抗越大,对信号的阻碍作用越强。

如何提高RS485抗干扰能力?

A、在RS485的A、B以及AB之间各并连一个TVS,当脉冲信号较高时,干扰电压被TVS钳位,达到保护RS-485收发器的目的;

B、在输出端串联一个共模电感,滤除共模干扰。

10.直接用网线连接电脑和485网口可以正常通讯吗?

不可以。485是串口通信协议,电脑是TCP/IP网络接口是两种不同的通讯协议。需要提供USB转485这样的转接板,来实现485串口与网络接口的数据双向传输,使得串口设备能够立即具备TCP/IP网络接口功能,连接网络进行数据通信。

这种转接小板网上很容易买到,100元以内就能搞定。

11.网线和485线的区别

.14、学习模拟电路分四步:

首先一定要先把分立元器件学好,学透。比如:电阻、电容、二极管、稳压管、三极管、比较器、运放、MOSFET等。分立元器件在模拟电路中是最基本也是最小的组成部分。这好比人的组织细胞,要想研究人就要先研究组织细胞。

其次,需要懂得利用这些分立器件的工作特性和条件来组成一个小的单元电路,学会让这个单元电路正常工作。这就好比各个组织细胞组成了人体的各个器官,模拟电路的各个单元电路正常高效工作就好比人体器官的正常健康;

再次,学会将各个单元电路有机地协调运转,联调可靠运行,这就好比各个器官的协调运动组成了一个健康充满活力的有生命的人。

最后,学会设计和调试电路,借助示波器等测量仪器让电路的参数调整合理并最优化。这就好比利用仪器对人体进行体检,并根据体检报告进行调理,使人精神饱满,健康充满活力。

所以说我一直拿设计电路比喻有生命体的人。一个好的设计电路好比一个充满活力的人,一个设计不好的电路就好比亚健康的人。所以说我们设计电路需要赋予它的生命,需要让它强壮,这是我们设计电路的终极目标。

15、如何培养设计电路的思路呢?能不能介绍一些好的方法。

设计电路思路特别重要,那么思路又是如何得来的呢?每当我们看到一个比较复杂的电路时,首先想到的是别人是如何把这么复杂的电路设计出来的?为什么我不能?我怎么才能够设计呢?

从大的方面讲一般我们分三步走:

第一步,先学会看别人的电路;

第二步,学会根据自己的需要修改别人的电路;

第三步,自己独立设计电路。

具体方法如下:其实任何一个复杂的电路都是由一个个小的电路模块组成的。

首先,我们先把一个小的单元电路搞懂,而这个单元电路又是由一个个元器件组成的,所以我们先把这个单元电路中元器件弄通,而掌握这些元器件无非是电流、电压、功率、工作条件等这几个参数;

然后把这些器件放在一个单元单元电路中根据前面说的那几个参数分析他们在电路中的作用。然后一定要多动手,建议大家把每个元器件都要换个参数测试一下,而且每次只能更换一个元器件,观看电路有什么变化,思考为什么会有这样的变化,然后逐渐更换所有元器件,重复以上,这样你会对电路中的这些元器件有了很深刻的感悟,而且动手做过的东西你不会忘记的。这样对你积累经验十分有帮助。

其次,把两个单元电路进行联调,观察调试过程出现的问题,直至调通。最后把多个单元电路进行联调,直至调通。这样由简单到复杂循序渐进地学习和掌握电路设计经验,而这些经验作为数据库会存进你的大脑,以后你在设计电路时需要什么电路你大脑就会立即跳出来你曾经做过的这些电路,让你电路设计起来特别轻松,游刃有余。

16、遇到问题的处理方法

在公司里让我最得意的产品也很难找出,因为每一次的技术突破都会让我还没有来得及兴奋就又投入到新的技术突破项目中去。我们在公司的任务不是直接针对产品研发,而是不断进行新的技术的突破,为公司未来几年的产品研发做技术铺垫。而对我们的考核就是研发出来的技术要新颖而且独特,我曾不用MCU成功做过一款无位置传感器的三项BLDC控制器,如果用单片机处理就比较容易,但全部硬件来做就会遇到许多麻烦:旋转转子位置如何检测?换向逻辑译码电路如何设计?六个状态的控制信号如何周期性地锁存?过零点信号如何由120°转换成90°?如何进行相位跟踪?如何进行启动、低速、高速三种状态的自动切换等等。有人说这么复杂为什么还要全硬件去做?因为硬件的速度特别快,很多信号处理同时进行,而软件是单步执行的,时效性不强。而正是这次尝试取得了新的发现,使得我们更新了软件算法,重新用单片机做了一个项目,保持了我们的技术优势。

在设计中有时也会遇到难以解决的问题,一般如果三天也没有取得解决的话我就会把它放一放,想想与工作无关的事情,然后强迫自己从原来的思维模式中跳出来,有几次是做梦的时候突然想到了一个新的idea,然后早上起来赶紧把它记下来,到公司后赶紧做,然后把问题解决了。

17、令人记忆犹新或难忘的经历是什么?

08年进入一家日本独资企业工作,当我完成了一个项目设计,并将图纸送到日本一位资深的老工程师进行审核时,他摇摇头,把我的方案全全否决,我一下子蒙掉了,当我向他申述为什么时,他拿给我看的全是日本的法规,天哪,人家电子设计的细节都已经用法规来规范了,那我们国家在这方面的差距是多么的大。当时我最大的挑战就是设计思想需要重新塑造。严谨的设计思想以及苛刻的细节追求才是做一个世界级产品的前提,所以说落后不可怕,可怕的是思想落后。因此希望大家设计思想一定要严谨。

19、最想与将要或已经从事硬件开发的新人说些什么呢?

做硬件设计必须注意的以下三点:

第一,需要一颗安静的心,不能烦躁。

第二,需要多动手,多测量和分析波形,多总计经验,不管是别人的还是自己的。

第三,不要满足自己目前设计的电路敢于指出自己电路设计的不足,然后至少修改两次,这样才能设计出优秀的电路。

大家如有需要与我就技术问题进行沟通可以与我联系,论坛账号:@松山归人

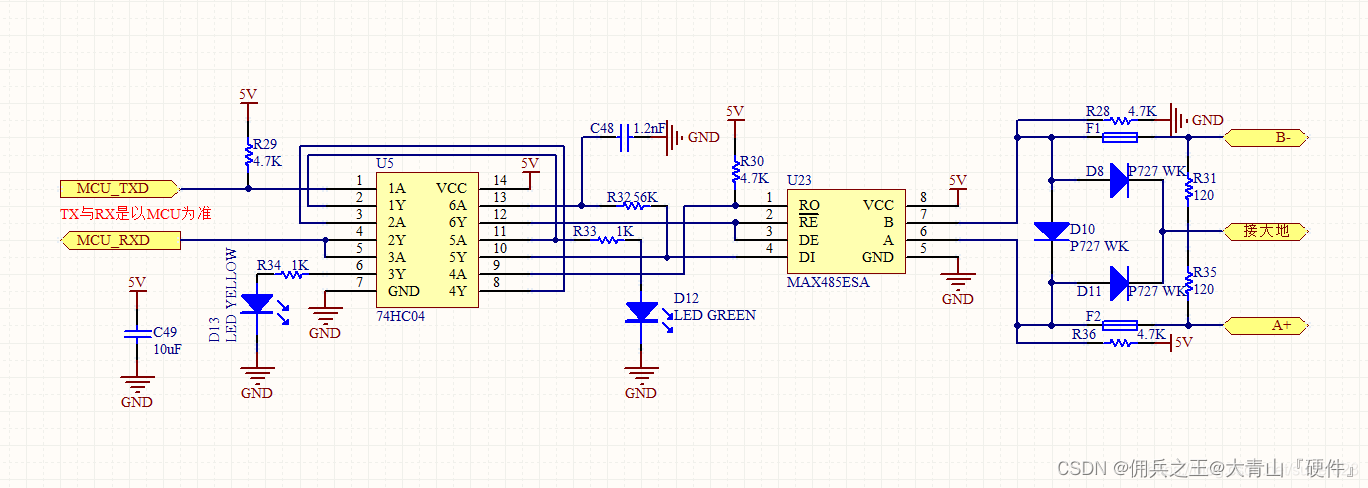

20、RS485通信

NEC公司的光耦器件PS2501芯片

任一时刻SP485R芯片中的“接收器”和“发送器”只能够有1个处于工作状态。连接至A引脚的上拉电阻R7、连接至B引脚的下拉电阻R8用于保证总线空闲时,A/B差分信号仍是确定状态,避免杂讯影响。钳位于6.8V的TVS管V4、V5、V6都是用来保护RS-485总线的,避免RS-485总线在受外界干扰时(雷击、浪涌)产生的高压损坏RS-485收发器。另外,电路中的L1、L2、C1、C2是可选安装元件,用于提高电路的EMI性能。

输出电路的设计要充分考虑到线路上的各种干扰及线路特性阻抗的匹配

在电路设计中采用稳压管 D301、D302组成的吸收回路,也可以选用能够抗浪涌的 TVS 瞬态杂波抑制器件,或者直接选用能抗雷击的485芯片(如 SN75LBC184等)。

考虑到线路的特殊情况(如某一台分机的485芯片被击穿短路),为防止总线中其它分机的通信受到影响,在MAX487EESA信号输出端串联了两个200Ω的电阻 R314、R315。这样本机的硬件故障就不会使整个总线的通信受到影响。

在应用系统工程的现场施工中,由于通信载体是双绞线,它的特性阻抗为120Ω左右,所以线路设计时,在 RS-485网络传输线的始端和末端各应接1只120Ω的匹配电阻(这是可选的,见前面说明),以减少线路上传输信号的反射。

由于 RS-485芯片的特性,接收器的检测灵敏度为± 200mV,即差分输入端 VA-VB ≥+200mV,输出逻辑1,VA-VB ≤-200mV,输出逻辑0;而 A、B 端电位差的绝对值小于200mV时,输出为不确定。如果在总线上所有发送器被禁止时,接收器输出逻辑0,这会误认为通信帧的起始引起工作不正常。解决这个问题的办法是人为地使 A 端电位高于 B 两端电位,这样RXD的电平在485总线不发送期间(总线悬浮时)呈现唯一的高电平,单片机就不会被误中断而收到乱字符。通过在485电路的A、B 输出端加接上拉、下拉电阻 R313、R312,即可很好地解决这个问题。

21、为什么要等长?

一般在PCB设计时,进行信号等长处理的原因有以下几个。

❶ 一般做等长是为了满足系统对信号组的等时,即为了满足此组内信号的时序须满足系统要求。比如对于DDR,其数据信号每8位一组,做+/-25mil处理,如果此组信号等长没有在此公差范围内,信号线长度相差太大,会导致其相对延时较长,最终导致DDR运行速率不高。

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组长度每相差6mil,其总延时在1ps。一般我们做设计时等长并不用控制的太小,控制到+/-10mil左右就已经很好了。+/-10mil 等长和+/-1mil 等长,在时间上的差异不超过 4ps,一般的IC信号裕量都不止4ps,所以做等长时没必要控制的过小,从而导致自己设计走线困难。

❷ 差分信号(差分信号分析可查看我们的公众号往期文章)等长是为了满足相位,一对差分信号相位相差180度,如果长度相差太大,会导致其相位偏移过大。

22、高速信号串接电阻的功能

高速信号线中才考虑使用这样的电阻,在低频情况下,一般是直接连接。

这个电阻有两个作用,

第一是阻抗匹配。因为信号源的阻抗很低,跟信号线之间阻抗不匹配(关于阻抗匹配,请看详述),串上一个电阻后,可改善匹配情况,以减少反射,避免振荡等。

第二是可以减少信号边沿的陡峭程度,从而减少高频噪声以及过冲等。因为串联的电阻,跟信号线的分布电容以及负载的输入 电容等形成一个RC 电路,这样就会降低信号边沿的陡峭程度。大家知道,如果一个信号的边沿非常陡峭,含有大量的高频成分,将会辐射干扰,另外,也容易产生过冲。

23、

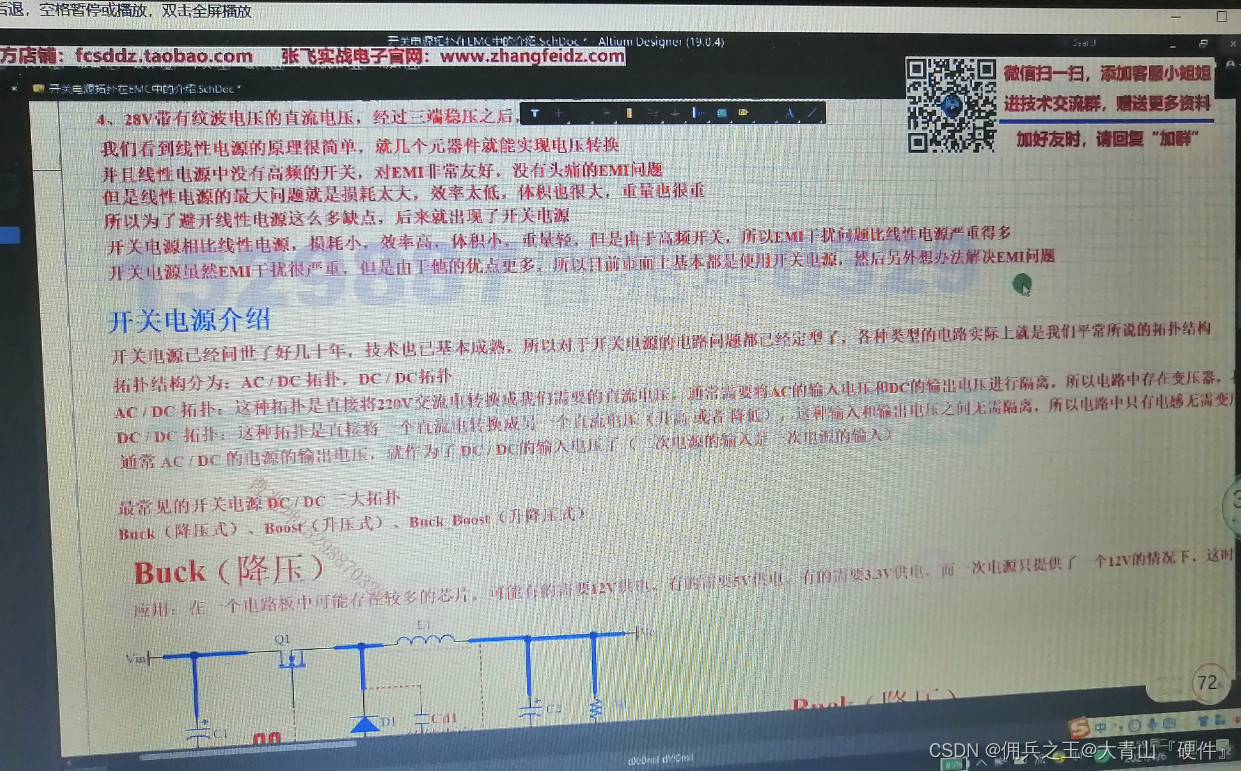

25、BUCK:

外部强烈干扰后,BUCK输出电压跌落,

电流带来的 电压跌落和压降问题

铜皮形状也有影响

自恢复时钟

26、光互联/电互联

导体损耗,电互联的有效带宽3dB,25Gbps

铜损耗 25Gbps

介质损耗/本征损耗

Tr=0.35/Fsw

27、连接器

27.1

总的显示 接地柱

28、电路仿真

multisim:大学用过,方便 (内含mulink)spice模拟

LTSpice:ADI公司软件,与PsPice模型兼容,输入激励信号比较复杂,复杂的模拟电路,设计的电路是否合理,LTspice激励获取信息会更多。所以推荐

Tina:TI公司软件

ADS:板级仿真模拟

HFSS:结构电磁场仿真

Proteus:单片机仿真

老白:电路仿真,是基于SPice模型构建。完整度+功能+看到更多模拟仿真细节推荐LTSpice+Tina

元器件特性理解不深入,仿真软件可以更详细仿真

29、高速:

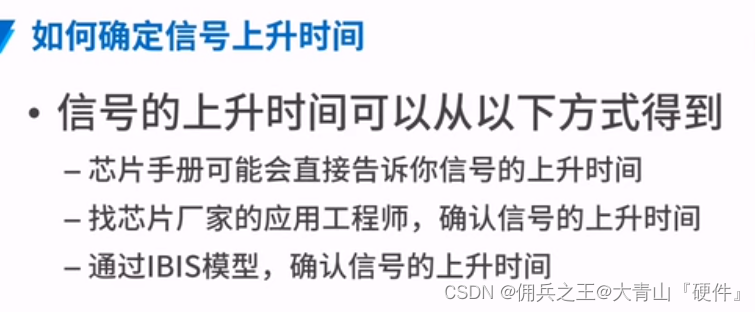

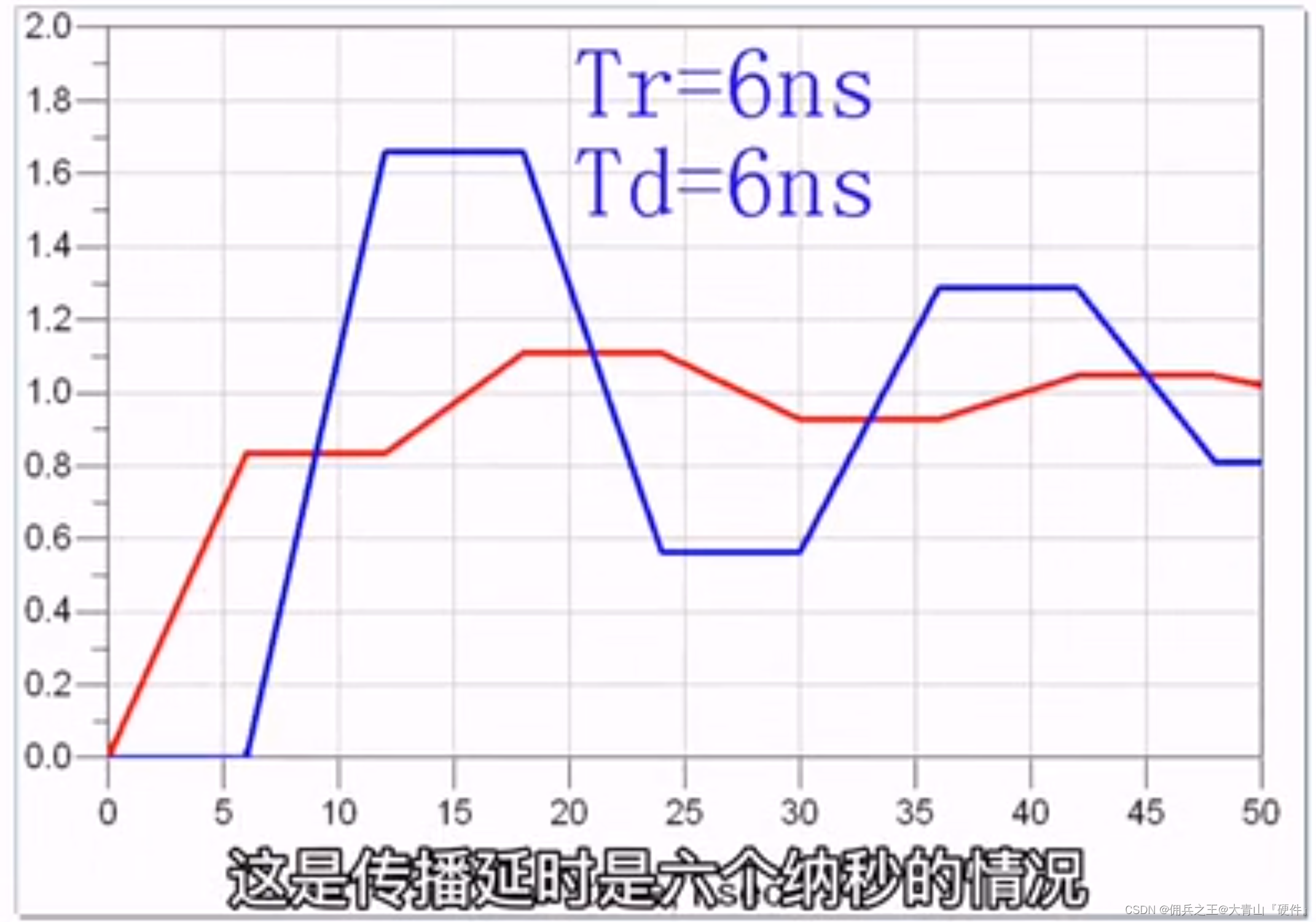

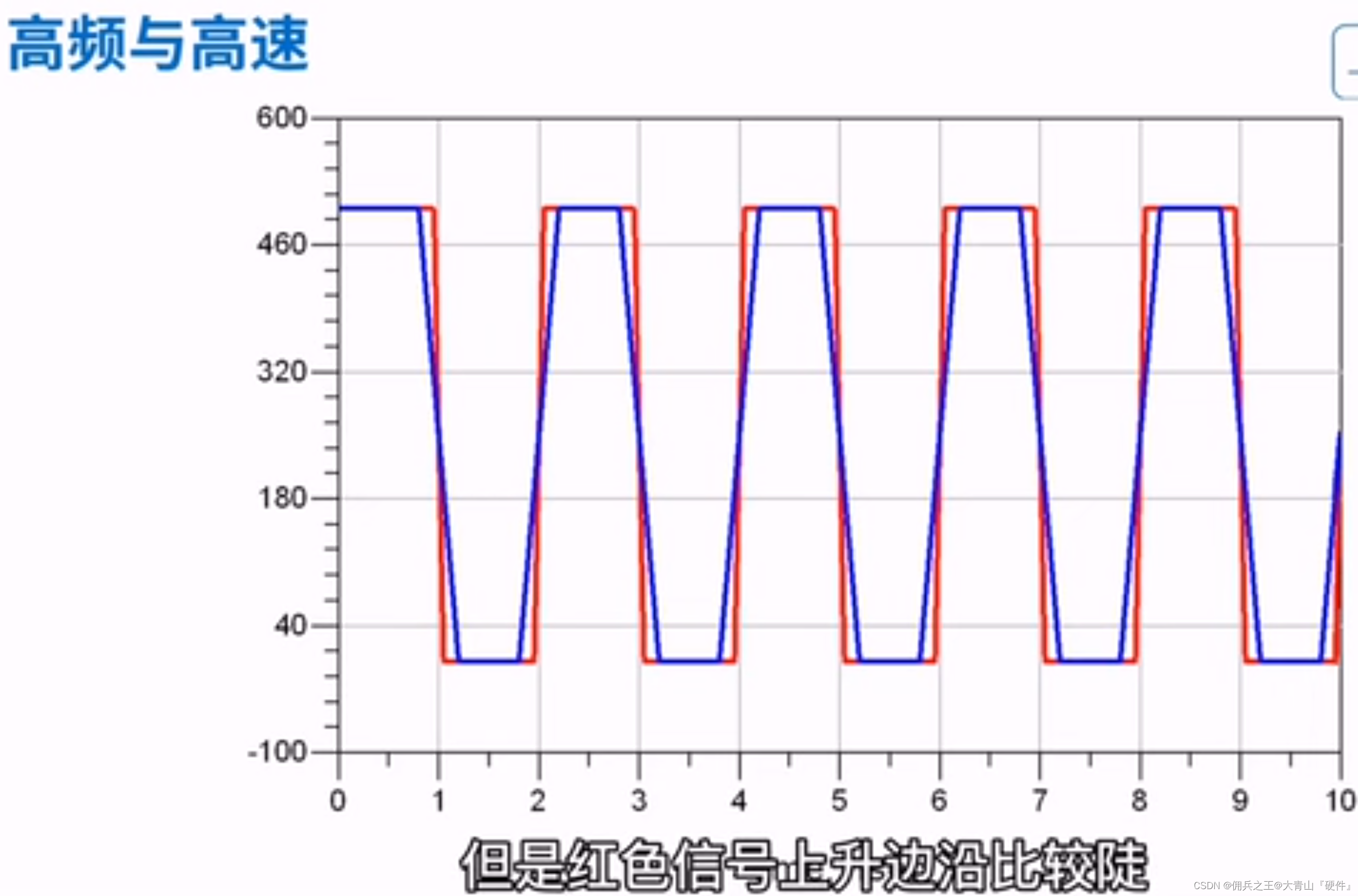

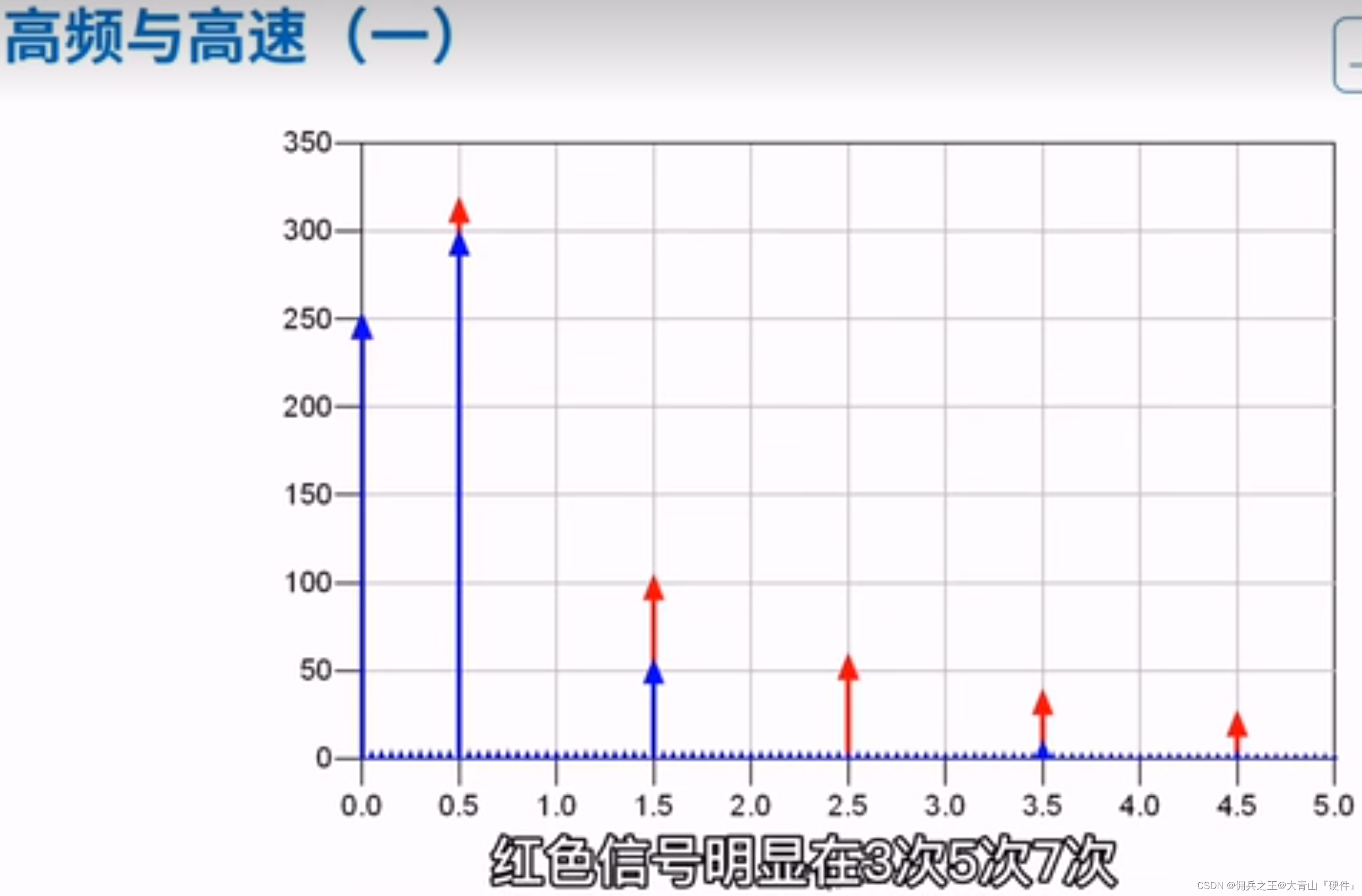

我们在做硬件设计的时候对高频信号会比较在意。高速信号的定义与上升沿时间有关,而高频信号的定义与信号的周期有关,两者是不同的。

信号完整性的研究对象是整个信号频谱中的高频分量,信号高频分量决定上升沿时间,信号有效长度是由上升沿时间决定的。信号上升沿时间越短,其电气特性的有效长度越短,如果我们的走线长于有效长度的1/6,则需要考虑用阻抗匹配来保持信号的完整性。典型的FR-4印制电路板(PCB)的内层走线信号有效长度为5.6in,而对于外层走线,由于传播延迟要小一些,有效长度更短。

在硬件设计中经常需要对频率比较高的信号进行特殊照顾,比如DDR3内存的频率经常能达到1GHz以上,PCB布线的时候通常要考虑到信号完整性的问题,做阻抗匹配和严格的拓扑结构, 但实际分析信号完整性的时候,我们的研究对象是信号的上升沿时间,在数字信号中上升沿和信号频率没有必然联系 ,所以归根结底我们对高频信号的特殊照顾,都是从其上升沿时间的角度出发的,也就是说上升沿时间短的高速信号是我们在硬件设计中需要特殊照顾的对象,而不是高频信号。

对于一个信号,其上升沿和下降沿时间占周期的4/10,通常情况下,我们考虑上升沿时间为信号周期的1/10比较合理。对于533MHz的DDR3内存信号,在没有数据手册的情况下,我们可以通过上面的经验估计方式,大致判断其上升沿时间为0.2ns,从而估算该信号走线的最大有效长度。对一个周期为1KHz的低频信号,如果它的上升沿时间很短,这个信号就是高速信号,只是说通常频率较高的信号上升沿也会较短

MIPI核,设计问题:

1)ZYNQ上加Lattice芯片扣接,加100pin,一组扣接RGB,DPHY输出一半

2)type-C替代电路

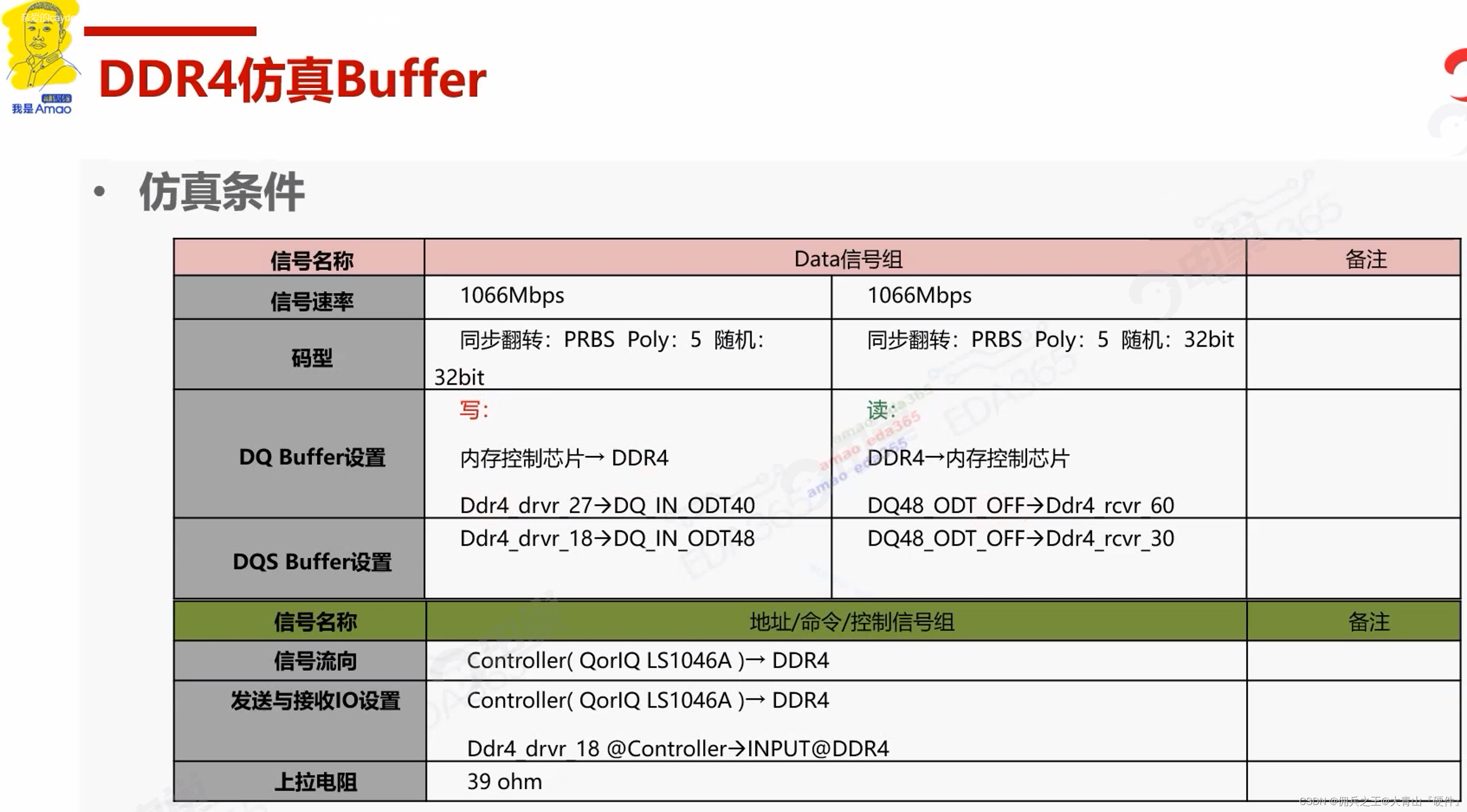

30、DDR4:

1)VTT 上拉39Ω

2)

31、PCB

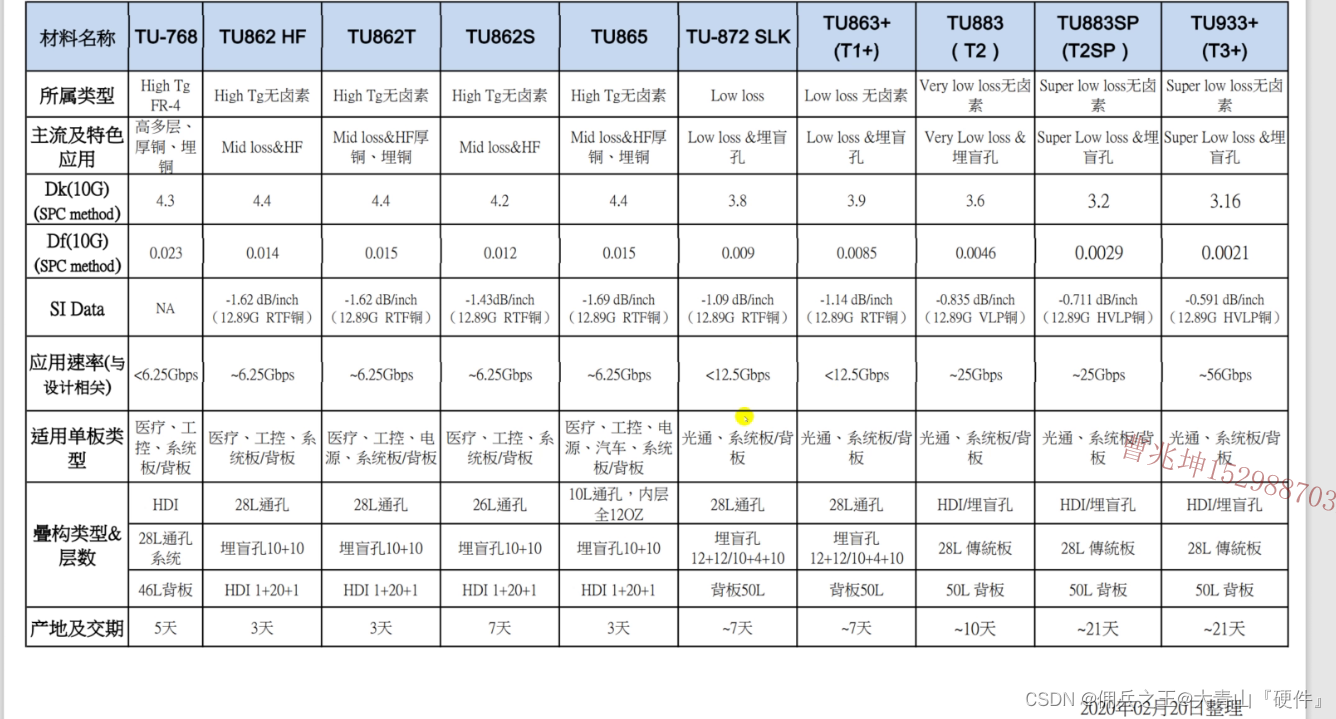

1)板材特征参数

或者PCB提交生产时仅向板厂指定使用FR-4材料,没有进一步要求是否使用高Tg板材,所以板厂给采购报了个低Tg材料的报价,报价很有价格优势,采购很开心,老板也很开心,结果PCB在加工过程中经过几次热循环之后,由于Z轴膨胀问题要换高Tg板材,老板很生气,采购自然是甩锅给Layout了。

同时,材料制造商也在不断开发新的材料,以满足市场需求,特别是对更高速度和更低损耗材料的需求,所以PCB设计工程师一定要熟悉当前的可用材料,并向PCB板材咨询最新的材料建议。同时,并非所有的PCB制造厂商都能处理所有的材料,所以准确了解所选择的PCB制造厂商能够处理哪些材料也很重要,是否是常备料,交期多久,一定要预先沟通确定。

32、

2)差分时钟控制在+-50mil以下,严格的差分走线;

控制信以及地址线要和时钟线等长,线长不超过+-100mil.

至于数据线,没有必要和时钟线,地址线以及控制线等长。每8个bit也就是一个Byte及其对应的DQS,DQM为一组。

3)以32位DDR2为例:

其实一共可以分为五个组来控制走线长度:

其实一共可以分为五个组来控制走线长度:

第一组:时钟以及控制线,地址线,所有的走线等长,误差在+-100mil,时钟要求更高,该组走线长度不宜短于数据线长度。

第二组:Byte0(D0-D7)以DQS0,DQM0为一组,要求等长,误差在+-100mil,可适当放宽

第三组:Byte1 (D8-D15)以DQS1,DQM1为一组,要求等长,误差在+-100mil,可适当放宽

第四组:Byte2(D16-D23)以DQS2,DQM2为一组,要求等长,误差在+-100mil,可适当放宽

第五组:Byte3(D24-D32)以DQS3,DQM3为一组,要求等长,误差在+-100mil,可适当放宽

2)温度升高,会降低运行频率

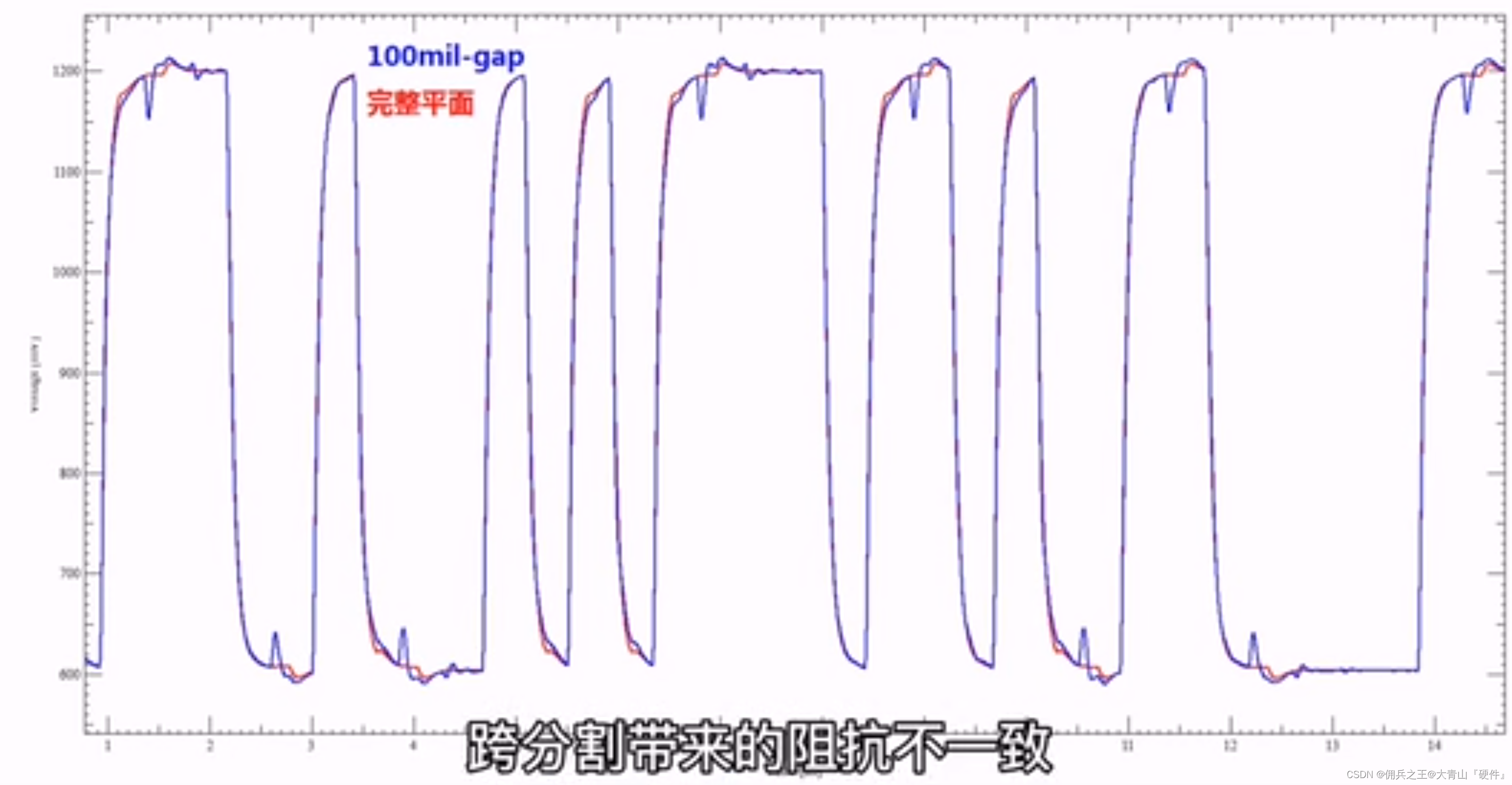

9)信号的上升沿

蓝色波形,高次谐波幅度低

过孔规划方式

如上,大家对高速的理解,千奇百怪

35、汤涛--SPI-50MHz的电路

36、验证产品的功能、性能和可靠性、安规、EMC,及实现内部技术标准的要求;

负责规格书编写、测试方案制定及进行可靠性和功能验证测试,制作测试治具,与测试部门协作完成验证与确认过程

37、故障:

38、运放

39、工作:

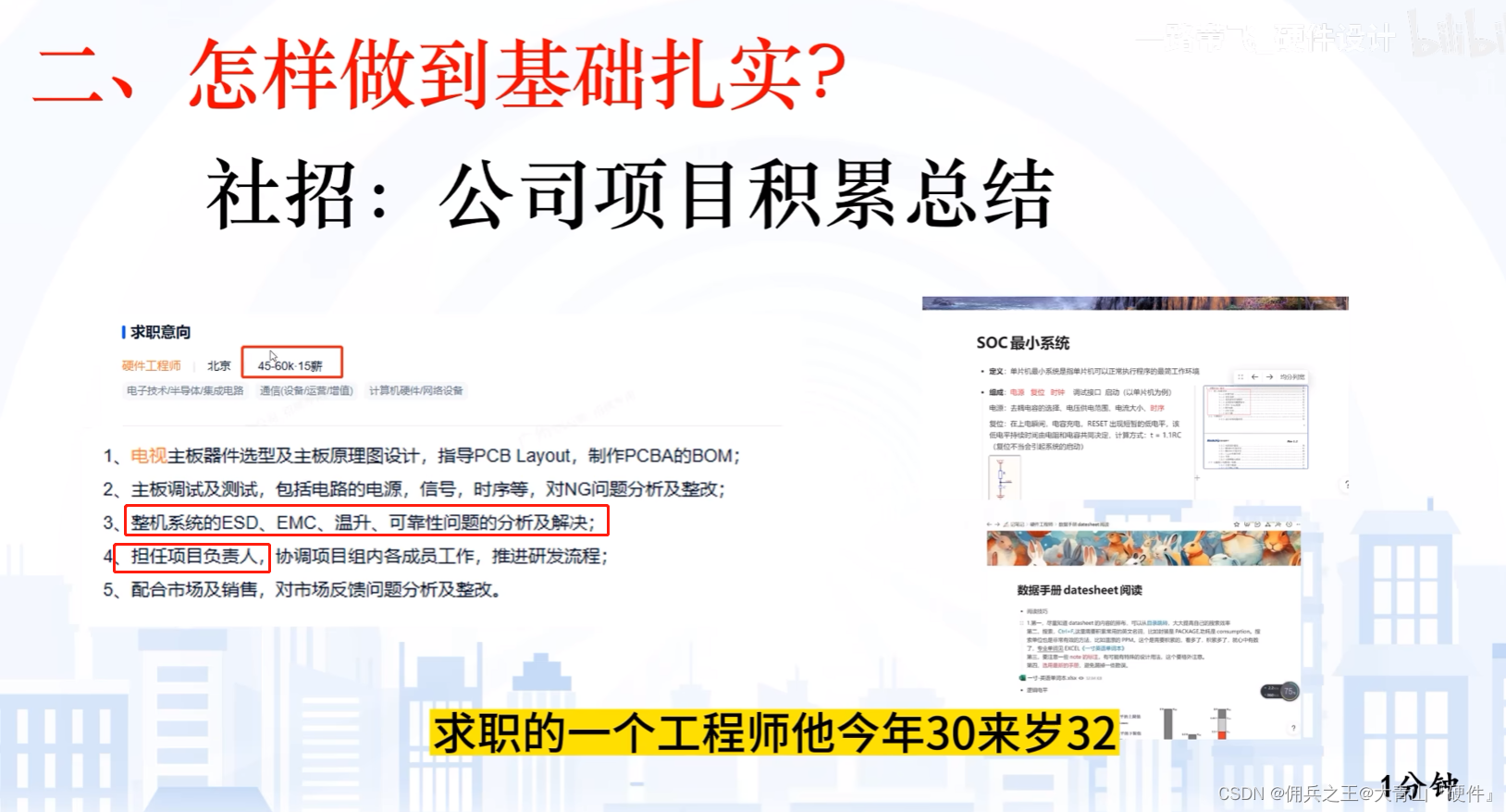

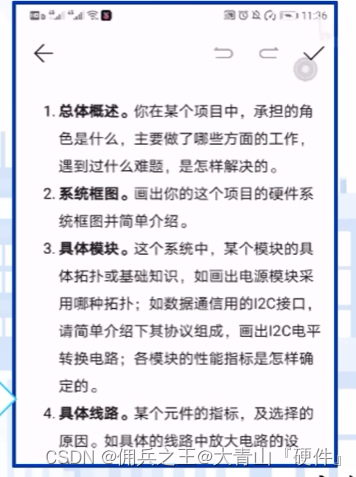

1)比能力更重要的,是底层逻辑

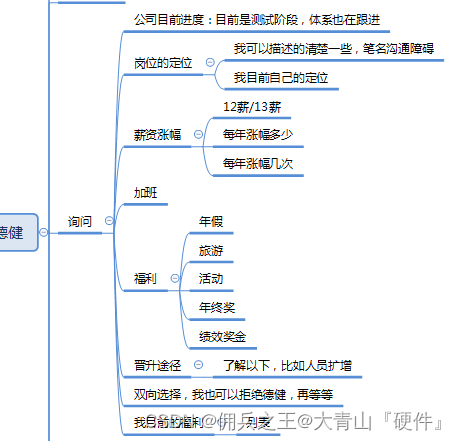

2)面试

40、BJT/MOS搭建双向切换开关

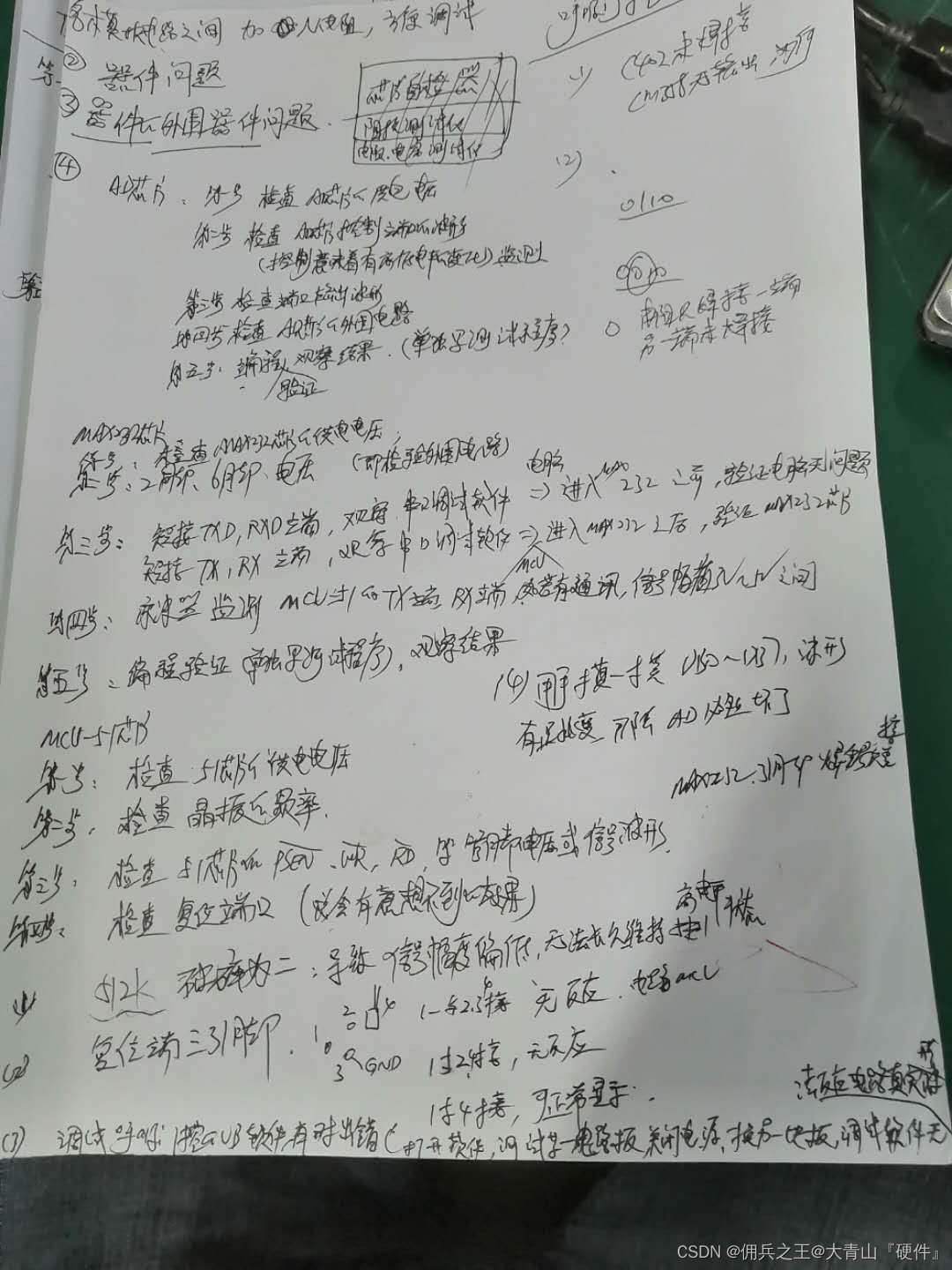

如何DEBUG

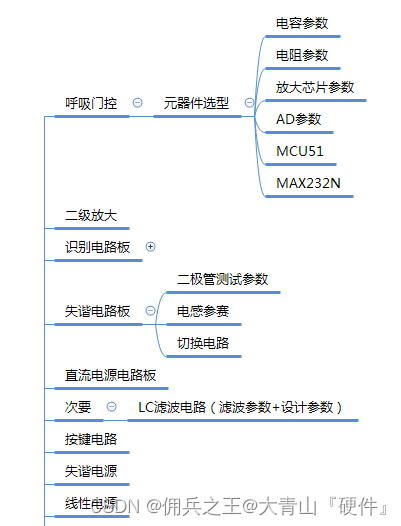

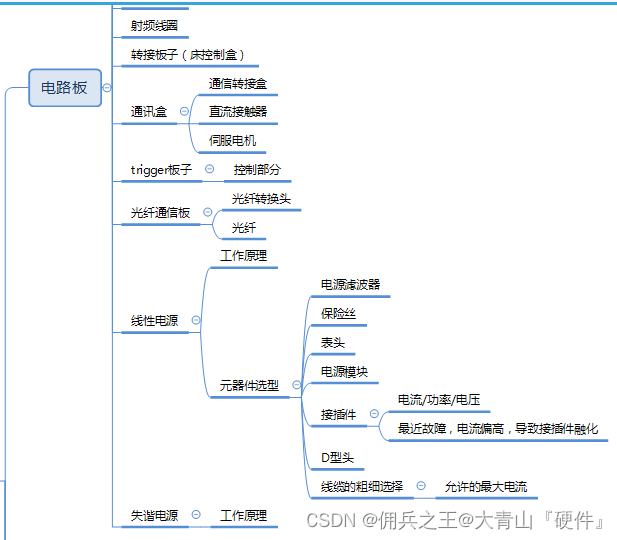

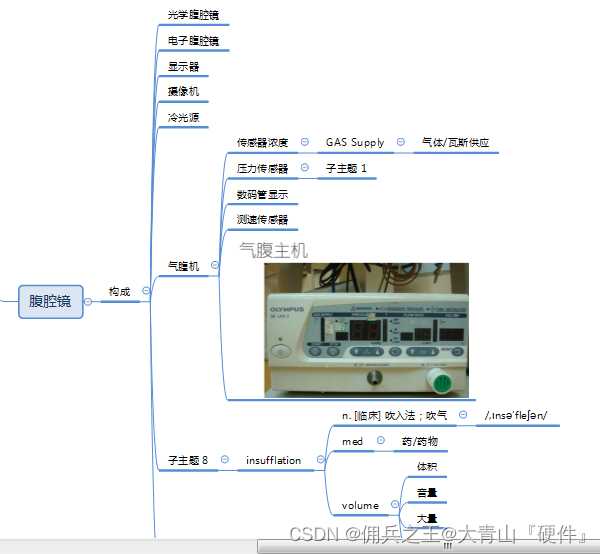

41、思维导图

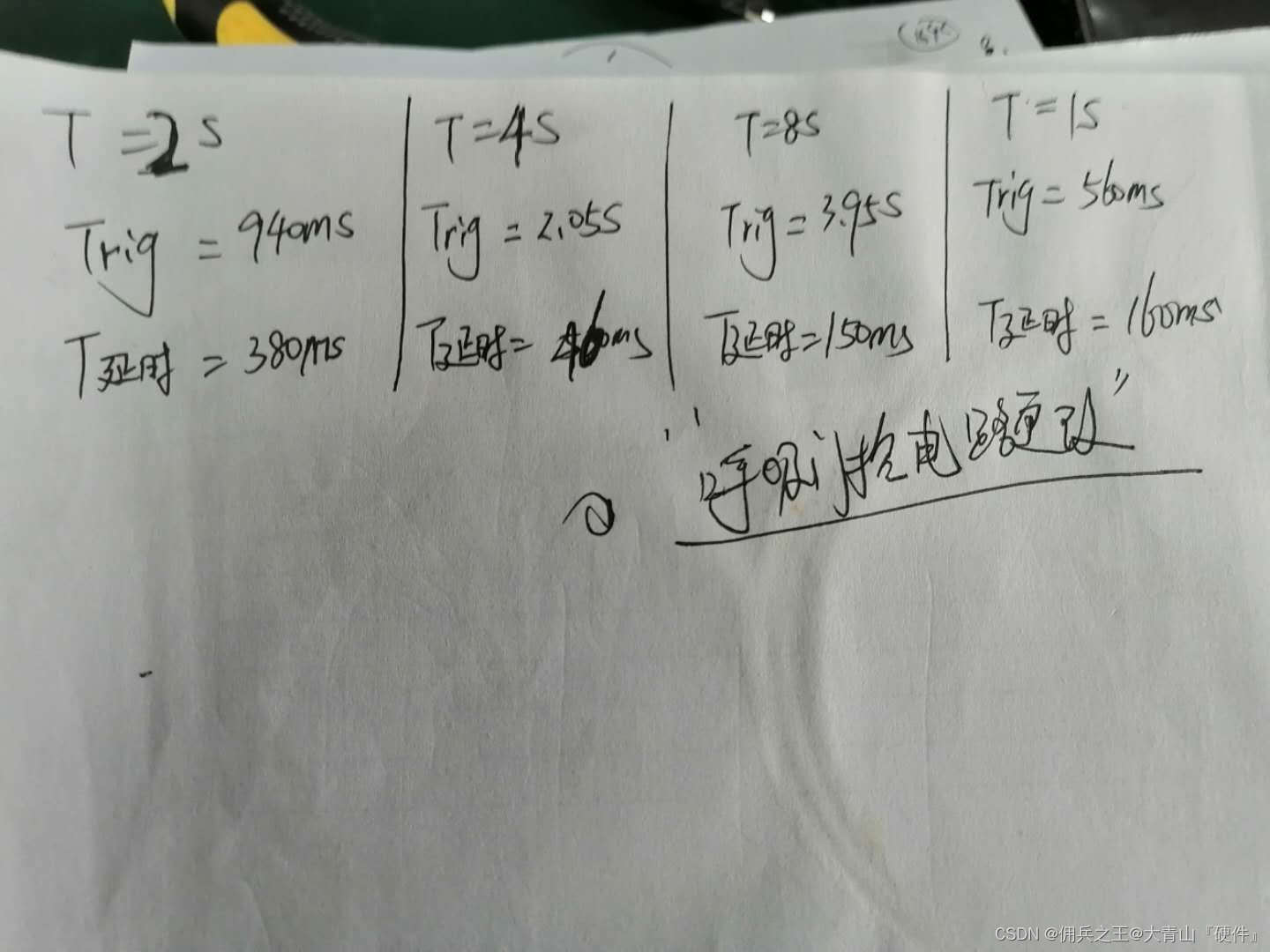

42、调试

43、饮食

饭前喝汤身体健康,饭后吃饭身体发胖

不知道-->了解-->知道-->懂/理解-->侃侃而谈

做到极致的感受

44、功能设计

1)

2)各功能程序实现模块化、系统化。这样,既便于调试、连接,又便于移植、修改和一个优秀的应用系统的软件应具有以下特点:1)软件结构清晰、简捷、流程合理。

3)程序存储区、数据存储区规划合理,既能节约存储容量,又能给程序设计与操作带维护。

4)运行状态实现标志化管理。各个功能程序运行状态、运行结果以及运行需求都设置来方便。状态标志以便查询,程序的转移、运行、控制都可通过状态标志来控制。

5)经过调试修改后的程序应进行规范化,除去修改“痕迹”。规范化的程序便于交流

借鉴,也为今后的软件模块化、标准化打下基础。

6)实现全面软件抗干扰设计。软件抗于扰是计算机应用系统提高可靠性的有力措施。

7)为了提高运行的可靠性,在应用软件中设置自诊断程序,在系统运行前先运行自诊断程序,用以检查系统各特征参数是否正常。

研发助理+工程人员(硬件设计+Layout+FPGA+软件+机构+工程+)

PCB工程文件=Layout文件和pdf+Gerber文件+装配文件pdf+坐标文件asc+BOM

硬件工程文件=原理图文件和pdf+硬件电路描述+changlist文档+cable线缆参数文档(电流/长度/接头/线序/材质/双绞/同轴。。。)

项目名称+文件+文件说明 加密后发给 研发助理,由研发助理负责文件格式和文件数量检查,并上传到ERP和存储SVN盘,研发人员被开通权限后可以下载,流程由研发助理跟踪,过多人找其他部门,事情比较乱,单一关系的处理,成批量处理,提高效率;

ERP功能:协调不同部门,共享信息

DSN+PCB====制版==采购发包

45、采购和研发助理,BOM发送和建立料号

46、售后/生产列出常见故障条目,生产测试和研发软硬件共同给出给答案

故障解决方案库(70%-80%出现的是常见问题/重复问题,特别的问题/不常见的问题,硬件人员和软件人员解决,减小研发人员因简单问题频繁受干扰)

47、原理图升版

PCB没有提交给供应商加工,每次的原理图变更一般不升版本,更改文件日期即可

原理图的升版一般是在旧的板子上做过原理图的变更才会升版,比如新的板子做出来,经过测试、调试后要增删电路,那么就要开始升一个版本,然后提交给Layout工程师做新的板子,Layout工程师在画板过程中,电路工程师发现电路还得修改,那么新修改的原理图不需要升版,只需更换出图日期即可(一般文件命名规则是:项目名称+版本号+出图日期)。

对应的BOM和外接线缆也要升级,即使元器件没有改变

元器件升级,器件改变,但是封装没变,BOM版本保留再添加,文档说明

仅仅丝印变更,

PCB版本升级

PCB的版本一般是有一次实物板子,就会有一个版本,如上次出来的板子是1版本,第二次做出来的板子就是2版

封装改变/位置改变(热量大调整位置)/文件丝印改变/器件改变(10K不够改改为49K)

开放权限才可下载,参与过项目,可以一直看;更换部门/离职,取消权限

存放在公共SVN盘里

看规格书要求:

1.看元件类型是贴片(SMD)还是插件(DIP)2.看标注尺寸单位(1inches(英寸)=1000mil密耳=25.4mm)

3.看管脚个数及大小

4.看管脚间的间距

5.看实体大小。

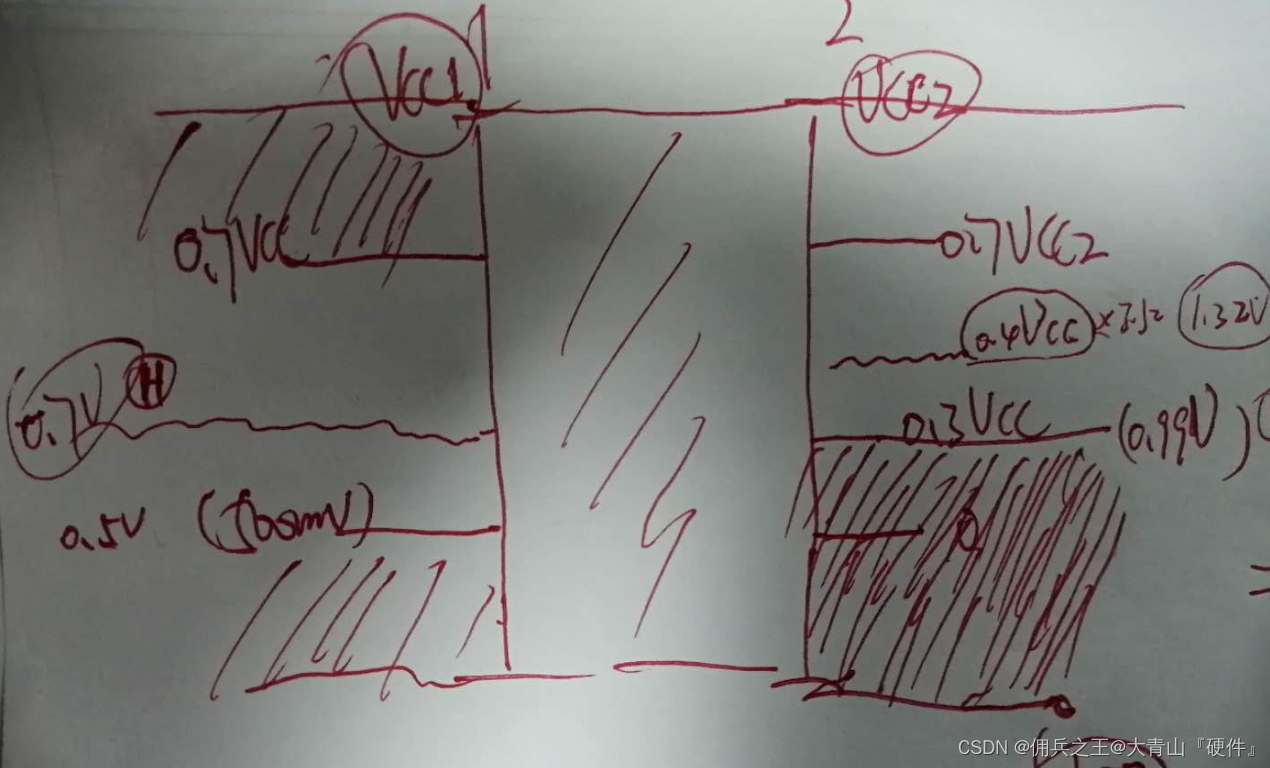

49、电平标准:

元器件失效:

50、示波器:

我用示波器观察高频时钟信号时也遇到过这种现象,我的愚见是因为振铃效应。有回答说波形质量差,我认为未必,示波器本身也是一个测量装置,测量到的波形与实际波形并不一致。方波本身包含着从基频到无穷次的奇次谐波,示波器采样频率有限,测量会损失高次谐波分量,导致最后描述的信号与实际产生偏差。此外,一般的示波器探头接入电路相当于一个滤波器,在测量方波时也会造成误差。

51、电平技巧:

过冲/下冲,,,阻抗不匹配,

粗线:过零点失真

速率高,抖动难以控制,抖动大,图像线条够粗(垂直方向)

占空比,三角形够大。

Q大,线条细、

噪声大,电平范围比较厚(水平方向)

交叉点下调,比较好

眼睛的张开度 和 误码率数值大小的区别,BER浴缸图,,数值越大越好,10的-12次方

Swing抬高,抬高眼高

高低电平的幅度

高电平时的噪声大小,涉及厚度。

时钟抖动,ppm就起作用,个人猜测。

眼高,信噪比测量

眼宽,反映总抖动

三角区域要够干净

物理层测试,硬件处理

协议层测试,软件处理

友达的2.7版FPGA程序,不支持逻辑图,是特殊程序。

线太长,信号变差,,

1米以上线缆,常温ok,高温NG

项目/专案的把控

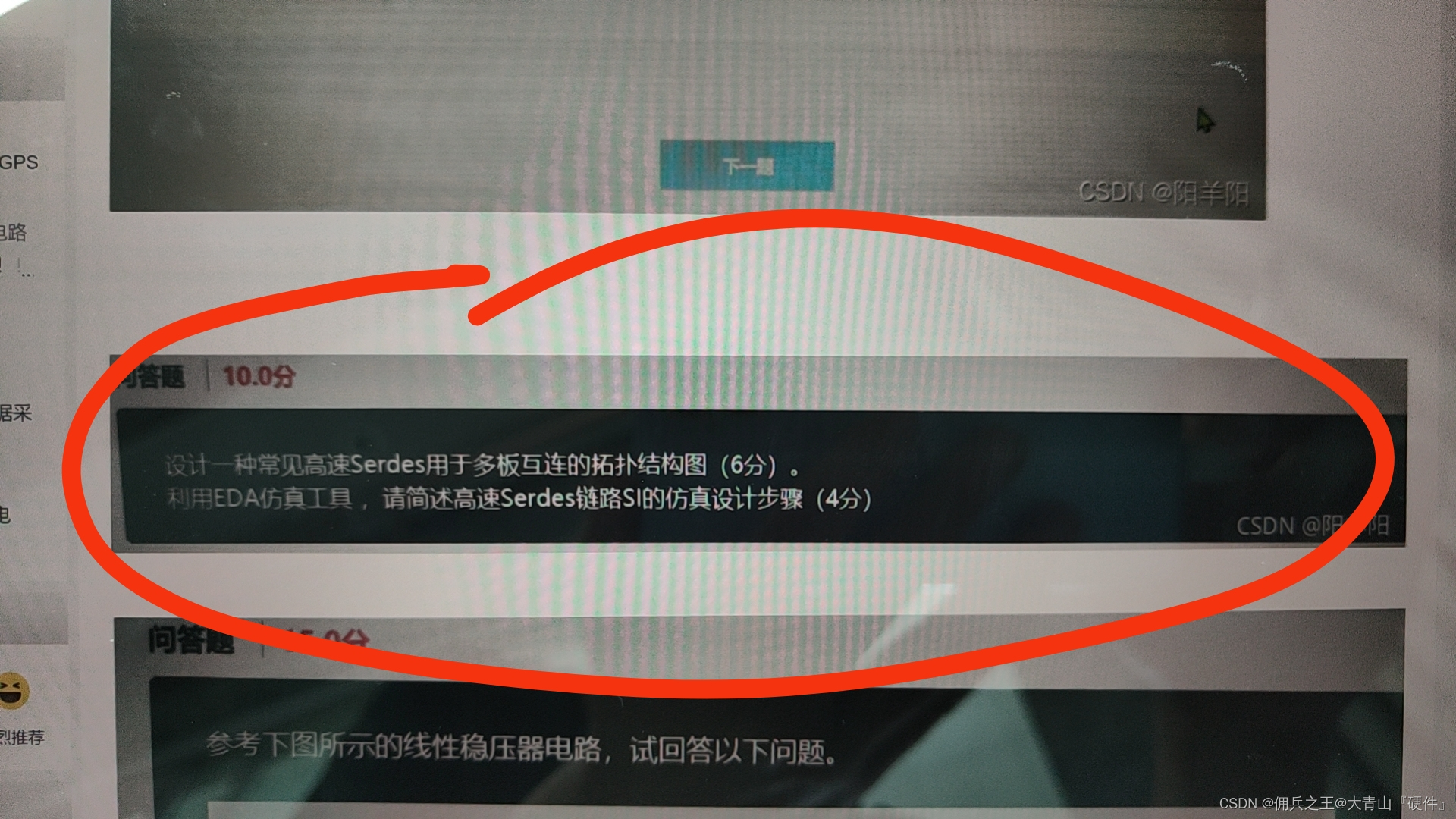

serdes串化器/解串器电路,FPGA内部电路

过压过流保护

电压/电流侦测

短路保护

SG2142+NT805-A+;;确定是否SG2142?

SG622的网口电路,PHY芯片输出两个时钟,发送时钟给FPGA的RX端口;发送时钟给FPGA的IP核作为参考时钟,

母料号升级,2001文件/2005文件,变更为205和318文件

4.6,发烫,复现不了,电源找问题

15.6灭屏,查找RST和电源波形,

5.46屏幕的PWM可调屏幕,软件已经做完。

SG624,信号课,8K一体机,提前规划,熟悉电路,安排工作。

减小纹波的方法:

环路补偿,

增大输入端和输出端的容值(选择低ESR的输出电容)

增大电感值

减小输入电压

15天=改版本需要9天(部分芯片替代料验证+buck电路新设计+方案评估+绘图+相关上传文件时间+评审)+调试时间不确定,要是顺利,2天搞定(环境拼搭+测试点屏+老化试验)+异常情况调试4天。

52、电源芯片

MP1482DS-LF-Z

RAA210130

[方案]15.6高温灭屏的后续方案

专项进度报备-eDP

公司的EDP TX模块移植到Altera开发板。

会议结论:曹兆坤把测试报告提交采购,邀请厂商(骏龙专家)线上培训、评判测试报告,通知段总、远来和张超一起参加,骏龙南京的专家微信推送段总。----------秦杨(尽量安排在下周)

53、规划 小朋友的学习步骤和成长规划

54、BUCK:

部

部

电机: