热门标签

热门文章

- 1Qt5配置opencv4.5.4_qt5 opencv4.5 指纹比对

- 2引领代码美感革命:Iconify - VS Code 必备图标插件

- 3redis数据迁移的方法_redis 数据迁移到 ctgcache

- 4哈夫曼树(Huffman tree)及哈夫曼编码_已知哈夫曼树怎么求哈夫曼编码

- 5windows Terminal修改配置文件_terminal修改文件

- 6服务器数据恢复—虚拟机配置文件丢失,虚拟磁盘文件被误删除的数据恢复案例

- 7脱离服务器|电脑,备用机安卓机也能玩转青龙面板。_手机怎么搭建青龙面板

- 8Hadoop HDFS 常用Shell命令 | 图文详解_movefromlocal命令举例

- 9学业辅导导师:文心一言智能体详细介绍和开发_文心一言的智能体怎样才能成长

- 10现场直击 | 飞凌嵌入式亮相2024上海国际嵌入式展

当前位置: article > 正文

数电基础知识学习笔记_数电笔记

作者:从前慢现在也慢 | 2024-07-06 15:44:46

赞

踩

数电笔记

文章目录:

用74LS160反馈法构成6进制计数器 ( 反馈置0法、直接清零法)

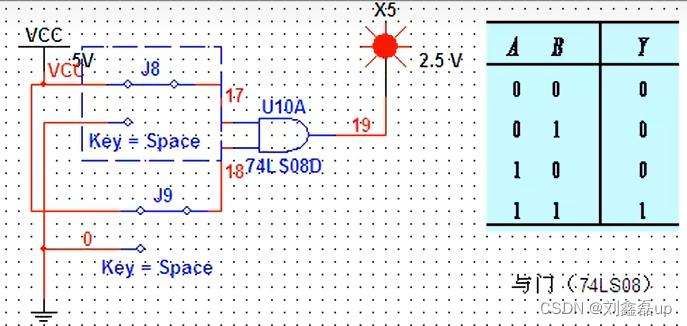

一:逻辑门

1.逻辑门电路的分类

1.1 按逻辑(逻辑门)

1.1.1 逻辑定义

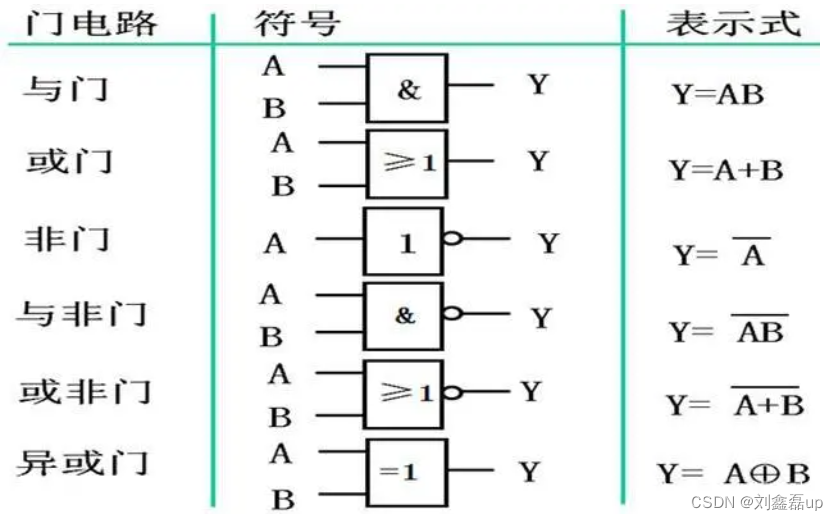

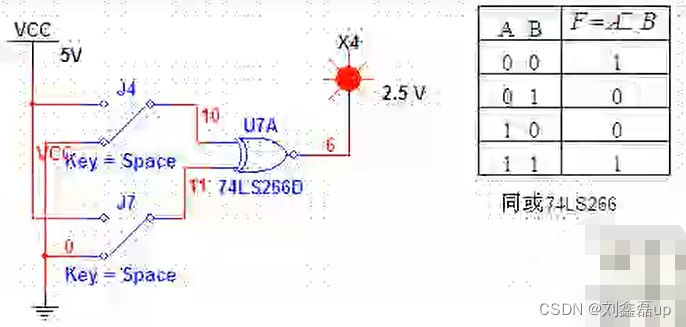

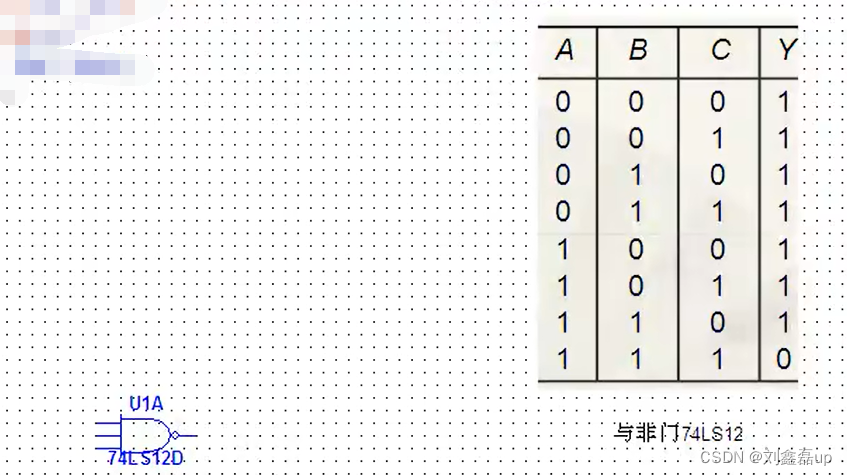

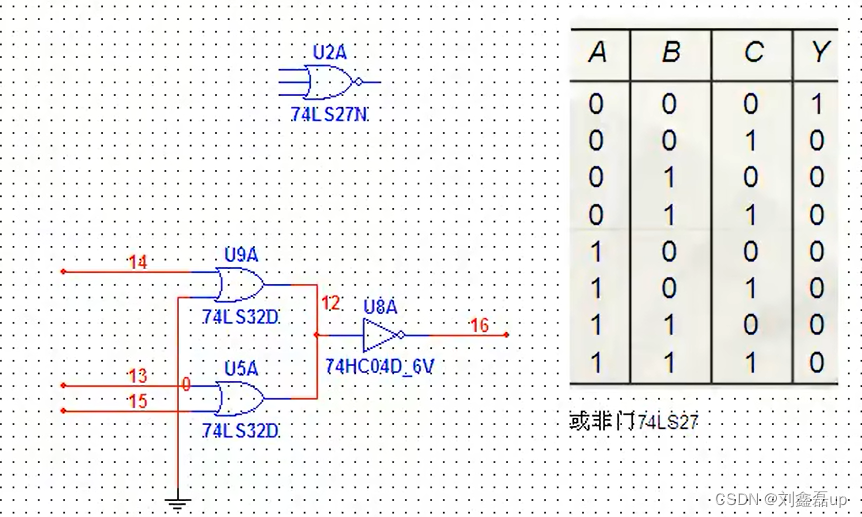

1.1.2 常见数字电路相关符号

1.1.3 电路图表示

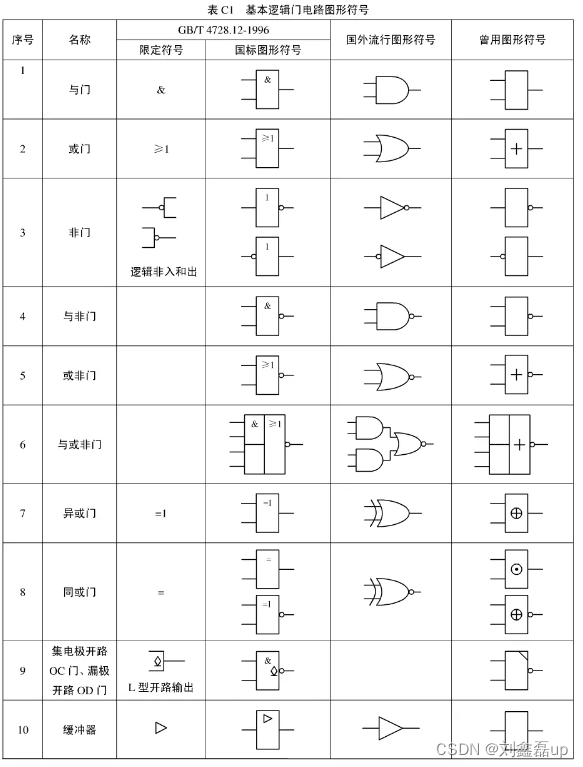

1.1.4 逻辑门电路图像符号

1.2 按电路结构

- TTL集成门电路:输入端和输出端都用三极管的逻辑门电路

- 对于一般情况下,TTL门比COMS门电平翻转快一些

-

-

-

- CMOS集成门电路:用互补对称MOS管构成的逻辑门电路

- 功耗极低、抗干扰能力强、电源电压范围宽、输出信号摆幅大、扇出系数大(带负载能力强)

1.3 按功能特点

2.高低电平的含义

- 高电平和低电平为某规定范围的电位值,而非一固定值

-

-

- 正逻辑:看1(0011=3)

- 一般高电平为3.5~5V,低电平为0~0.3V

- 负逻辑:看0(0011=12)

- 一般高电平为0~0.3V,低电平为3.5~5V

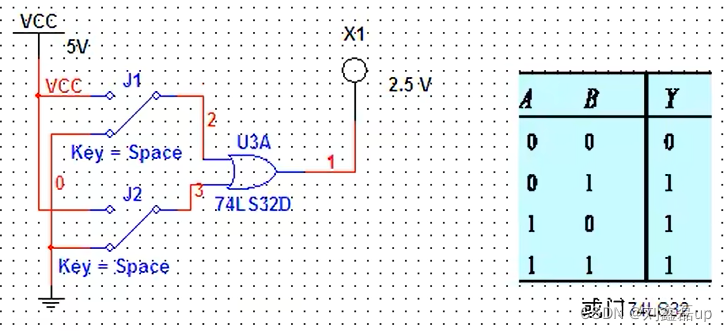

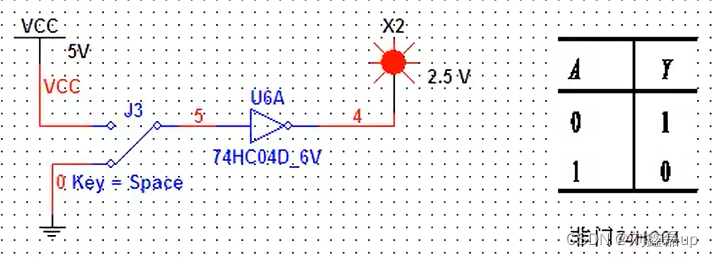

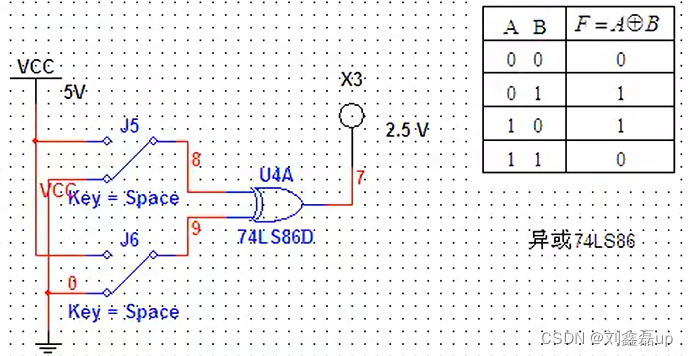

3.常见的门

3.1 逻辑门

3.2 OC门

3.3 OD门

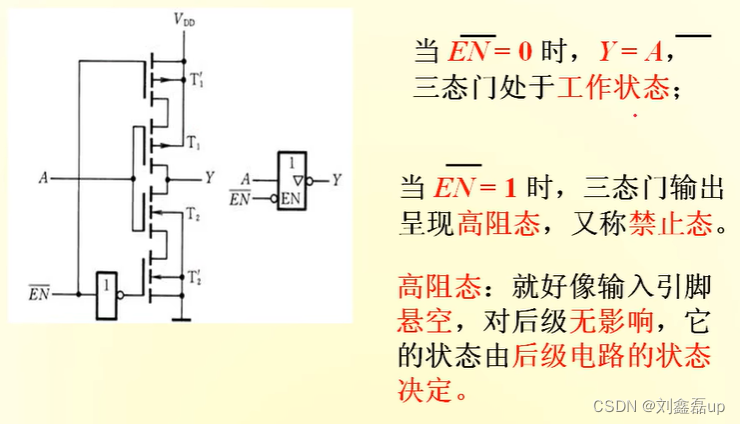

3.4 三态输出门

介绍:具有三种状态的门电路,分别为高电平,低电平高阻态

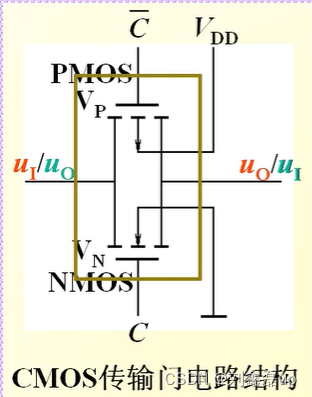

3.5 CMOS传输门

4.闲置输出端的处理

- 与门和与非门:多余输入端接正电源,或与有用输入端并接

- 或门和或非门:多余输入端接地,或与有用输入端并接

-

-

- TTL电路:输入端悬空时相当于输入高电平

- CMOS电路:多余输入端不允许悬空

5.集成逻辑门电路的选用

- 1、工作频率要求(高低电平翻转所需时间)

-

- 2、输入电源电压要求

-

- 3、功耗问题

-

- 4、电平翻转对输入电压的要求

-

- 5、注意灌申流和村申流

二:组合逻辑门电路

- 定义:它就是有一些逻辑门电路搭建,为实现某种功能而组合的电路

-

- 特点:在任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关

-

-

-

-

- 根据图分析组合逻辑的方法:

- 第一步:组合逻辑电路图(在右边 逻辑转换器XLCI)

- 第二步:逻辑表达式

- 第三步:最简表达式

- 第四步:真值表

- 第五步:确切电路功能

-

- 根据题目要求设计逻辑电路:

- 第一步:问题的提出

- 第二步:真值表

- 第三步:逻辑表达式

- 第四步:最简表达式

- 第五步:逻辑电路(点击自动生成,之后添加上相应组件就是)

三:编码器、译码器

1.编码器

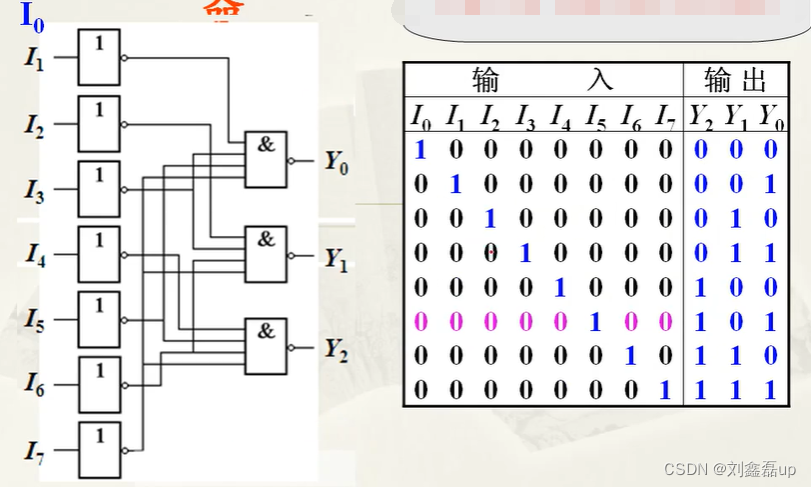

1.1 二进制编码器

用n位二进制数码对2^n个输入信号进行编码的电路

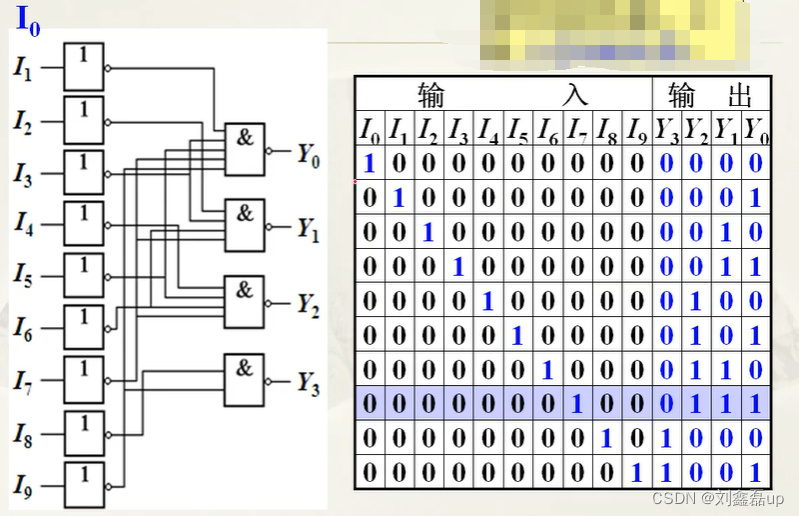

1.2 二~十进制编码器 CT74LS147

将0~9十个十进制数转换为二进制代码的电路。又称十进制编码器

1.3 优先编码器 74LS148

允许同时输入数个编码信号,并只对其中优先权最高的信号进行编码输出的电路

2.译码器(编码的逆过程)

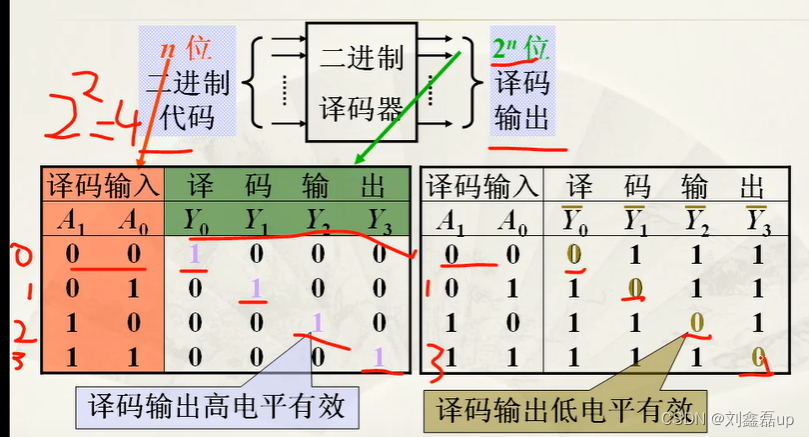

2.1 二进制编码器

定义:将输入二进制代码译成相应输出信号的电路

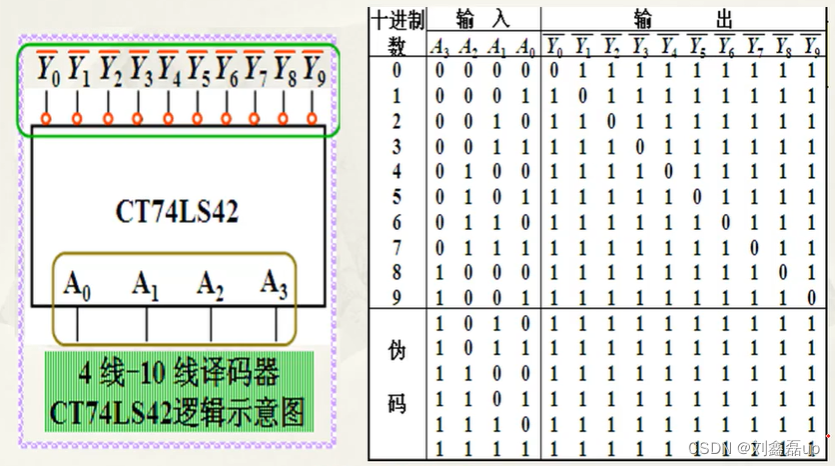

2.2 二~十进制编码器 CT74LS148

将BCD码的十组代码译成0~9十个对应输出信号的电路,又称4线-10线译码器

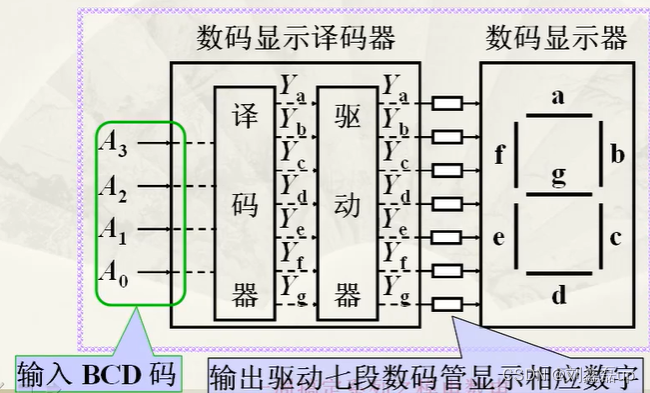

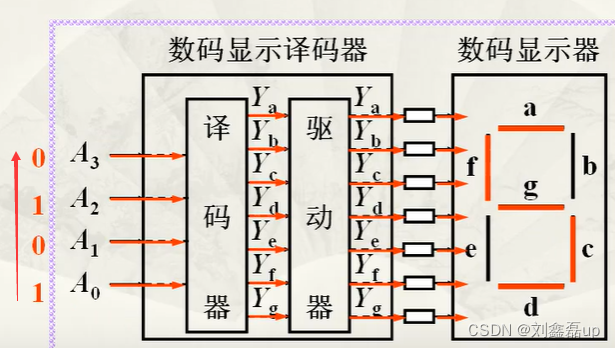

2.3 数码显示译码器

四:触发器(基本元件 存储数据)

- 数字电路

- 组合逻辑电路:基本单元是门电路

- 时序逻辑电路:基本单元是触发器

- 触发器与门电路的区别

- 门电路:某一时刻的输出信号完全取决于该时刻的输入信号,无记忆功能

- 触发器:具有记忆功能,能够在无信号的情况下,保持上一次的信号

-

-

- 触发器的现态和次态

- 现态O^n———触发器接收输入信号之前的状态

- 次态O^(n+l)———触发器接收输入信号之后的状态

-

-

- 触发器的分类

- 从电路结构不同分

- 基本触发器:输入信号直接加到输入端,是触发器的基本电路结构,是构成其他类型触发器的基础

- 同步触发器:输入信号经过控制门输入,控制门受时钟信号CP控制

- 边沿触发器:只在时钟信号CP的上升沿或下降沿时刻,输入信号才能被接收

- 从逻辑功能不同分

- RS触发器

- JK触发器

- D触发器

- T触发器

- T'触发器

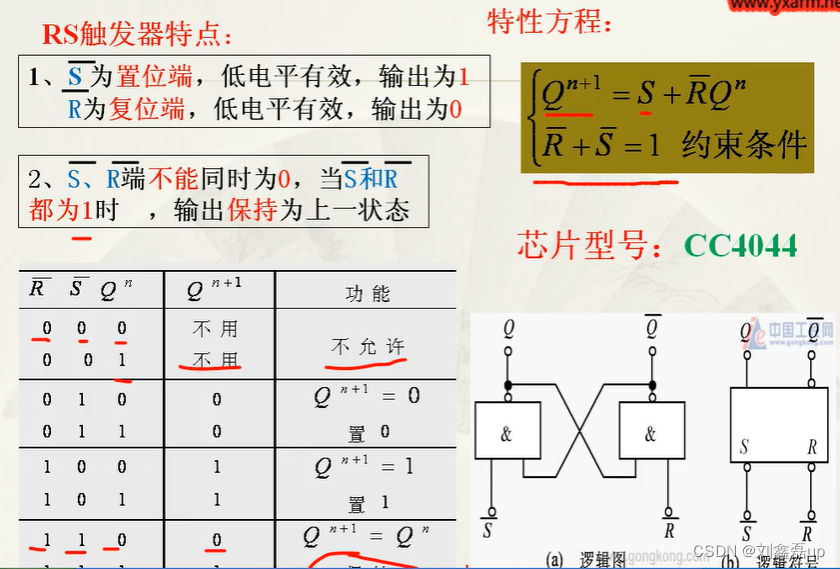

1.基本RS触发器

2.时钟控制R-S触发器

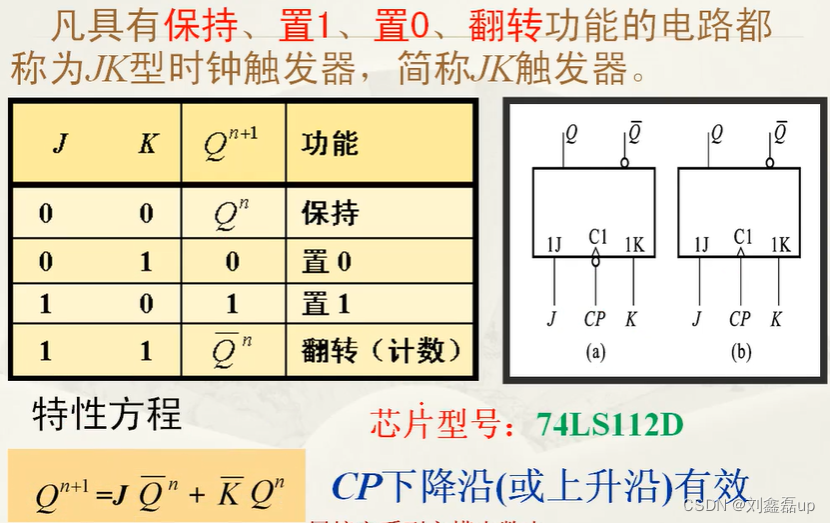

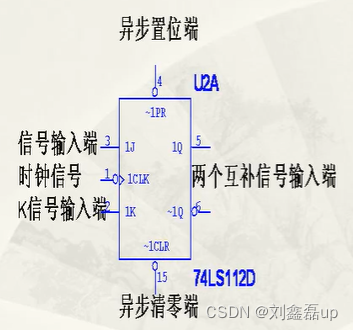

3.JK触发器

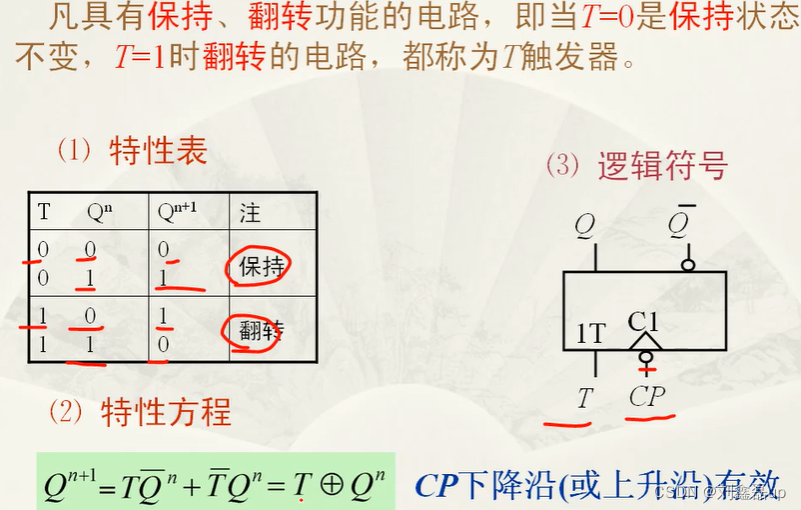

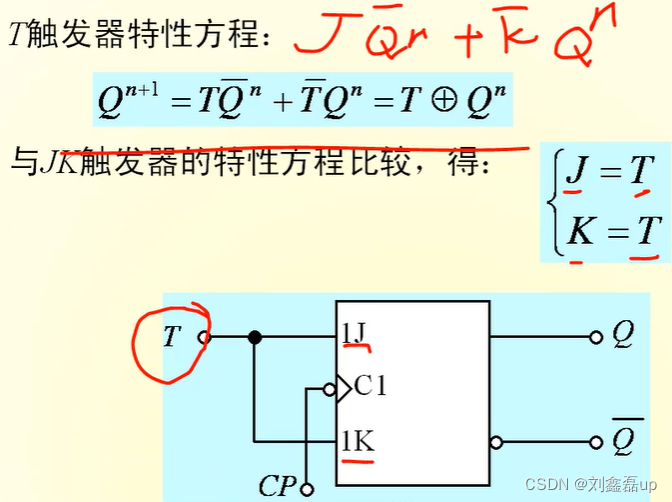

4.T型触发器

JK触发器转T型触发器

对比公式进行替换

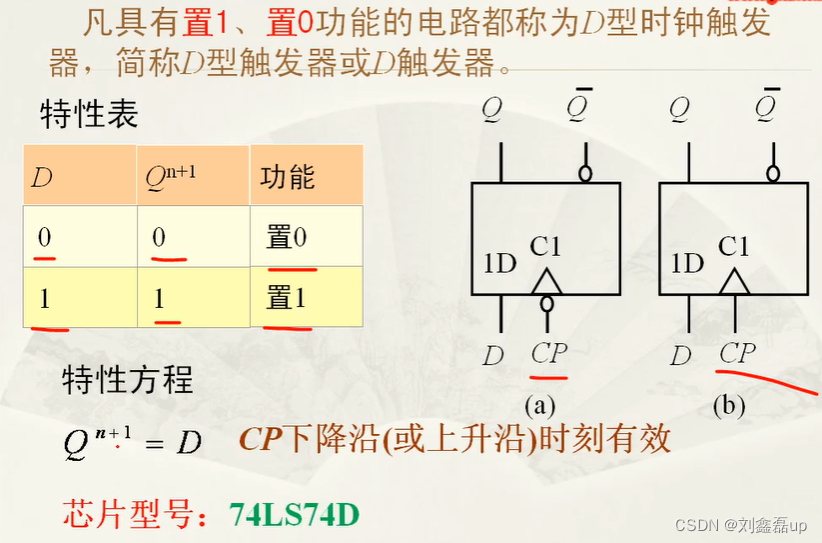

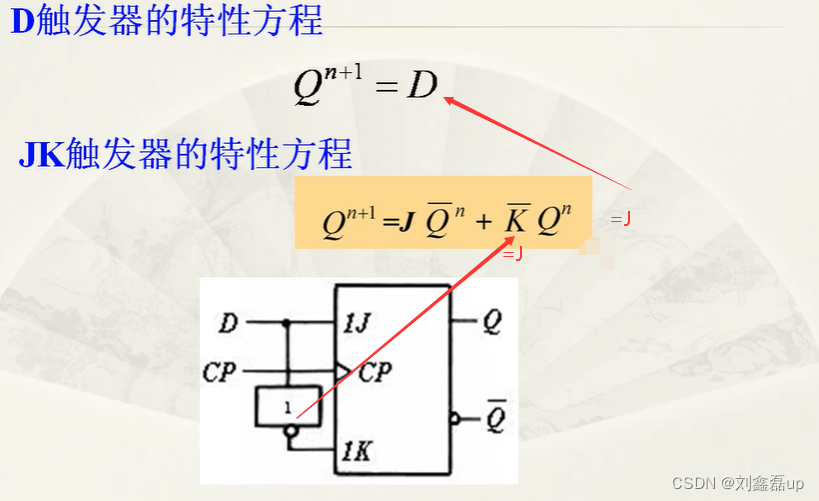

5.D型触发器

JK触发器转D型触发器

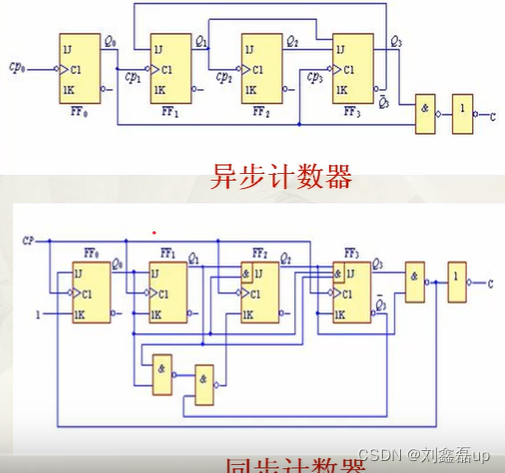

五:计数器(高级元件 统计脉冲信号)

- 定义:用以统计输入计数脉冲(CP)个数的电路

-

-

- 原理:计数器内部由触发器构成,触发器具有记忆功能,1个触发器单元能存储1位二进制数

-

-

- 应用:计数、定时和分频

-

-

- 分类

- CP脉冲引入的方式:同步、异步计数器

- 计数值的增减趋势:加法、减法、循环计数器

- 计数容量:二进制、十进制、任意进制计数器

1.同步计数器和异步计数器的区别

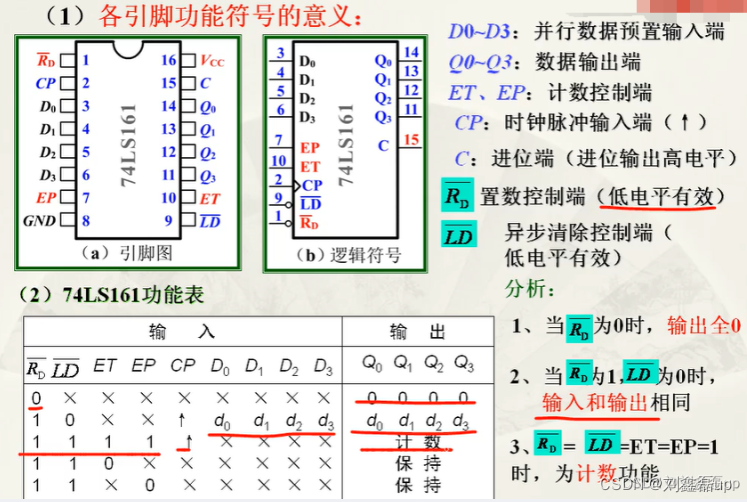

2.同步二进制计数器(74LS161)

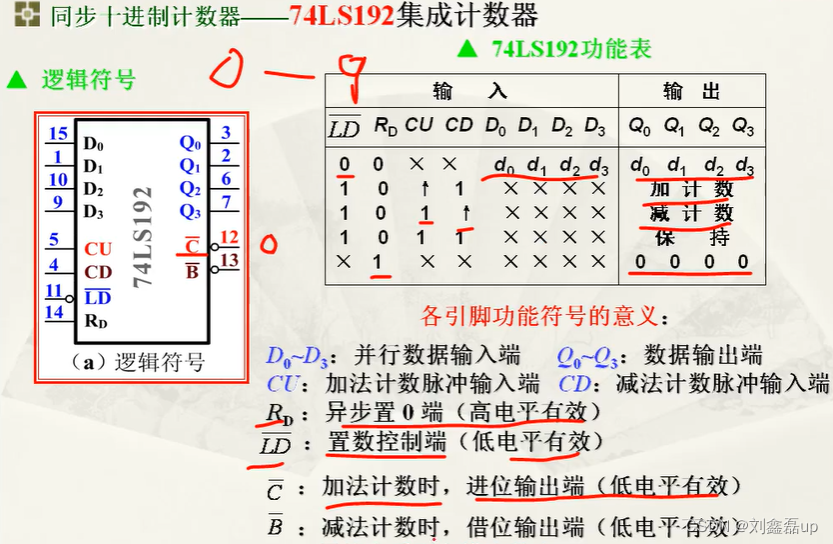

3.十进制计数器(74LS192)

逻辑分析仪XLAI

利用74LS192实现100进制计数器

利用两个相连:通关进位,实现0~99计数

4.任意进制计数器

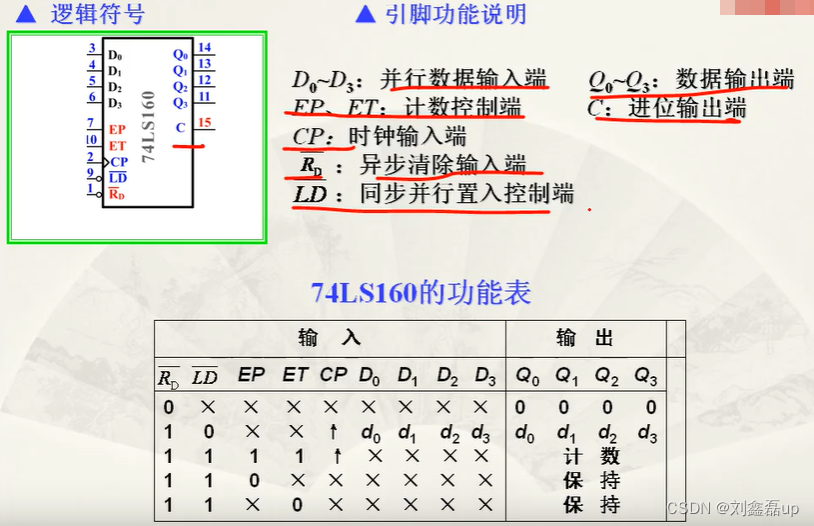

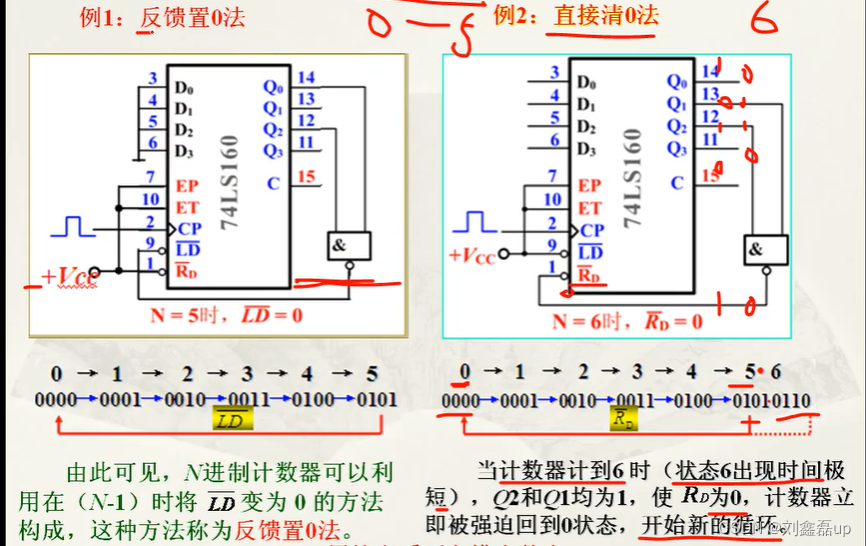

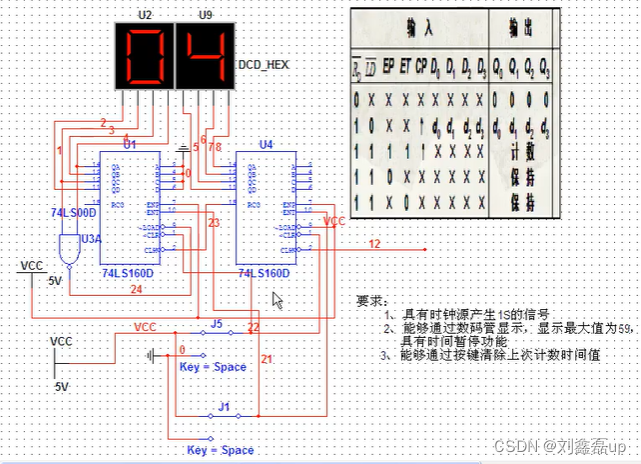

用74LS160反馈法构成6进制计数器 ( 反馈置0法、直接清零法)

六:数电电路设计

1.简易秒表设计

2.简易密码锁

- 要求

- 1、设定三位密码锁

- 2、能够通过数码管显示当前所输入的密码

- 3、密码正确时,用LED灯点亮指示

3.简易测频仪

要求:用数字电路搭建一个简易测频仪,能够测出范围为10HZ~9KHZ的频率

4.抢答器设计

- 要求:

- 1、抢答器同时提供6名选手或6个代表队赛,分别用6个按钮S1~S6表示

- 2、设置一个系统清除开关,该开关由主持人控制

- 3、抢答器具有锁存与显示功能。即选手按动按钮,锁存相应的编号,并在LED数码管上显示

- 选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/793314

推荐阅读

相关标签