- 1史上最快的推理终端来啦!Groq API 新手入门指南

- 2软件测试面试题之自动化测试题合集(金九银十必备)_自动化测试笔试题

- 3Mybatis (plus 也适用)原生直接执行某句SQL_mybatis plus 直接执行sql

- 4重磅!2024智源大会完整日程公布——全球大模型先锋集结

- 5实验07 因子分析_因子分析实验

- 6鸿蒙一次开发,多端部署(七)响应式布局_鸿蒙breakpointsystem

- 7chatgpt赋能python:Python编译成C代码的完整指南_将python代码转换成c代码

- 8PHP设计网站登录功能_php用户名密码登录界面

- 9【Asp.Net Core】C#解析Markdown文档_c# markdown

- 10大数据 深度学习毕业论文(毕设)课题汇总_深度学习的毕设论文怎么写

深入浅出dpdk读书笔记--pcie与包处理(二)----dma_dpdk dma

赞

踩

1、什么是DMA

DMA(Direct Memory Access,直接存储器访问)是一种高速的数据传输方式,允许在外部设备和存储器之间直接读写数据。数据既不通过CPU,也不需要CPU干预。整个数据传输操作在DMA控制器的控制下进行。但是这种方式存在多次访存的情况,而且还存在内存一致性问题,基于此intel提出DDIO技术,是对传统DMA技术的一个优化。DDIO允许I/O设备(如支持该技术的网卡)将数据直接写入或读取CPU的最后级缓存(LLC),而非内存。既然DDIO允许设备直接访问CPU的LLC,那么访问的过程中会涉及到pcie?带着这个疑问,我们继续探究第二个问题。

2、DDIO与PCIE的关系

正如上篇文章所讲,PCIe作为一种高速串行计算机扩展总线标准,是连接CPU与各种I/O设备(如网卡、存储控制器等)的主要通道。在采用DDIO技术的系统中,数据传输路径如下:当一个支持DDIO的I/O设备(如网卡)接收到数据时,它可以通过PCIe总线直接将这些数据传送给CPU的最后级缓存(LLC)。这个传输过程利用了PCIe提供的高速互连能力和数据带宽,即使得数据不必先经过内存,而是直接进入CPU缓存,减少了数据在内存和CPU之间来回移动的延迟。PCIe在此过程中扮演着关键角色,提供了高速、双向、点对点的数据传输信道,使得DDIO技术得以实现高效的数据交换。因此,DDIO技术的成功实施离不开PCIe总线所提供的高性能连接基础架构。

3、DMA的工作原理

3.1 初始化阶段

(1)网卡启动被设备识别时,告知CPU其具有DMA功能,并要求CPU分配一段连续的内存供DMA使用

(2)CPU根据设备的需求,在物理内存中预留一段区域并将其对应的物理地址提供给设备。这段内存区域被称为DMA缓冲区。

3.2 设置控制器

(1)DMA控制器是连接设备和内存之间的硬件组件,它负责管理DMA事务。

(2)设备驱动程序通常会设置DMA控制器的参数,如传输的方向(读或写)、源地址(设备地址或内存地址)、目的地址(内存地址)、传输大小等,并将这些参数存储在DMA通道的控制寄存器中。

3.3 启动DMA传输

(1)当有数据需要传输时,设备会激活其DMA控制器,指定相关的DMA通道开始数据传输。

(2)对于写操作,设备会将数据直接写入到内存的DMA缓冲区;对于读操作,则是从内存的DMA缓冲区读取数据。

3.4 CPU角色

(1)在DMA传输过程中,CPU并不直接参与数据搬运过程,而是可以执行其他任务,从而显著提升了系统的整体性能。

(2)只有在DMA事务开始前(初始化DMA控制器)和结束后(处理DMA完成中断),CPU才会介入进行必要的设置和清理工作。

3.5 DMA中断

(1)当DMA传输完成时,DMA控制器会触发一个中断通知CPU。

(2)CPU响应中断后,会执行相应的中断服务程序(ISR),确认DMA操作已完成,并可能进一步处理传输后的数据(如将网络数据包上传至协议栈处理)。

4、网卡DMA描述符环形队列

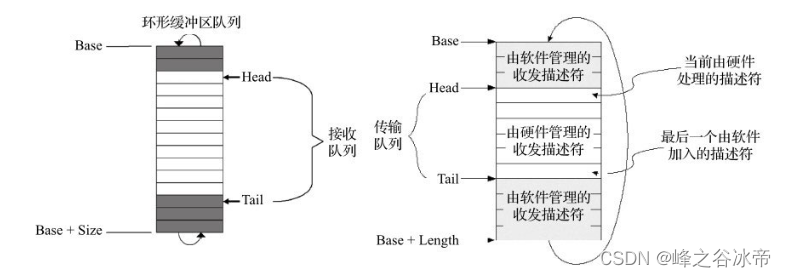

网卡DMA控制器通过环形队列与CPU交互。环形队列由一组控制寄存器和一块物理上连续的缓存构成。主要的控制寄存器有Base、Size、Head和Tail。通过设置Base寄存器,可以将分配的一段物理连续的内存地址作为环形队列的起始地址,通告给DMA控制器。同样通过Size寄存器,可以通告该内存块的大小。Head寄存器往往对软件只读,它表示硬件当前访问的描述符单元。而Tail寄存器则由软件来填写更新,通知DMA控制器当前已准备好被硬件访问的描述符单元

4.1 DMA描述符环形队列的运作原理

4.1.1 初始化阶段:

(1)DPDK在初始化网卡接收队列时,会分配一组连续的内存空间,用于存储接收描述符。每个描述符记录了内存中接收缓冲区(MBUFs)的物理地址和相关状态信息。

(2)这些描述符组成一个环形队列,即队列的最后一个描述符之后紧接着是第一个描述符,形成一个循环列表

4.1.2 接收数据包过程

(1)当网卡接收到数据包时,其内部的DMA引擎按照预先设定好的环形队列顺序读取描述符。

(2)根据描述符中的信息,DMA控制器将网络数据直接写入到主机内存中对应MBUF分配的缓冲区内。

(3)每个描述符写满后,DMA控制器自动更新描述符状态,表示数据包已经被成功放入内存。

4.1.3 CPU处理

(1)网卡完成数据包的DMA传输后,会触发一个中断通知CPU。

(2)CPU响应中断后,通过查询描述符的状态信息得知有哪些数据包已经接收完成,并进行后续处理,如解析包头、分发到不同的处理队列或转发到其他目的地。

4.1.4 轮询和空闲中断优化

DPDK还支持轮询(Polling)模式以及空闲中断(IDLE IRQ)等优化手段,进一步减少不必要的中断次数,提高CPU利用率和数据处理效率

pcie的讲解请看上一篇:深入浅出dpdk读书笔记--pcie与包处理(一)-CSDN博客