- 1flink调优(检查点/反压/内存)_flink 调优

- 2【Python 已解决】TypeError: unsupported operand type(s) for +: ‘int’ and ‘str’ —— 深度解析与解决策略_typeerror: unsupported operand type(s) for +: 'int

- 3最全docker--高级篇_docker高级

- 4vscode配置调用visual studio的编译和调试环境_vscode配置vs2019环境

- 5十分钟带你复现YOLOv8_yolov8复现

- 6理论+实操:docker入门初体验,申请阿里镜像加速器_阿里云docker镜像加速申请

- 7升力的产生_机翼升力库塔儒科夫斯基

- 8从零开始学习Java神经网络、自然语言处理和语音识别,附详解和简易版GPT,语音识别完整代码示例解析_gpt java

- 9数据仓库之事实表和维度表_数据仓库 事实表和维表 例子

- 102023年来钱最快副业python爬虫,任何人没看到我真的会伤心的好吧!_搞钱最快的副业

千兆网数据接收(一)_tcp和udp都可以用在千兆网卡上吗

赞

踩

OSI模型

OSI模型:开放式通信系统互联参考模型。个人认为在FPGA中主要关心的有网络层、传输层和物理层。

物理层----进行的是通信链路的硬件实现,通过PHY芯片实现一个节点到另一个节点的连接。物理地址通过MAC地址唯一标识。

网络层----该层实现的是数据的路由了,实现上下层数据的连接和转发。主要协议有:IP(IPV4、IPV6)。

传输层----建立、管理和维护端到端的连接。主要协议有TCP、UDP。

UDP

UDP和TCP

1、TCP 为可靠传输协议,而 UDP 为不可靠传输协议。即 TCP 协议可以保证数据的完整和有序,而UDP 不能保证;

2、UDP 由于不需要连接,故传输速度比 TCP 快,且占用资源比 TCP 少;

3、应用场合:TCP 协议常用在对数据文件完整性较高的一些场景中,如文件传输等。UDP 常用于对通讯速度有较高要求或者传输数据较少时,比如对速度要求较高的视频直播和传输数据较少的 QQ 等。

在FPGA开发中,并不是说TCP不能实现,但是实现起来无论时间成本、资源成本都是巨大的。

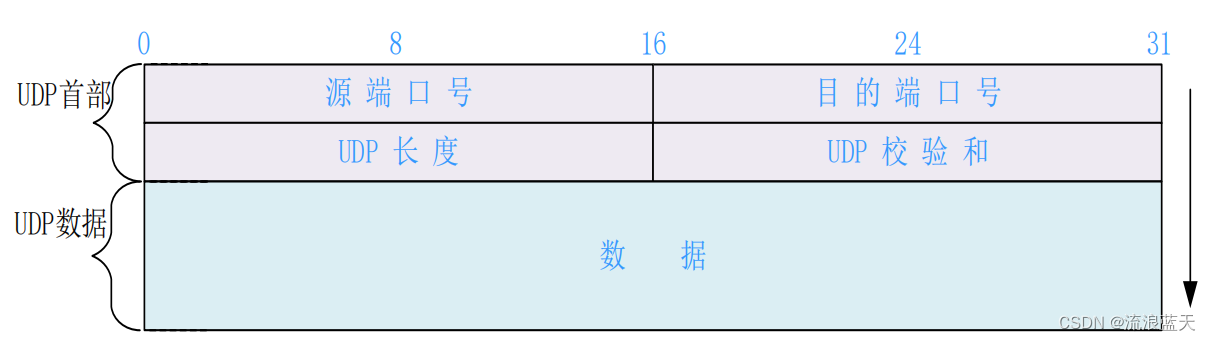

UDP协议

UDP 首部共 8 个字节,同 IP 首部一样,也是一行以 32 位(4 个字节)为单位。

源端口号:16 位发送端端口号,用于区分不同服务的端口,端口号的范围从 0 到 65535。

目的端口号:16 位接收端端口号。

UDP 长度:16 位 UDP 长度,包含 UDP 首部长度+数据长度,单位是字节(byte)。

UDP 校验和:16 位 UDP 校验和。

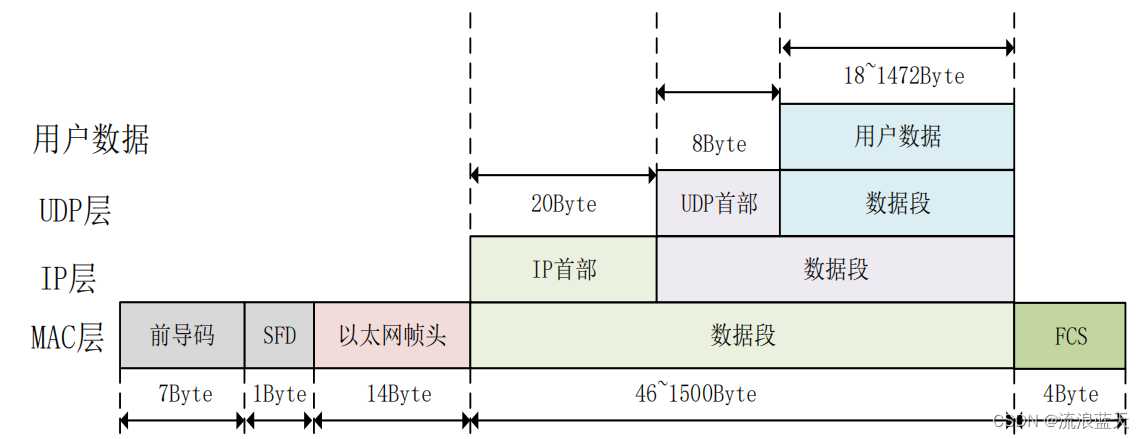

在以太网数据包中,数据是按照不同层的协议一层一层打包的:

也就是说,假如我想发送数据。那么首先我要把数据打包在UDP协议中得到a,然后再把a打包在IP协议中得到b,然后再把b打包在MAC头中进行发送。同理,当接收到一包数据时,我们需要“层层解包”,最终得到有效数据。

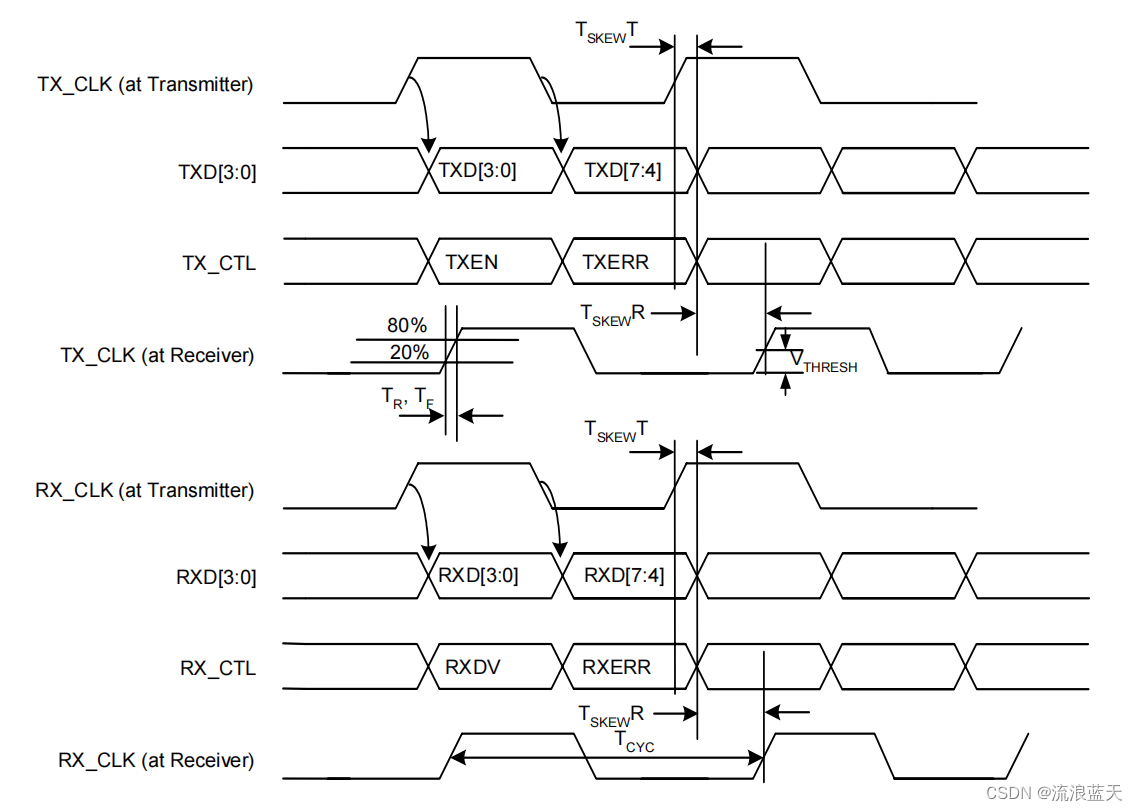

RGMII

在千兆以太网通信中常用的接口为RGMII和GMII,用于连接物理MAC和PHY芯片。相较于GMII,RGMII在时钟的上升沿和下降沿分别传输4bit数据,这样的话一个时钟周期就可以传输一个字节数据,并且节省了引脚资源。

RGMII 使用 4bit 数据接口,在 1000Mbps 通信速率下,ETH_TXC 和 ETH_RXC 的时钟频率为125Mhz。ETH_TXCTL 和 ETH_RXCTL 控制信号同样采用 DDR的方式在一个时钟周期内传输两位控制信号,即上升沿发送/接收数据使能(TX_EN/RX_ DV)信号,下降沿发送/接收使能信号与错误信号的异或值(TX_ERR xor TX_EN、RX_ERR xor RX_DV)。当 RX_DV 为高电平(表示数据有效),RX_ERR 为低电平(表示数据无错误),则异或的结果值为高电平,因此只有当ETH_RXCTL 和 ETH_TXCTL 信号的上下沿同时为高电平时,发送和接收的数据有效且正确。

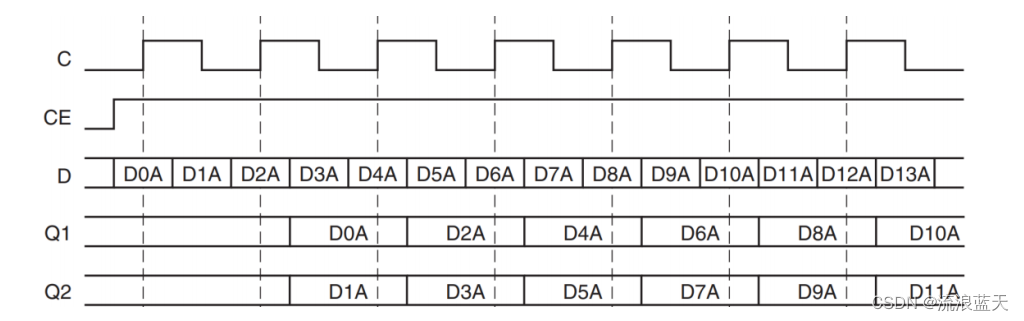

IDDR原语

原语是 Xilinx 器件底层硬件中的功能模块,它使用专用的资源来实现一系列的功能。IDDR可以将上下边沿DDR信号转换成单边沿的SDR信号。

IDDR有不同的采集模式,一般使用SAME_EDGE_PIPELINED模式,在时钟的上升沿输出SDR信号Q1和Q2,但是整体延迟一个时钟周期。

iddr_ctrl模块

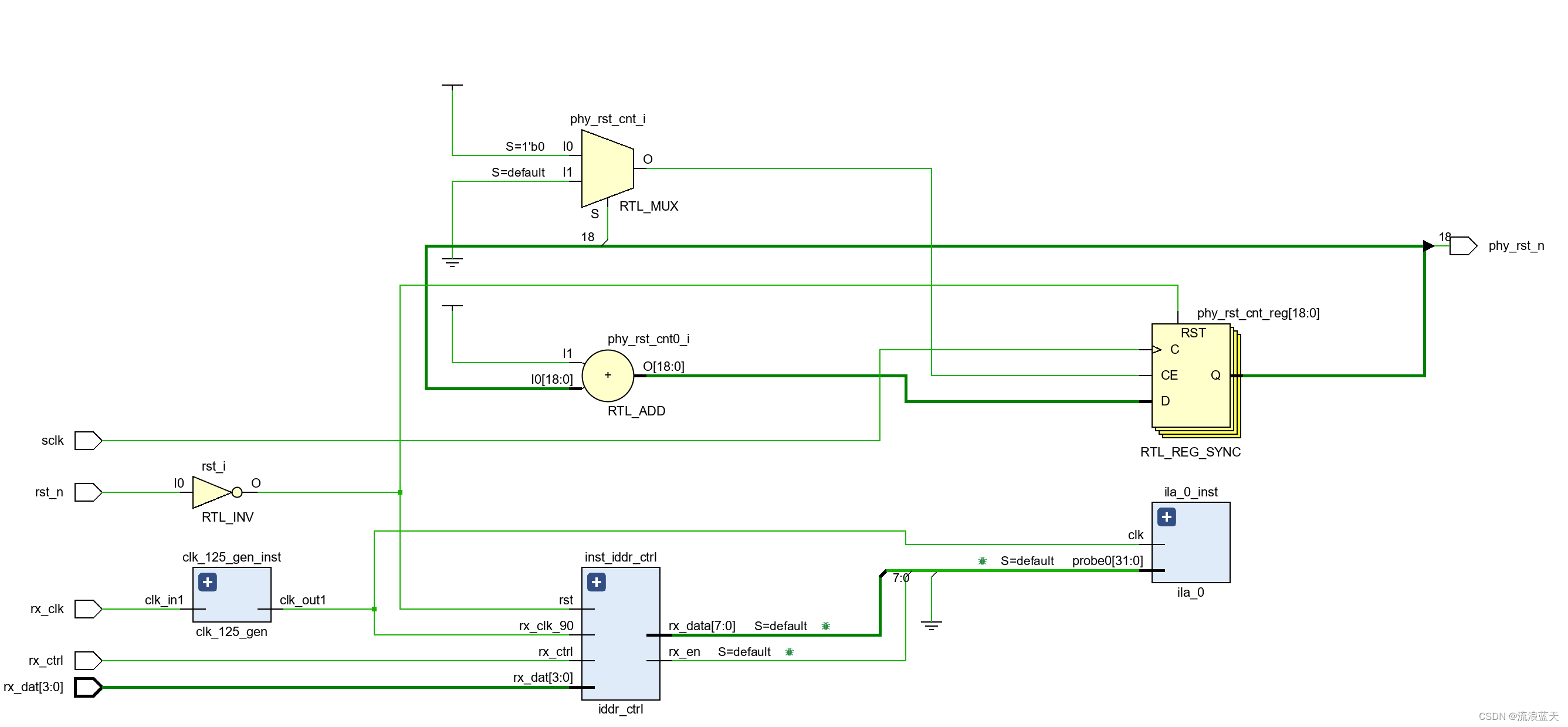

模块的框图如图所示。硬件引脚输入输入的DDR信号rx_dat[3:0]和rx_ctrl信号经过模块内的iddr源语转换为sdr信号如下如下rx_data[7:0]信号输出。

rx_clk_90是PHY时钟相移90°得到的,将 rx_clk_90 时钟作为 rx_ctrl 和 rx_dat 的采样时钟,这样采集rx_ctrl 和 rx_da 数据更为稳定。

将板卡连接至电脑,抓取rx_en信号上升沿。可以看到抓取到了以太网帧头中的前导码和界定符,说明已经将DDR信号转换。

未完待续。。。。。。