热门标签

热门文章

- 1el-table的各个属性5.17_el-table属性

- 2Dependency ‘org.springframework.cloud:spring-cloud-starter-config:‘ not found_dependency 'org.springframework.cloud:spring-cloud

- 3Windows的cmd运行编译器(cmd运行c/c++、python等)_windows cmd python

- 42023如果纯做业务测试的话,在测试行业有出路吗?_业务测试是不是最简单的

- 5MAC 安装PHP及环境配置 保姆级别_formula.jws.json: update failed, falling back to c

- 6xcode通过链接ssh 链接git_xcode 配置ssh

- 7fastapi响应数据处理_fastapi中間件修改響應

- 8一篇文章带你入门文件上传漏洞_如何利用文件上传漏洞

- 9c语言中输入一个字符串直到遇到回车为止,C语言程序设计实践第四章.pptx

- 10“BS,“ “PL,“ 和 “CF“ 是财务报告中常用的缩写,它们分别代表财务报表的不同部分_bs pl

当前位置: article > 正文

HackRF One硬件架构及参数简介_hackrf one元器件位置图

作者:你好赵伟 | 2024-04-26 21:46:14

赞

踩

hackrf one元器件位置图

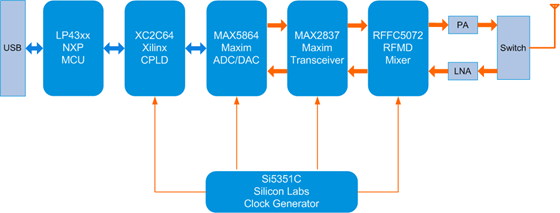

HackRF One硬件架构如图1所示。

图1 HackRF One硬件架构图[1]

- PC机通过USB接口与NXP LP43xx微控制器通信

- 微控制器通过并行总线及GPIO模拟的JTAG接口与CPLD连接

- MAX5864对【发送的数据】进行数模转换DAC,对【接收到的数据】进行模数转换ADC

- MAX2837完成上/下变频,并通过宽带混频器RFFC5072提高频率范围

- 射频前端采用一级LNA/PA进行放大,并最终通过TR Switch与天线连接

LPC4320/4330: ARM Cortex M4处理器, 主频204MHz

XC2C64A:Xilinx,CoolRunner-II系列CPLD,1500门

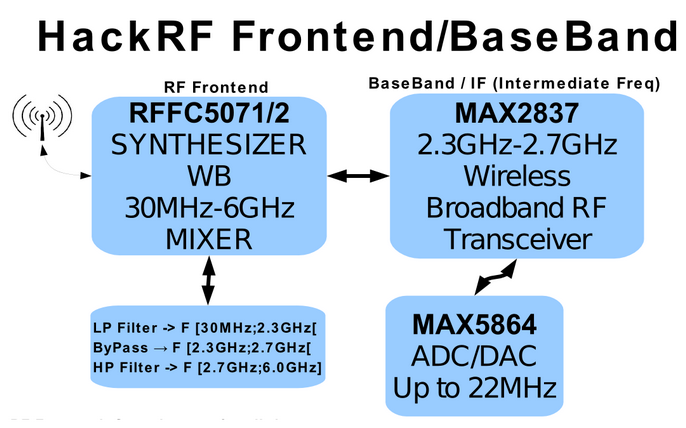

MAX2837:2.3GHz to 2.7GHz 无线宽带射频收发器

RFFC5072:混频器,提供80MHz到4200MHz的本振

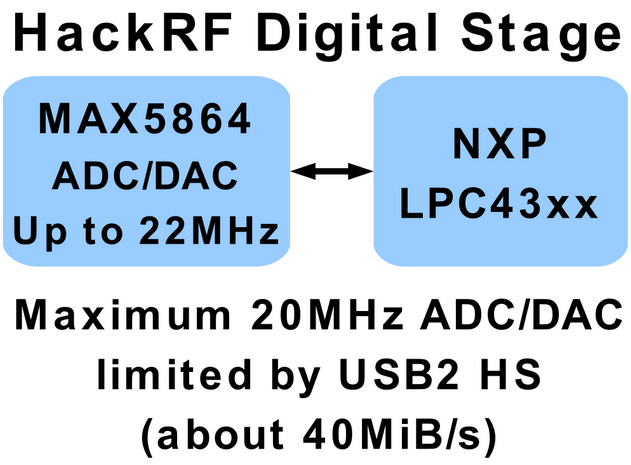

MAX5864:ADC/DAC, 8-bit,22MHz采样率

Si5351C:I2C可编程任意CMOS时钟生成器

MGA-81563:0.1–6GHz 3V, 14 dBm 放大器

SKY13317:20 MHz-6.0 GHz 射频单刀三掷(SP3T)开关

SKY13350:0.01-6.0 GHz 射频单刀双掷(SPDT)开关

图2 HackRF Frontend/Baseband[2]

图3 HackRF Digital Stage[2]

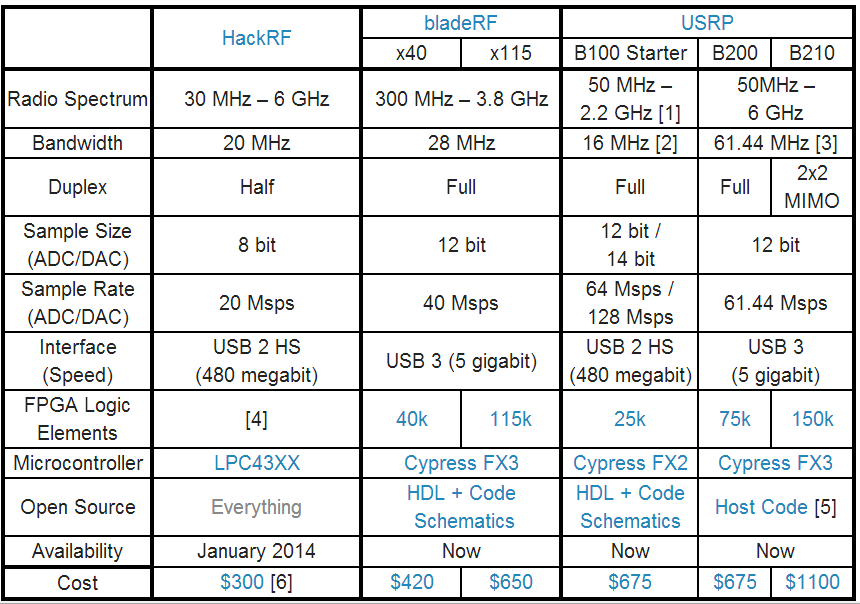

图4 HackRF One参数[3]

参考文献:

[1]http://bbs.eeworld.com.cn/thread-465790-1-1.html

[2]https://github.com/mossmann/hackrf/wiki/Hardware-Components

[3]http://www.taylorkillian.com/2013/08/sdr-showdown-hackrf-vs-bladerf-vs-usrp.html

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/你好赵伟/article/detail/493239

推荐阅读

相关标签