热门标签

热门文章

- 1去哪里找抖音短视频素材?告诉大家几个抖音短视频素材下载资源_抖音资源哪里找

- 2Linux权限有哪些?500代表什么意思?_权限500啥意思

- 3软件测试面试题及答案_软件测试上机考试面试

- 4【机器学习入门】拥抱人工智能,从机器学习开始

- 5微信小程序使用ColorUI组件库_微信小程序只引用部分colorui组件

- 6使用Typecho搭建个人博客网站,并内网穿透实现公网访问

- 7算法沉淀——BFS 解决拓扑排序(leetcode真题剖析)_bfs拓扑排序

- 8pytorch实现word embedding :torch.nn.Embedding_pytorch embedding python 实现

- 9JVM笔记_java 虚拟机的类型

- 10【OpenVINO】基于 OpenVINO Python API 部署 RT-DETR 模型_openvino 的github链接

当前位置: article > 正文

LIN信号显隐性电平测试——踩坑_lin tx rx的电压不一致会产生位错误吗

作者:在线问答5 | 2024-07-28 07:48:19

赞

踩

lin tx rx的电压不一致会产生位错误吗

测试环境

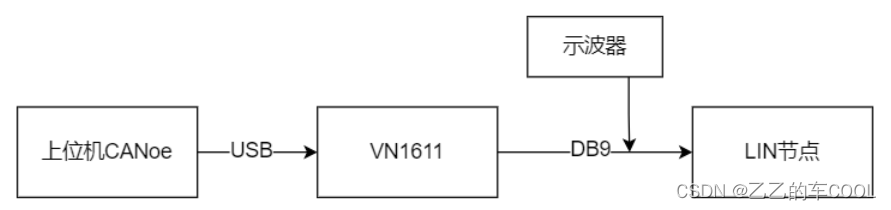

在LIN总线协议一致性测试中,针对物理层会进行显隐性状态下LIN信号电平测试来验证LIN显隐性状态下电平信号是否满足设计要求。主从节点的测试方法相同,在LIN节点级测试搭建桌面环境如下图,使用CANoe软件+VN1611+小电源+示波器(或picoscope)进行测试验证。DB9的接线众所周知采用PIN7接LIN,PIN3接地。

问题描述

存在一个LIN隐性电平问题,在测试低于12v电压case中被测DUT的电压值会出现偏差,隐性电平被拉高。

原因分析

接上VN1611接口卡后,由于接口卡一端通过USB线接到上位机,可能是其供电电压的影响,被测DUT的电压值会出现偏差,导致测出的隐性电平被拉高。并且主要存在于接口卡电压大于供电电压时的测试场景。

解决方案

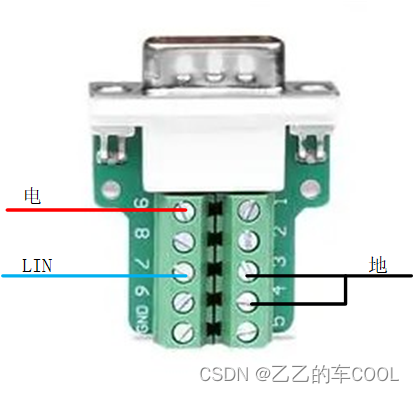

既然怀疑是VN1611接口卡带电导致的,查阅硬件资料如下图Note所描述:如果PIN4(Pdis,power disable)连接到PIN3 (VB-),则内部电源关闭。在这种情况下,需要一个外部电源在PIN9 (VB+)。

因此,原本PIN7接LIN,PIN3接地的方式确实没有屏蔽掉接口卡内部电源。所以DB9改接线如下图。但是当调节电压很低或很高的情况下,DUT还在工作,接口卡也不会停止工作。至此,LIN隐性电平被拉高的问题得以解决。

提示:VN1630接口卡同样适用此方法。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/在线问答5/article/detail/893314

推荐阅读

相关标签