热门标签

热门文章

- 1AIGC文生图PixArt-Sigma使用;StableDiffusion3使用

- 2组合筛选vue_Vue 3 组合式 API 介绍

- 3群晖NAS实现Video Station显示视频封面_群晖video station 封面

- 4java 控制台输出 样式_自定义SpringBoot控制台输出的图案

- 5WPF: 针对Windows 8优化菜单栏和工具栏

- 6CVE-2014-0160-心脏滴血漏洞

- 7使用Neo4j和Langchain创建知识图谱_langchain neo4j

- 8数据挖掘实战-基于内容协同过滤算法的电影推荐系统_协同过滤算法 sklearn 电影推荐

- 9如何读源码-方法论总结_源码阅读方法论

- 10resvg-js:高性能SVG渲染库的首选

当前位置: article > 正文

数字频率计Verilog代码Quartus DE1-SoC开发板_数字瞬时频率测量 verilog

作者:天景科技苑 | 2024-06-29 05:06:59

赞

踩

数字瞬时频率测量 verilog

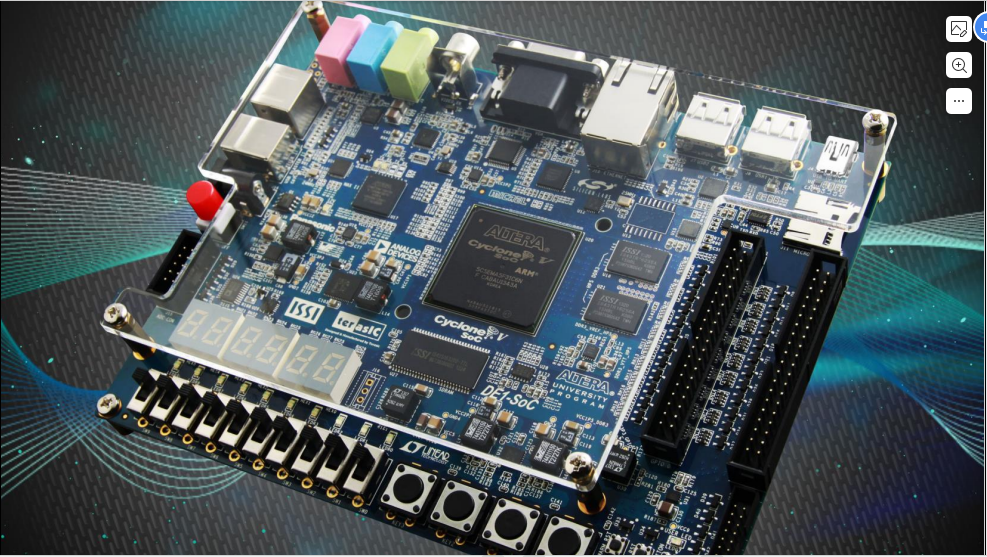

名称:数字频率计Verilog代码Quartus DE1-SoC开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

数字频率计 采用一个标准的基准时钟,在1s里对被测信号的脉冲数进行计数,即为信号频率利用等精度测量法可以测量1hz至99999999Hz信号频率

七段码管显示测量值

本代码已在DE1-SoC开发板验证,DE1-SoC开发板如下,其他开发板可以修改管脚适配:

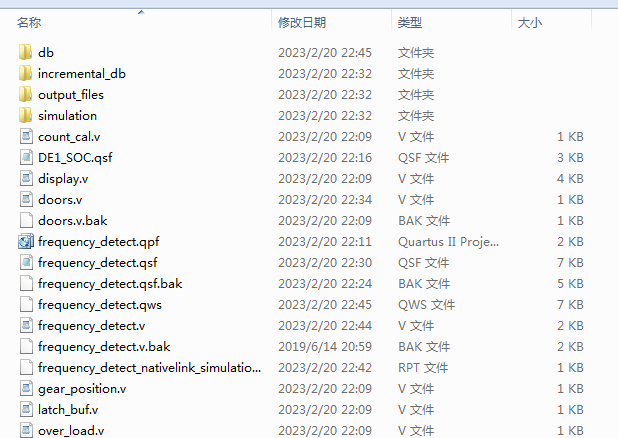

1. 工程文件

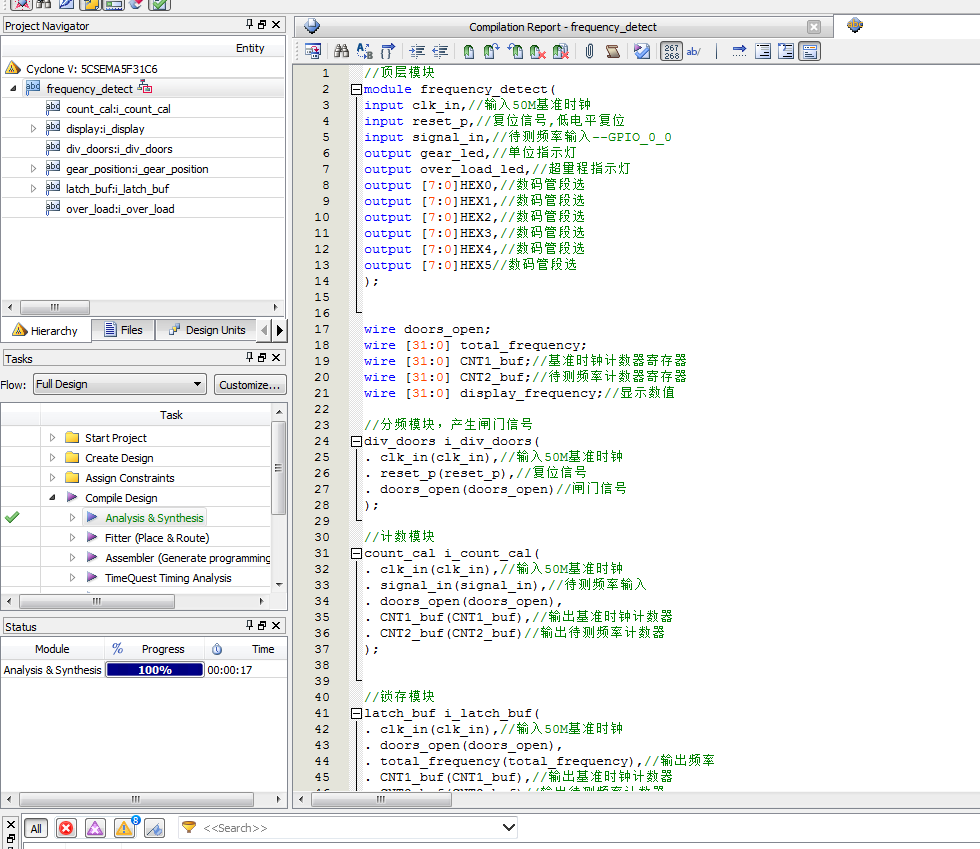

2. 程序文件

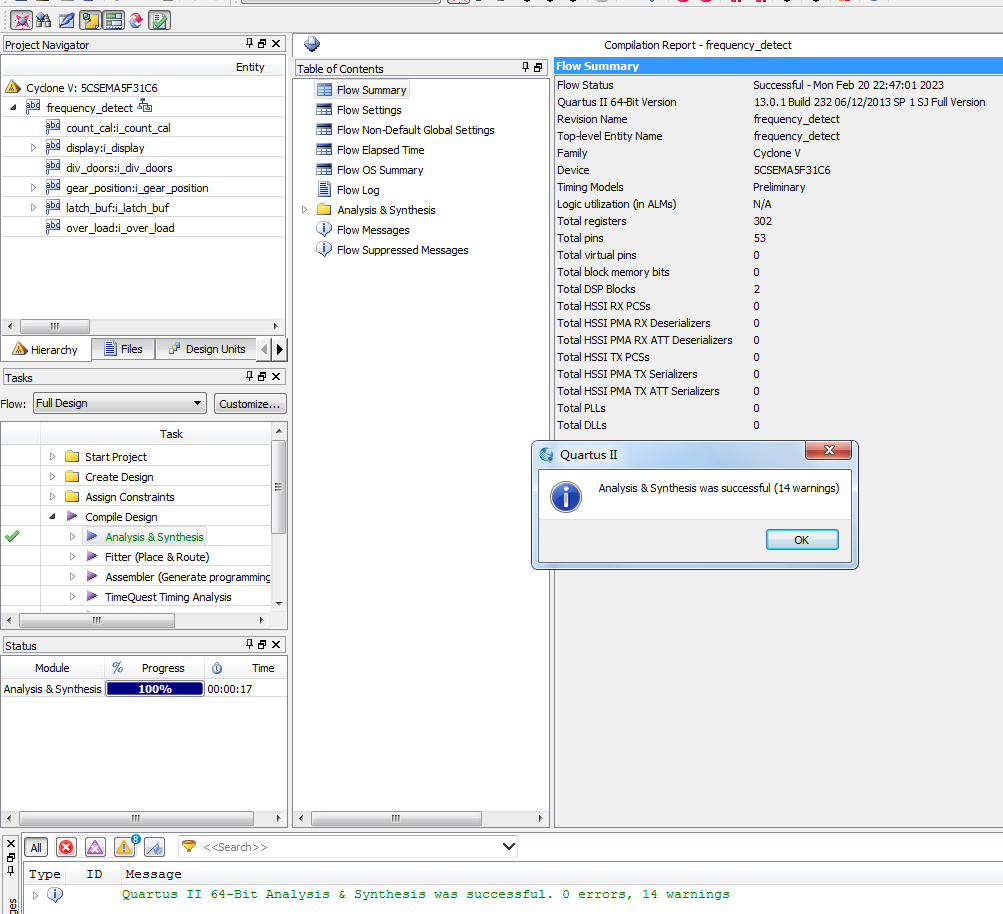

3. 程序编译

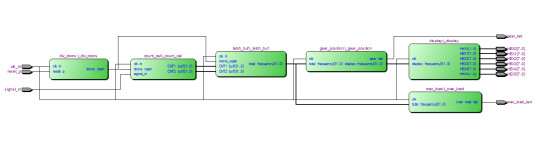

4. 程序RTL图(结构图)

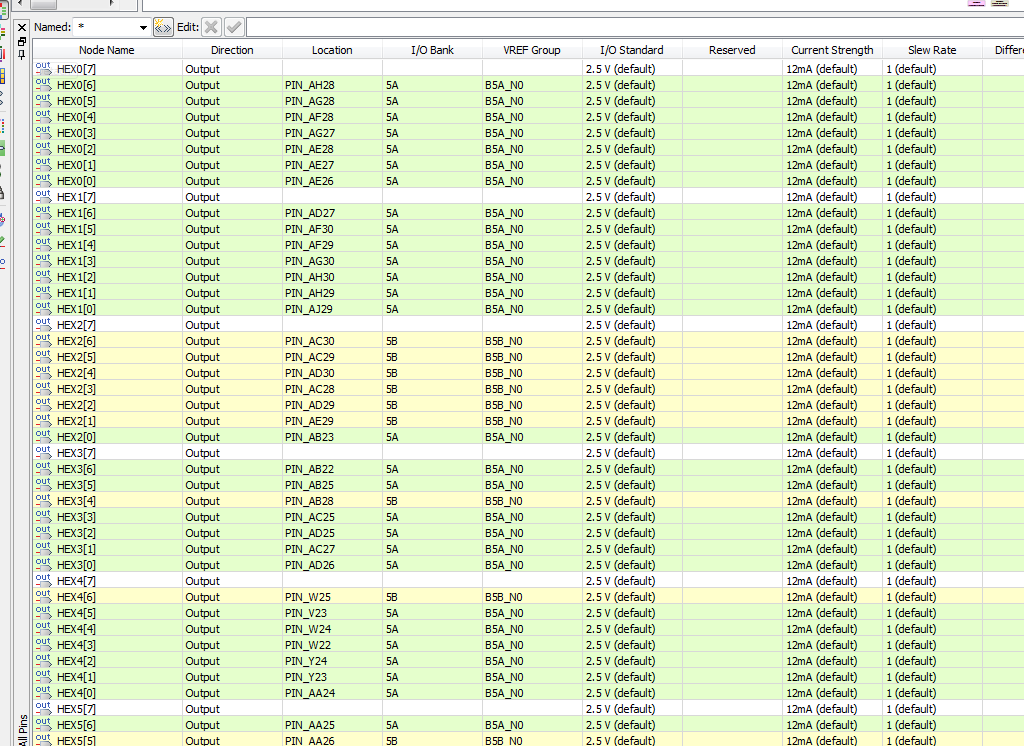

5. 管脚分配

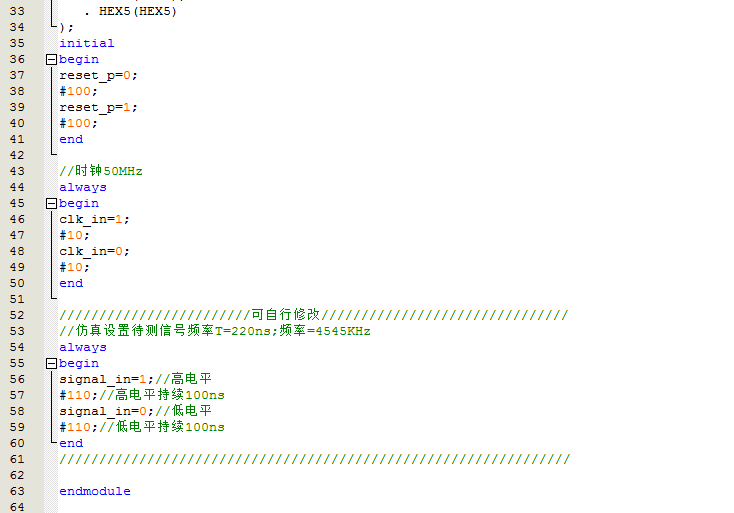

6. Testbench

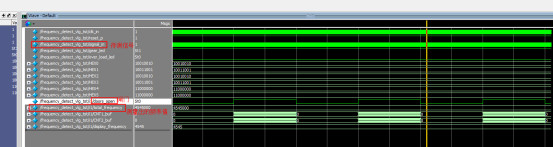

7. 仿真图

整体仿真图

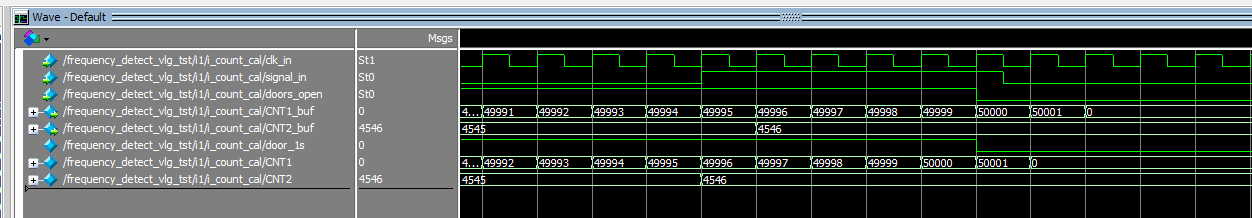

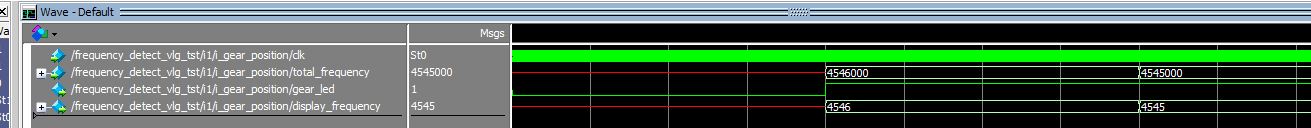

计数模块

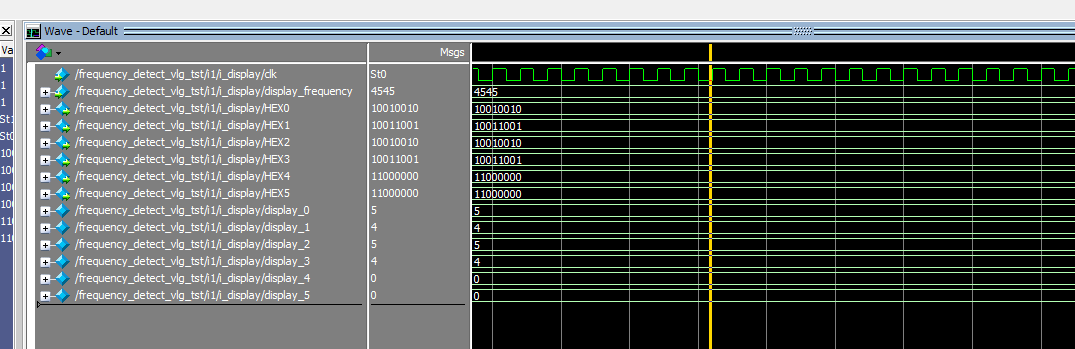

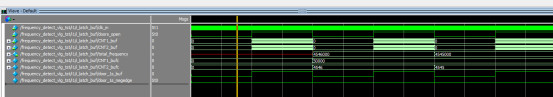

显示模块

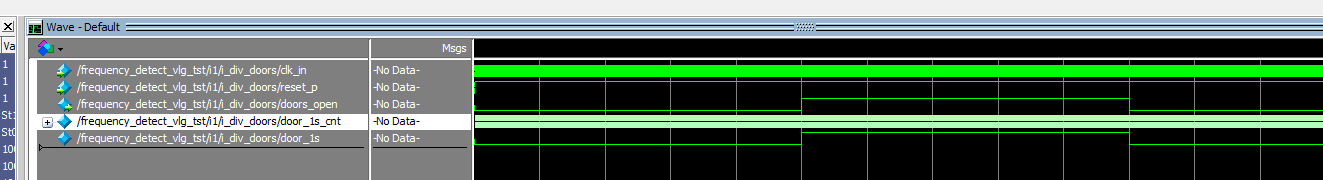

闸门信号产生模块

单位选择模块

锁存模块

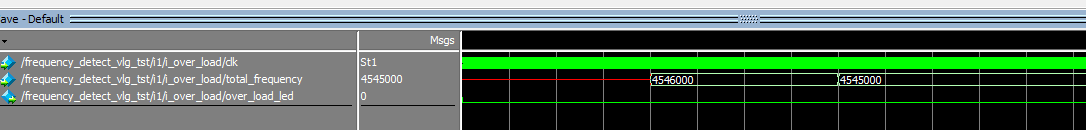

超量程模块

部分代码展示:

//顶层模块 module frequency_detect( input clk_in,//输入50M基准时钟 input reset_p,//复位信号,低电平复位 input [7:0] SW,//频率调节开关 input signal_in,//待测频率输入--GPIO_0_0 output gear_led,//单位指示灯 output over_load_led,//超量程指示灯 output [7:0]HEX0,//数码管段选 output [7:0]HEX1,//数码管段选 output [7:0]HEX2,//数码管段选 output [7:0]HEX3,//数码管段选 output [7:0]HEX4,//数码管段选 output [7:0]HEX5//数码管段选 ); wire doors_open; wire [31:0] total_frequency; wire [31:0] CNT1_buf;//基准时钟计数器寄存器 wire [31:0] CNT2_buf;//待测频率计数器寄存器 wire [31:0] display_frequency;//显示数值 wire clk_out; //分频模块,产生自测频率 clk_div i_clk_div( . clk_in(clk_in),//输入50M基准时钟 . SW(SW),//频率调节开关 . clk_out(clk_out)//待测频率 ); 分频模块,产生闸门信号 div_doors i_div_doors( . clk_in(clk_in),//输入50M基准时钟 . reset_p(reset_p),//复位信号 . signal_in(clk_out), . doors_open(doors_open)//闸门信号 ); //计数模块 count_cal i_count_cal( . clk_in(clk_in),//输入50M基准时钟 . signal_in(clk_out),//待测频率输入 . doors_open(doors_open), . CNT1_buf(CNT1_buf),//输出基准时钟计数器 . CNT2_buf(CNT2_buf)//输出待测频率计数器 ); //锁存模块 latch_buf i_latch_buf( . clk_in(clk_in),//输入50M基准时钟 . doors_open(doors_open), . total_frequency(total_frequency),//输出频率 . CNT1_buf(CNT1_buf),//输出基准时钟计数器 . CNT2_buf(CNT2_buf)//输出待测频率计数器 ); //单位选择模块 gear_position i_gear_position( . clk(clk_in), . total_frequency(total_frequency),//频率 . gear_led(gear_led),//单位指示灯 . display_frequency(display_frequency)//显示数值 ); //超量程指示模块 over_load i_over_load( . clk(clk_in), . total_frequency(total_frequency),//频率 . over_load_led(over_load_led)//超量程指示灯 ); //数码管显示模块 display i_display( . clk(clk_in), . display_frequency(display_frequency),//输出频率 . HEX0(HEX0), . HEX1(HEX1), . HEX2(HEX2), . HEX3(HEX3), . HEX4(HEX4), . HEX5(HEX5) ); endmodule

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/天景科技苑/article/detail/768334

推荐阅读

相关标签