vivado CLOCK_REGION_vivado region

赞

踩

描述

出于计时的目的,每个设备被划分为多个时钟区域。CLOCK_REGION是

标识Xilinx FPGA或由一组服务的设备的区域的设备对象

计时资源。时钟区域包含可配置逻辑块(CLB)、DSP片、以及其它可配置逻辑,

块RAM、互连和相关的时钟。

时钟区域的数量随着设备的大小而变化。UltraScale设备是

被划分为分段的时钟区域的列和行。这些时钟区域不同于

以前的族,因为它们排列在平铺中,并且不跨越的宽度的一半

装置

对于UltraScale设备,时钟区的高度是60个CLB、24个DSP片和12个块

RAM,在其中心具有水平时钟脊(HCS)。每个银行有52个I/O,4个

与时钟区域间距匹配的千兆收发器(GT)。

对于7个串联设备,时钟区域包含50个CLB和一个具有50个I/O的I/O组,以及

在其中心的水平时钟行(HROW)。

时钟区域中的I/O组具有时钟引脚,可将用户时钟带到时钟上

在时钟区域内路由资源。

请参阅7系列FPGA时钟资源用户指南(UG472)[参考文献3]或UltraScale

有关时钟的更多信息,请参阅《建筑时钟资源用户指南》(UG572)[参考文献9]

区域及其所包含的资源。

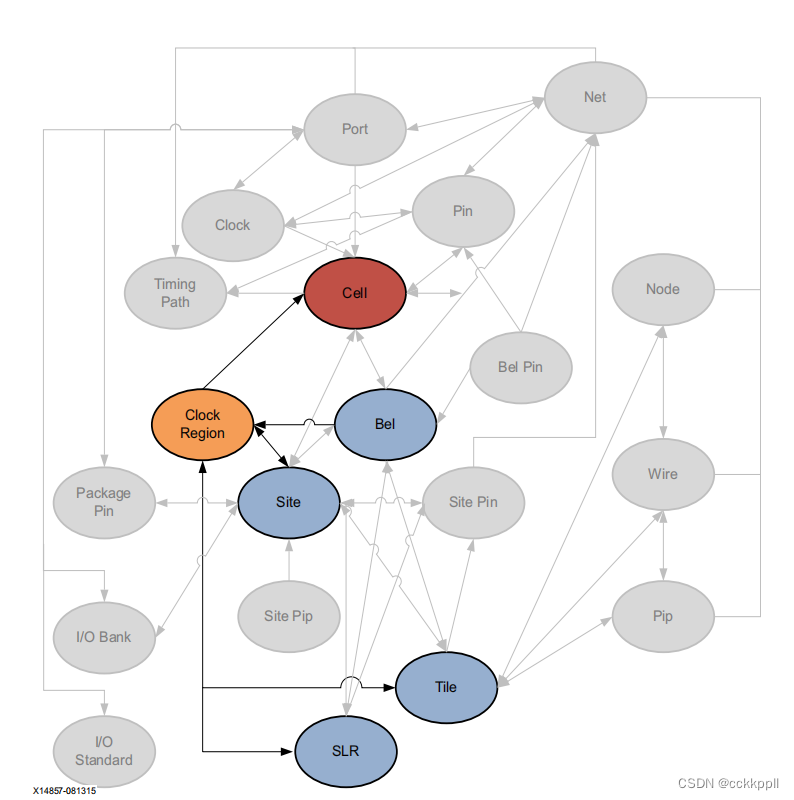

相关对象

CLOCK_REGION对象与设备上的超级逻辑区域(SLR)相关联

在中找到区域,或者在时钟中找到TILE、SITE或PACKAGE_BANK设备对象

区域此外,您还可以获得CELL网表对象已被

放入。

可以使用类似于的Tcl命令查询关联对象的CLOCK_REGION

如下,返回指定单元所在的时钟区域:

get_clock_regions-of[get_cells usbEngine0/u1/u0/crc16_sum_reg[7]]

此外,您还可以查询关联的SLR、TILE、SITE、BEL和IO_BANK设备对象

具有CLOCK_REGION,或在CLOCK_REGION中找到。例如,以下Tcl命令返回

指定单元所在的同一时钟区域中的I/O组:

get_iobanks-of _objects[get_clock_regions-of\

[get_cells usbEngine0/u1/u0/crc16_sum_reg[7]]]

属性

可以使用report_property命令报告

CLOCK_REGION。请参阅Vivado Design Suite Tcl命令参考指南(UG835)

[参考文献13]了解更多信息。

clock_region对象上的属性包括以下内容,并带有示例值: