热门标签

热门文章

- 1FFmpeg详解及常用命令使用

- 2WAIC | 斯梅尔数学与计算研究院邀您莅临WAIC 2024“数学与人工智能”论坛_#waic2024 推出首支ai原创主题曲——《waic 正青春》,这首歌曲不仅是ai与音乐

- 3使用SciPy.optimize.linprog函数解决线性规划问题指南_scipy linprog

- 4Apache HTTP server benchmarking tool(ab)-服务器基准测试工具一文上手(1)_压力测试报443

- 5Facebook如何运用机器学习进行亿级用户数据处理

- 6基于STM32单片机智能灯光照明灯台灯路灯光照检测蓝牙设计20-178_stm32智能蓝牙台灯

- 7新晋管理者的十大行为误区_新晋管理者管理误区

- 8华为校招开奖,岗位职级薪资汇总(精华面经分享)_华为14a和14b哪个高

- 9消息队列常见问题(1)-如何保障不丢消息_消息业务层保证不丢消息方案

- 102023年程序员找工作难的原因_it程序员找工作很难

当前位置: article > 正文

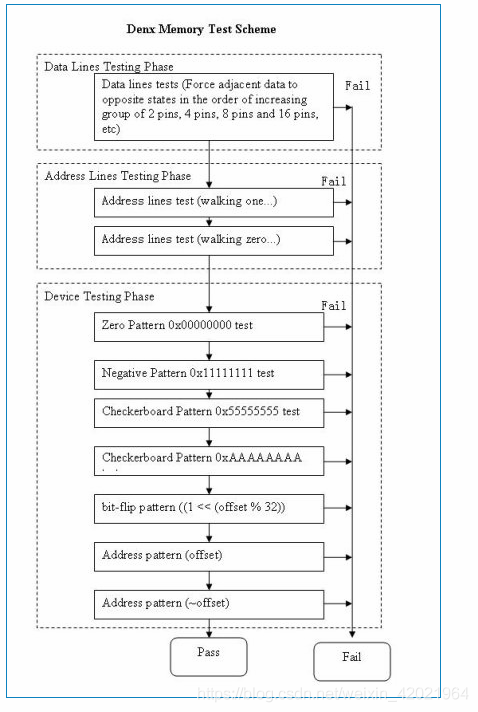

DDR SDRAM内存测试的一种官方方案(简单易懂)_cpu到ddr的测试pattern

作者:天景科技苑 | 2024-07-13 14:37:08

赞

踩

cpu到ddr的测试pattern

#话不多说,先上图,再上代码!

- ddr_base = DDR_BASE;

- ddr_size = 0x100000; // Partial memory range

-

- if ( memfill32( ddr_base, ddr_size, 0xffffffff ) )

- errors += 0x01;

-

- if ( memfill32( ddr_base, ddr_size, 0xaaaaaaaa ) )

- errors += 0x02;

-

- if ( memfill32( ddr_base, ddr_size, 0x55555555 ) )

- errors += 0x04;

-

- if ( memfill32( ddr_base, ddr_size, 0x00000000 ) )

- errors += 0x08;

-

-

-

-

- Uint32 memfill32( Uint32 start, Uint32 len, Uint32 val )

- {

- Uint32 i;

- Uint32 end = start + len;

- Uint32 errorcount = 0;

-

- /* Write Pattern */

- for ( i = start; i < end; i += 4 )

- {

- *( volatile Uint32* )i = val;

- }

-

- /* Read Pattern */

- for ( i = start; i < end; i += 4 )

- {

- if ( *( volatile Uint32* )i != val )

- {

- errorcount++;

- break;

- }

- }

-

- return errorcount;

- }

- DDR2的寻址方式,为 行地址+列地址+bank地址寻址,理解成2维表格就可以,你是哪一张纸上的二维表格(bank),横纵坐标定位(行列地址)。

- 测数据肯定得写呀,比如你有2根数据线,你写个值 0b 01,读出来是0b 10 ,00 ,11都说明你硬件有问题。连线就不对。当然了,肯定不止有2根数据线了,延伸到你有16位数据线,你写0xaaaa(1010 1010 1010 1010),如何能读到0xaaaa,说明你的硬件连线奇偶顺序是对的,因为奇数位都是0,偶数位都是1,错误也只能是第一位和第三位,或者第五位顺序跌倒。

- 如果上一步过了,就写数据0b 1100 1100 1100 1100,即0xcccc,把相邻2根线合并为一组,来缩小奇偶范围,接着4根线合并为一组,8根线一组,测完就可以知道你的硬件布线是否出错了。

- 以上就是原理,和代码不是完全对照,可以参考理解。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/天景科技苑/article/detail/820017

推荐阅读

相关标签