AXI Quad SPI IP核子模块_startupe3

赞

踩

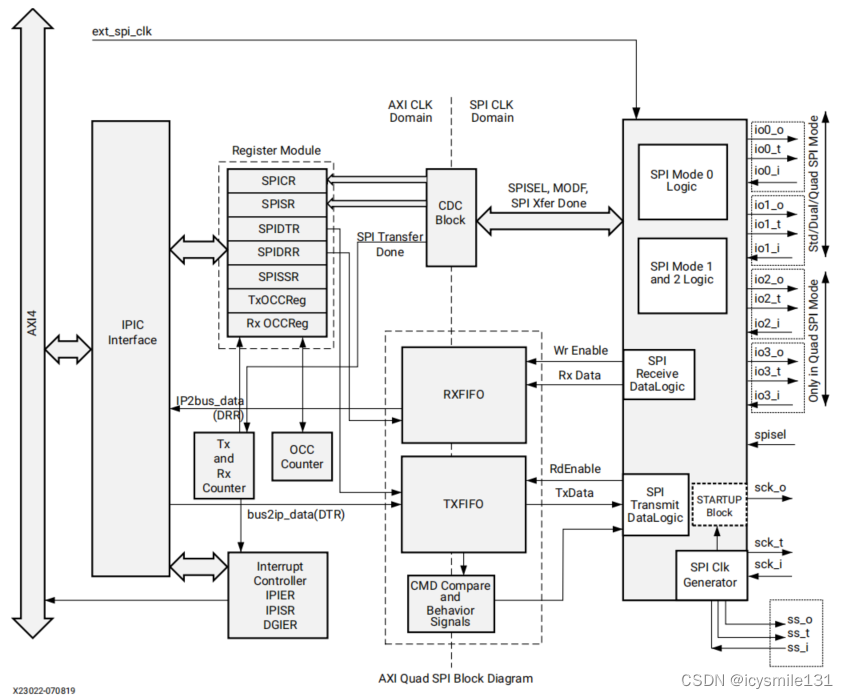

当选择Enable Performance Mode选项时,AXI Quad SPI IP核向后兼容所有早期版本的AXI Quad SPI IP核。该IP核包括以下子模块:

AXI4-Lite 接口模块

AXI4-Lite接口模块为AXI4-Lite协议和IPIC提供接口。AXI4Lite接口上的读写事务被转换为等效的IP

互连(IPIC)事务。这是该IP核的默认组合。

SPI 寄存器模块

SPI寄存器模块包括下图所示的所有内存映射寄存器,这些寄存器用于配置和控制 SPI IP核的行为。该模块连接到AXI4-Lite接口,由状态寄存器、控制寄存器、N位从设备选择寄存器(N≤32用于选择连接到SPI总线的不同从设备)以及一对发送和接收寄存器组成。

中断控制器寄存器集模块

由与中断相关的寄存器组成,包括:设备全局中断使能寄存器(DGIER)、IP中断使能寄存器(IPIER)和IP中断状态寄存器(IPISR)。

SPI 模块

SPI模块由一个移位寄存器、一个参数化波特率生成器(BRG)和一个控制单元组成。它提供SPI接口,包括控制逻辑和初始化逻辑。在标准SPI模式下,此模块是SPI操作的核心。

可选的FIFOs

当参数Enable FIFO被启用时,发送FIFO和接收FIFO在发送和接收路径上实现。发送FIFO的宽度和接收FIFO是相同的,并且取决于事务宽度(Transaction Width)参数。当标准SPI模式被启用时,启用或禁用FIFO,深度变量为16或256。

在dual SPI和quad SPI模式中,FIFO深度为16或256个位置(字节)。

STARTUPEn模块

STARTUPE2原语适用于Xilinx 7系列设备。STARTUPE3原语是适用于Xilinx UltraScale设备。

启用STARTUPE2原语参数

STARTUPE2是Xilinx设备中的一个原语。该原语可以在设计中FPGA配置之后使用。通过选择或设置Enable STARTUPE2 Primitive参数,可以确保STARTUPE2被包括在你的设计或配置中。STARTUPE2原语存在于7系列和Zynq®-7000 SoC设备中,它有一个专用的时钟引脚,可用于

将SPI时钟提供给从存储器。STARTUP原语的输出端口连接到作为STARTUP2接口的IP核模块顶层接口,这是为了确保FPGA在启动时能够正确地初始化,并将必要的状态或信号传递给IP核逻辑。Spartan-7 7S6 和7S15 FPGA不支持STARTUPE2.CLK-UserClk启动时钟引脚。

启用STARTUPE3原语参数

STARTUPE3原语存在于UltraScale设备中。这个原语有一个专用的时钟和数据引脚,可用于向从设备提供SPI时钟和数据接口。

STARTUPE3提供的SPI接口可以直接连接到从设备,如SPI Flash,用于FPGA的启动配置、程序存储或其他需要非易失性存储的应用。