- 1软件测试工程师面试题-功能测试(测试理论)_面试测试,问你功能实现逻辑

- 2MySQL事务底层原理和MVCC机制_数据库事务实现的底层机制

- 3springcloudalibaba版本发布说明

- 4Java Math类,Math类小练习_math类练习题

- 5比阿里EMO抢先开源!蔡徐坤“复出”唱RAP,腾讯AniPortrait让照片变视频,鬼畜区UP狂喜!看看哪家效果好

- 6基础:Zookeeper、Eureka、Nacos、Consul ,Etcd选型_zookeeper consul

- 7谷歌aab包在Android 14闪退而apk没问题(targetsdk 34)_targetsdk 34 闪退

- 8git add 后如何撤销?_git add * -f提交了 怎么撤回

- 9hadoop-完全分布式搭建_hadoop完全分布式

- 10读论文:图像分割综述_论文分割综述

FPGA(三)触发器与锁存器_两个输入端交叉耦合的与非门构成

赞

踩

前言

大多数数字系统中,除了需要具有逻辑运算和算数运算功能的的组合逻辑电路外,还需要具有存储功能的电路。组合电路与存储电路结合构成时序逻辑电路,简称时序电路。这章内容主要讨论实现存储功能的两种逻辑单元电路:锁存器和触发器。一、基本双稳态电路

根据我的数电书的介绍,各种锁存器和触发器,都是以基本双稳态电路为基础的,所以,首先大致讲一下基本双稳态电路。

最基本的双稳态电路的构成是将两个非门G1和G2接成如下图所示的交叉耦合形式。

- Q置1,那么Q’=0。这叫做基本双稳态电路的1状态

- Q置0,那么Q’=1。这叫做基本双稳态电路的0状态

该电路拥有1和0两种状态,一旦进入其中一种状态,就能长期保持不变。所以它又叫做双稳态存储电路。

双稳态电路的功能极不完备。在接通电源后,它可能随机进入1状态或0状态,因为没有控制机构,所以也无法在运行中改变和控制它的状态,从而不能作为存储电路使用。(即不具有实用性、可靠性)

二、锁存器

1. 或非门SR锁存器

将基本双稳态电路的非门换成或非门,则构成下面所示的基本SR锁存器,它是一种具有最简单控制功能的双稳态电路。相比基本双稳态电路,SR锁存器有两个输入端S和R。在数字电路中,“S”一般表示“Set”(高电平有效),“R”表示“Reset”(低电平有效).

功能表为:

通过对功能表的分析,为保证锁存器始终处于工作于定义状态,输入信号应遵守SR=0的约束条件,即不允许S=R=1 .

工作波形为:

当时了,并不是出现了S=R=1后,SR锁存器就进入了不可确定的状态。如果S或R有一方先置1,另一个稍后置1,则Q或Q’其中一个就会在S和R都置1时,置为0。如果S和R的1电平不同时撤销,此后的输出状态仍然是可以确定的,如下图中③和④所示:

2. 与非门SR锁存器

其实,不止有与非门构成的SR锁存器,还有或非门构成的基本SR锁存器。

3. D锁存器

与SR锁存器不同,D锁存器在工作中不存在非定义状态,因而得到广泛应用。目前,CMOS集成电路主要采用传输门控D锁存器和逻辑门控D锁存器两种电路结构,特别是前者电路结构简单、在芯片中占用面积小而更受青睐。

① 传输门控D锁存器

在基本双稳态电路中插入两个传输门TG1和TG2,则可以构成下面的传输门控D锁存器。

功能表为:

② 逻辑门控D锁存器

逻辑门控D锁存器在门控SR锁存器的S和R输入端之间连接了一个非门G5,从而保证了SR=0的约束条件,消除了可能存在的非定义状态。

三、触发器

锁存器是一种脉冲电平敏感的存储单元。最主要的特点是具有使能性的锁存电平功能,即在使能信号有效时,可以锁住输出信号保持不变,而在使能信号失效时,输出与输入相同,等效于一个输出缓冲器。

触发器又叫双稳态触发器,随着输入的变化,输出会产生对应的变化。它通常是由至少两个相同的门电路构成的具有反馈性质的组合逻辑电路。应用中为了使触发过程容易控制,而做成由时钟触发控制的时序逻辑电路。

常见的有SR触发器,D触发器,JK触发器。触发器通常有两种状态,保持态和转化态,分别对应两种输入情况,在保持态下输出会维持在当前状态不改变,而在转化态下输出会按规律顺序改变。

数电书上有这样一段,大致描述了触发器与锁存器的差异,也给触发器下了一个简单的定义:

如前所述的D锁存器,它的输出会随输入信号变化。而很多时序电路要求存储电路只对时钟信号的上升沿或下降沿敏感,而在其它时刻保持状态不变。(前面两句话是差异) 这种对时钟脉冲边沿敏感的状态更新称为触发,具有触发工作特性的存储单元成为触发器。(触发器的定于) 电路结构不同的触发器对时钟脉冲的敏感边沿可能不同,分为上升沿触发和下降沿触发。

目前应用的触发器主要有三种电路结构:主从触发器、维持阻塞触发器和利用传输延迟的触发器。

1. 主从D触发器

将两个D锁存器级联,则构成典型的COMS主从D触发器,左边的锁存器称为主锁存器,右边的称为从锁存器,主从的使能信号相位相反,利用两个锁存器的交互锁存,则可实现存储数据和输入信号之间的隔离。

下图中CP表示时钟信号。

分析过程如下:

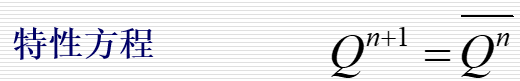

2. 触发器的逻辑功能

触发器在每次时钟触发沿到来之前的状态称为初态,之后的状态称为次态。所谓触发器的逻辑功能,是指以输入信号和现态为变量,以次态为函数的逻辑关系,可以用特性表、特性方程或状态图来描述这种关系。按照触发器的逻辑功能,通常分为D触发器、JK触发器、T触发器和SR触发器等几种不同类型。

逻辑功能和电路结构是两个不同的概念。某一种逻辑功能的触发器可以用不同的电路结构来实现,同时,以某一种基本电路结构为基础,也可以构成不同逻辑功能的触发器。

①D触发器

D触发器的下一状态与输入端D相同,而与上一状态无关。

②JK触发器

在所有逻辑类型的触发器中,JK触发器具有最强的逻辑功能,在外部J、K信号控制下,它能执行保持、置0、置1和翻转四种操作,并可用简单的附加电路转换为其他功能的触发器。

③T触发器

在某些应用中,需要对一些技术功能进行控制:当控制信号T=1时,每来一个CP脉冲(时钟周期),它的状态翻转一次;而当T=0时,则不对CP信号做出相应而保持状态不变。

④T’触发器

当T触发器的T输入端固定接高电平时(即T=1),则时钟脉冲每作用一次,触发器就翻转一次。这种特定的T触发器常在集成电路内部逻辑图中出现,其输入只有时钟信号,有时称为T’触发器。

⑤SR触发器

仅有置位、复位功能的触发器称为SR触发器。S=R=1时,触发器的次态是不能确定的,如果出现这种情况,触发器将失去控制,因此,SR触发器的使用必须遵循SR=0的约束条件。

四、用Verilog描述锁存器和触发器

在Verilog中,将逻辑电平中的敏感事件分为两种类型:电平敏感事件和边沿触发事件。①在组合电路中,输入信号的变化直接会导致输出信号的变化;②时序电路中的锁存器输出在使能信号为高电平时亦随输入电平而变化。

①组合逻辑电路:

always @(*) //或

always @(D,S) //其中D、S为信号

- 1

- 2

②时序电路:

always @(posedge clk or negedge rstn) //其中clk为时钟信号,rstn是复位信号

- 1

在IEEE 1364-1995标准中,要求多个事件之间用关键字 or 进行连接,修改后的标准可以用逗号隔开多个异步事件。

1. D锁存器行为级描述

对于D锁存器来说,当输入控制信号处于有效电平时(即E=1),其输出Q跟随输入信号D的变化;当控制信号无效时,输出Q保持不变。

module D_latch (

input D ,//端口声明,输入信号

input E ,//控制信号

output reg Q ,

output QN

);

assign QN = ~Q;

always @(E or D) begin

if(E)

Q <= D;

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

2. 基本D触发器行为级描述

在时钟信号上升沿时,将输入信号D的值赋给Q,而在其它任何时间,无论D信号如何变化,都不能改变Q的状态。

module DFF (

input clk ,//系统时钟

input D ,//输入信号

output reg Q //输出信号

);

always @(posedge clk) begin

Q <= D;

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

3. JK触发器行为级描述

根据JK触发器的特性表,使用case语句进行描述。将输入变量J、K拼接起来成为一个二进制变量({J,K})。

module JK_FF ( input clk , input J,K , output QN , output reg Q ); assign QN = ~Q; always @(negedge clk) begin case ({J,K}) 2'b00:Q <= Q; //状态保持不变 2'b01:Q <= 1'b0; //置0 2'b10:Q <= 1'b1; //置1 2'b11:Q <= ~Q; //翻转 default: ; endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

参考

数字电子技术基础5——锁存器与触发器相当于把数电书上这一节的内容都给“搬运”过来了,虽然这里面有一些图的缺损,不过还是相当棒的。

数电基础(5)–锁存器和触发器有点像是数电老师上课讲的PPT,来讲这一整章的内容。

锁存器和触发器的区别是一个大佬总结性的写的区别,很简单但很精髓,其中附有用Verilog写D触发器、T触发器、JK触发器的教程。

数字电路中D触发器和D锁存器分别有什么作用?用6种方法,分别是功能的文字叙述、功能表、状态转移真值表、特征方程、状态图、时序图总结性的介绍了D触发器和D锁存器。