热门标签

热门文章

- 1OpenHarmony网络组件-Mars

- 2navicate 连接虚拟机的mysql_navicat连接虚拟机mysql

- 320240407 每日AI必读资讯_octopus v2

- 4今天聊聊基于知识增强预训练技术ERNIE_预训练模型知识增强技术有哪些

- 5单片机采集的MPU6050原始数据对应关系

- 6企业老员工管理最有效的七个办法_管理学案例老员工

- 7lifecycleScope Unresolved reference_lifecyclescope.launch找不到

- 8大厂字节程序员薪资曝光:排行世界第五厉害了_大厂程序员年薪排名

- 9数字图像处理入门-邻域、连通性、通路和距离_数图路径的长度

- 10【Android Studio】Gradle版本 Gradle 插件 版本 Java版本 Androd studio版本统一问题_the specified gradle distribution

当前位置: article > 正文

国产安路FPGA(二)-TD软件仿真(Modelsim)_安路 mult

作者:小小林熬夜学编程 | 2024-04-15 18:23:18

赞

踩

安路 mult

使用ModelSim进行国产FPGA的功能型仿真

一、设计概述

本次仅进行FPGA部分的功能仿真,ModelSim的版本为ModelSim SE-64 10.5

工程描述:有符号数据的乘法运算,使用TD原语操作,芯片采用PH1系列芯片。

二、工程代码

设计代码:

module Signed_test( input clk, input rst_n, input signed[7:0] a, input signed[7:0] b, output reg signed[15:0] out ); //寄存器 寄存有符号数据 reg signed [7:0] a_reg; reg signed [7:0] b_reg; wire signed [15:0] mult_out; //assign mult_out = a_reg * b_reg; always @(posedge clk) begin a_reg <= a; b_reg <= b; out <= mult_out; end PH1_LOGIC_MULT#( .INPUT_WIDTH_A(8), .INPUT_WIDTH_B(8), .OUTPUT_WIDTH(16), .INPUTFORMAT("UNSIGNED"), .INPUTREGA("DISABLE"), .INPUTREGB("DISABLE"), .OUTPUTREG("DISABLE"), .SRMODE("ASYNC"), .IMPLEMENT("AUTO") ) red_dap_mult( .p(mult_out), .a(a_reg), .b(b_reg), .cea(1'd1), .ceb(1'd1), .cepd(1'd1), .clk(clk), .rstan(rst_n), .rstbn(rst_n), .rstpdn(rst_n) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

仿真代码:

`timescale 1ns/1ns module Sim_mult; reg clk; reg rst_n; reg signed[7:0] a; reg signed[7:0] b; wire signed[15:0] out; always #10 clk = ~clk; initial begin clk = 0; rst_n = 0; a = 8'd0; b = 8'd0; #20 rst_n = 1; a = -13;//1000_1101 b = -5;//1000_0101 #40 a = 10; b = -10; end Signed_test Signed_test( .clk(clk), .rst_n(rst_n), .a(a), .b(b), .out(out) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

三、ModelSim仿真(重点)

1. 环境配置

(1)仿真模型复制

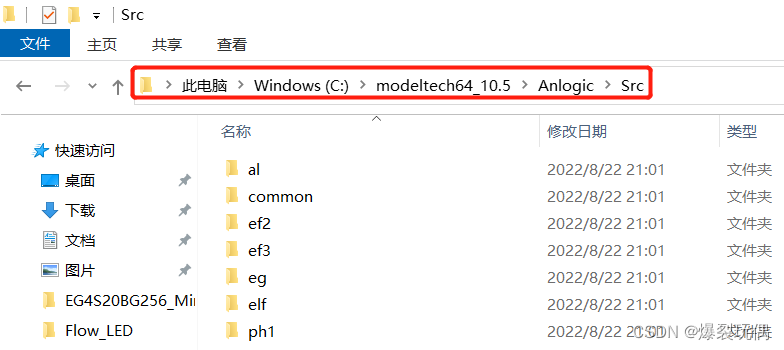

首先需要在ModelSim安装目录下新建一个Anlogic的文件夹,用以存放安路仿真的文件,然后需要新建一个Src文件夹,将TD软件安装路径中的sim_release中所有器件的仿真模型复制到Src文件夹中。

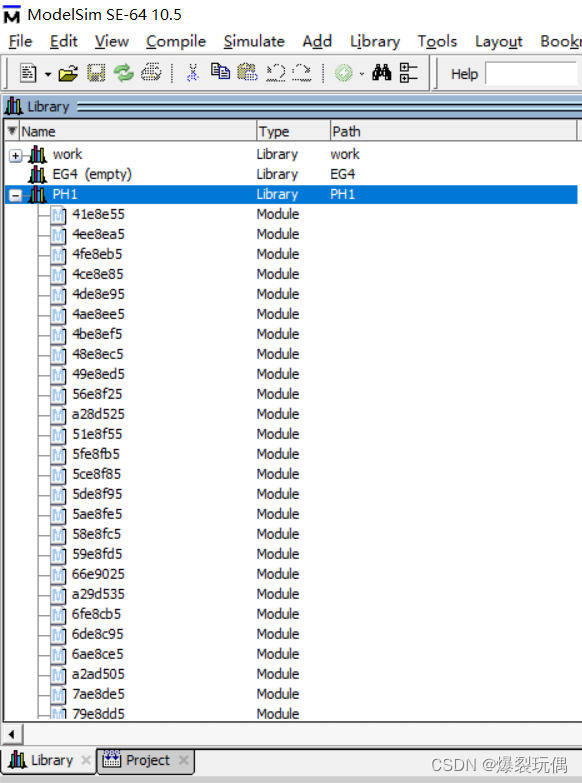

(2)新建Library,建立相对应芯片的仿真库,并添加

点击File——New——Library,并命名该仿真库,点击OK。

点击Compile——Compile,然后选择ModelSim安装目录下,Src文件夹下的PH1中所有的文件。添加完成后如图:

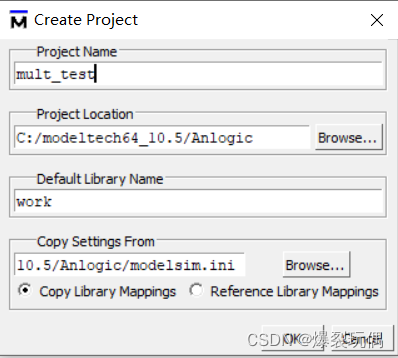

(3)新建仿真工程,建立相对应芯片的仿真库,并添加设计和仿真文件

点击File——New——Project,并命名该工程,点击OK。

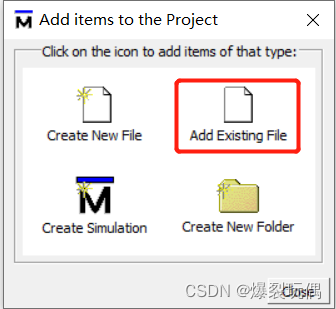

点击ADD Existing File添加设计工程文件.V和仿真设计文件.V。(`提示: 这里的两个.V文件是工程中的文件,可以进行直接添加,并且在文件修改过程中,该部分的添加文件也将自动进行修改)。

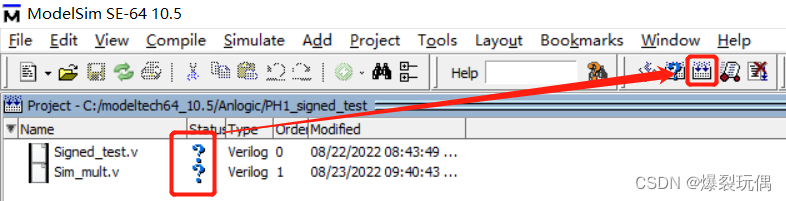

添加完成后,该部分将会显示待测文件,且都是未检测状态,所以需要点击Compile All将所有文件进行检查。

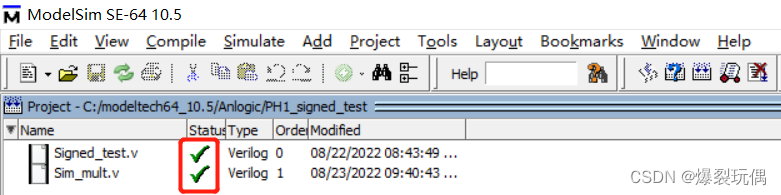

检验完成后的状态如图

(4)开始仿真

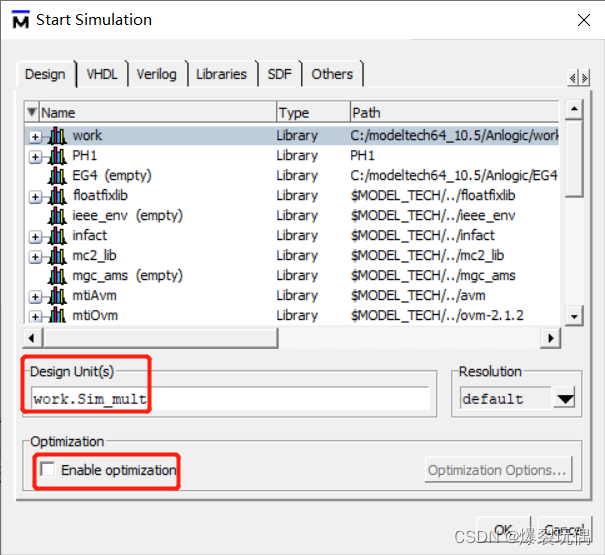

点击Simulate——Start Simulation,由于前面是在work下进行的仿真工程文件的添加,所以在work下寻找仿真文件,(`提示: 这里的Optimization中的勾选一定要勾选掉,否则将会有信号会被综合掉导致无法输出)。

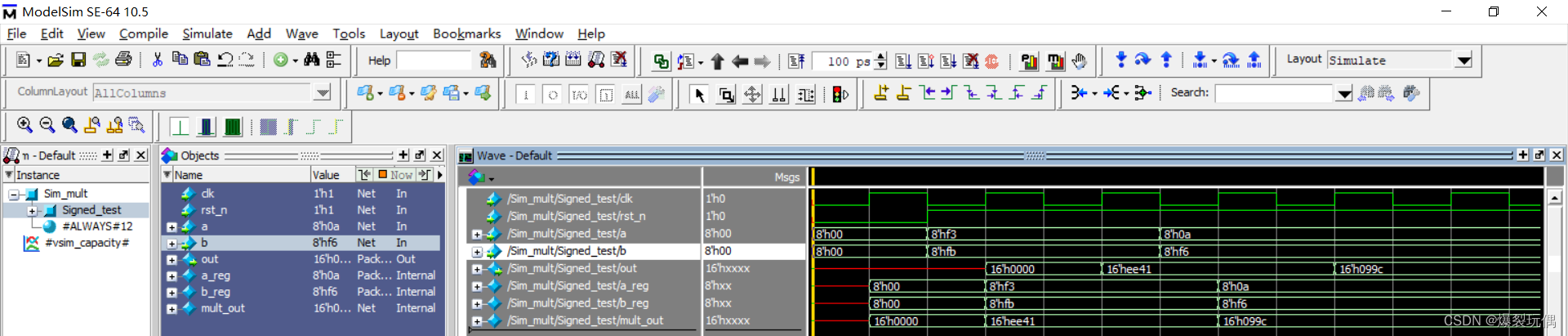

(5)完成仿真

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小小林熬夜学编程/article/detail/429384

推荐阅读

相关标签