- 1Paxos算法和ZooKeeper使用的Zab(ZooKeeper Atomic Broadcast)算法

- 2山东供销合作社发展的实施意见 国研政情·谋定论道-经济信息智库

- 3使用 Meltano 将数据从 Snowflake 导入到 Elasticsearch:开发者之旅

- 4【C语言实现贪吃蛇】(内含源码)

- 5[计算机视觉DL学习] 迁移学习 风格迁移基础学习_使用预训练模型 计算两张图片的风格损失

- 6使用PyTorch进行中文文本分类:一个深度学习实践项目

- 7关于undefined method `each‘ for nil:NilClass的报错

- 8GPT-4完全破解版:用最新官方API微调,想干啥就干啥,网友怕了_gpi4

- 9初级开发人员的缺点_在您担任初级开发人员的第一年,获得此建议

- 10作为 IT 行业的过来人,你有什么话想对后辈说的?

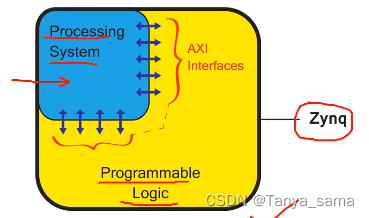

ZYNQ简介

赞

踩

1.全可编程片上系统(APSOC),本质特征:zynq组合了一个双核的ARM Cortex-A9的处理器和一个传统的现场可编程逻辑门阵列(FPGA)逻辑部件。

2.PL简介:可以等价一个FPGA。

先引入PLD, PLD:早期数字集成电路逻辑功能固定,要想改变它的逻辑功能,就必须改变内部各单元电路之间的连接,而连接在集成电路制作过程中已经固定下来了。

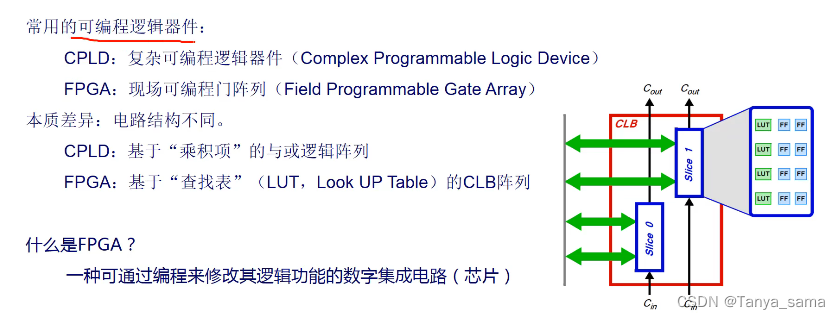

FPGA:基于“查找表(LUT,Look UP Table)”的CLB阵列,是一种可通过编程来修改其逻辑功能的数字集成电路(芯片),是对硬件进行编程。

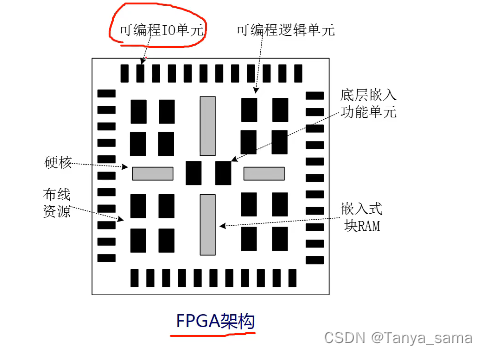

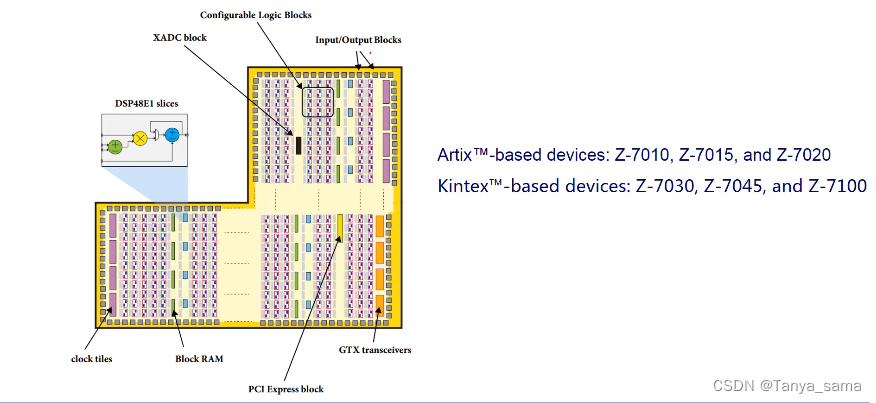

FPGA架构:

硬核:不是所有FPGA都有。

(XADC:数模转换模块)

PS简介 :

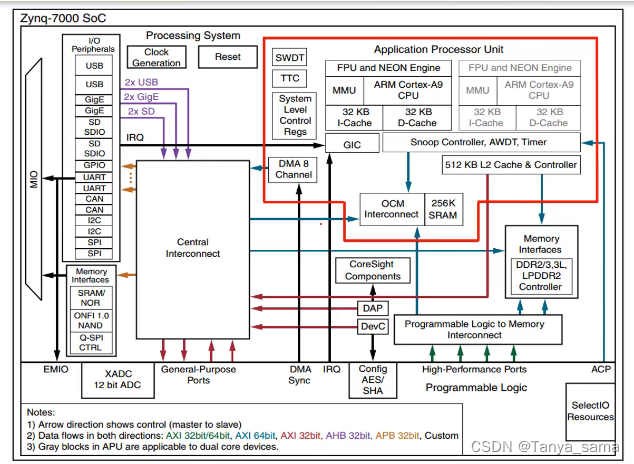

PS架构图:

红色区域APU

FPU (浮点计算有关) NENO Engine(做一些需要并行运算的计算) MMU(存储管理单元,物理地址与虚拟地址的映射) I-Cache + D-Cache (一级缓存)

| FPU (浮点计算有关) | NENO Engine(做一些需要并行运算的计算) |

| MMU(存储管理单元,物理地址与虚拟地址的映射) | I-Cache + D-Cache (一级缓存) |

| L2 Cache(两个处理器共用的) | OCM(片上处理器) |

| GIC(中断控制器) |

APU部分

Central Interconnect (中央互联),可以实现不同模块或者接口的通信。

EMIO(PS端,可做扩展,可以接到PL端的I/O)

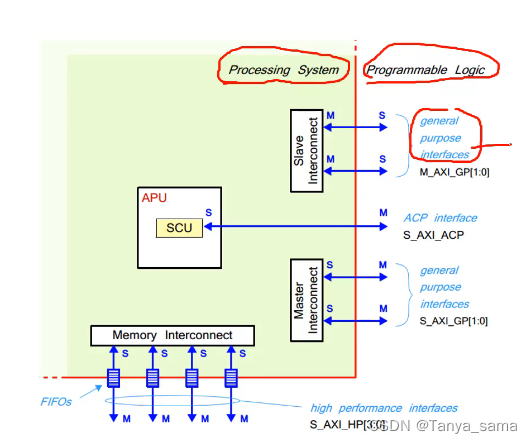

AXI interface:

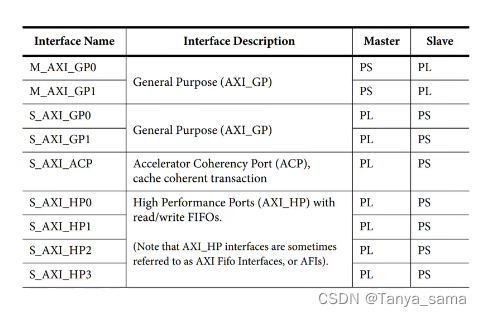

M_开头表示主接口,S_表示从接口;但是针对对象都为PS,例如以M_开头表示PS做主机,PL部分作从机;S_表示PS做从机,PL部分作从机。

S_AXI_HP(高性能接口,性能相对GP接口来说,每个接口的FIFO可以实现数据的缓冲,可以实现一个高带宽的一个数据访问,或比较大的一个数据量,同时这个接口PS作从机,PL作主机使用)

AXI简介:

AXI is Part of ARM's AMBA

AXI_4 Memory Map :存储映射,如果一个读写访问,在给出读写访问请求的时候,同时给出一个地址,这种访问称之为一个存储映射的访问。(可以做一些中低速的存储访问)

AXI_Stream :用来传输大量的数据流,只给出数据,并不给出相应的地址。

AXI_Lite :轻量级的一个接口,相当于AXI_4 Memory Map的一个简化版,简化体现在不支持突发传输,(可用于做一些简单寄存器的配置)