- 1毕业设计项目 基于大数据的招聘职业爬取与分析可视化

- 2确保未来安全:应对云安全的复杂性

- 3NLP必读经典-语料语言学-NLP方法学入门-最新

- 4自学也能学得会的《零基础入门学习Web开发》(HTML5 & CSS3)_零基础入门学习web开发pdf

- 5【PyTorch学习】PyTorch基础知识_pytorch2.1.2 是个啥

- 6CVPR2022 | ZeroCap:零样本图像到文本生成的视觉语义算法_zero-shot image-to-text generation for visual-sema

- 7如何导出自己Django项目所需要的包_pycharm中django项目怎么导出

- 8数据处理——SnowNLP计算文本情感值_snownlp库进行情感分析是怎么计算的

- 9mysql的去重添加ing_SQL从入门到不放弃(ing)

- 10你真的了解生成式对抗网络GAN的工作原理吗?(白话+数学公式推导)_gan的三个阶段是干嘛的

100G以太网光口的FPGA测试实例

赞

踩

100G光口测试采用C50测试仪和Xilinx的VCU118开发板测试,经过测试发现,Xilinx自带的100G IP核仍然无法跑到满速,跟10G一样,也是只跑到99%的负载率。另外,工具的版本和License的申请都需要特别留意。欢迎感兴趣的同学们留言讨论。

一、软硬件环境、IP核及对应License

1、软硬件环境

软件环境为VIVADO2019.1,不建议采用VIVADO 2018.2,原因在于2018.2中的该IP核没有AXI总线,只有LBUS总线,LBUS总线使用起来需要进行总线的聚合与分拆(数据总线分为4路,每路位宽为128bit),较为繁琐,所以建议使用2019.1中的AXI总线的IP核。

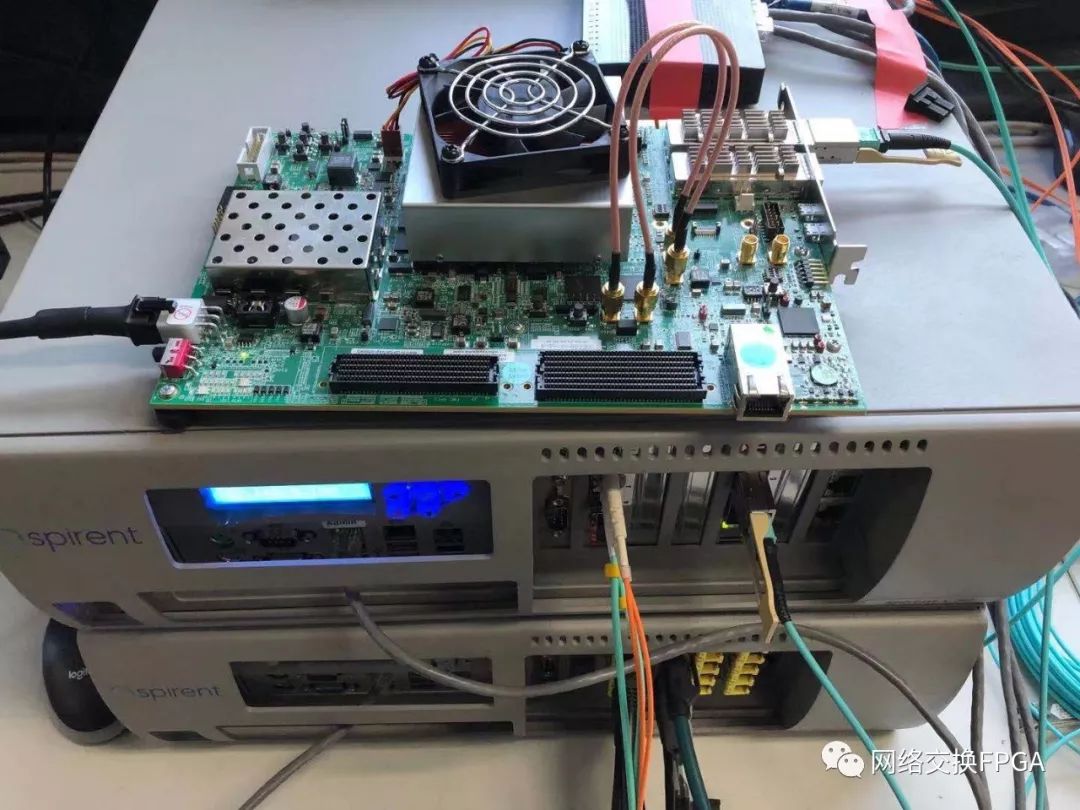

硬件环境为采用TestCenter C50测试仪的100G光口连接VCU118开发板上的100G光口进行测试。

连接图(必须用100G专用光纤)

VCU118开发板

C50网络分析仪(两个100G光口、4个五速光口(40G、20G和十百千)、16个十百千自适应电口)

2、100G IP核

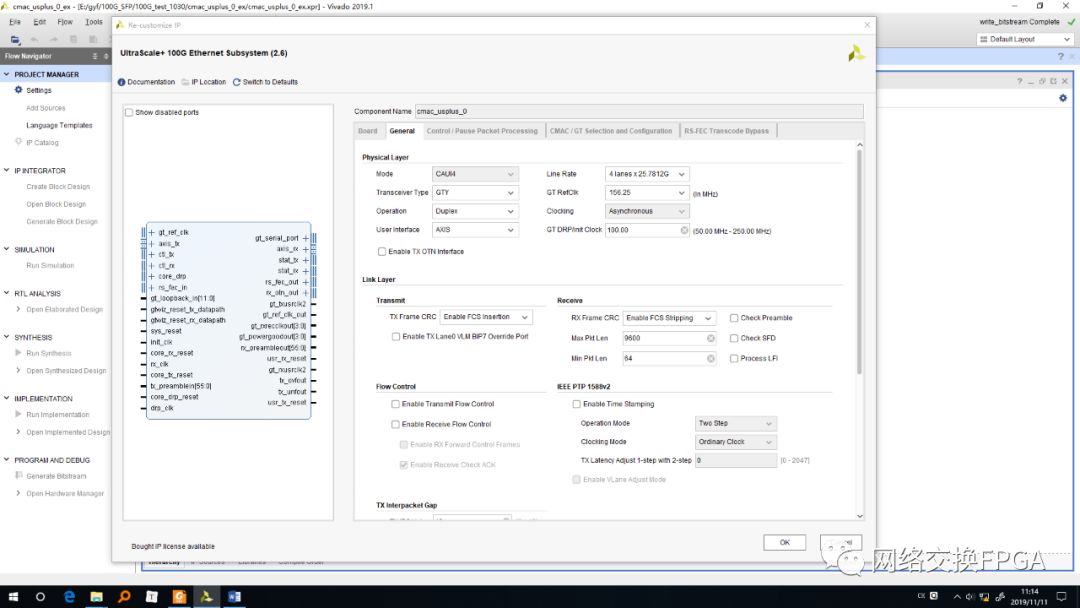

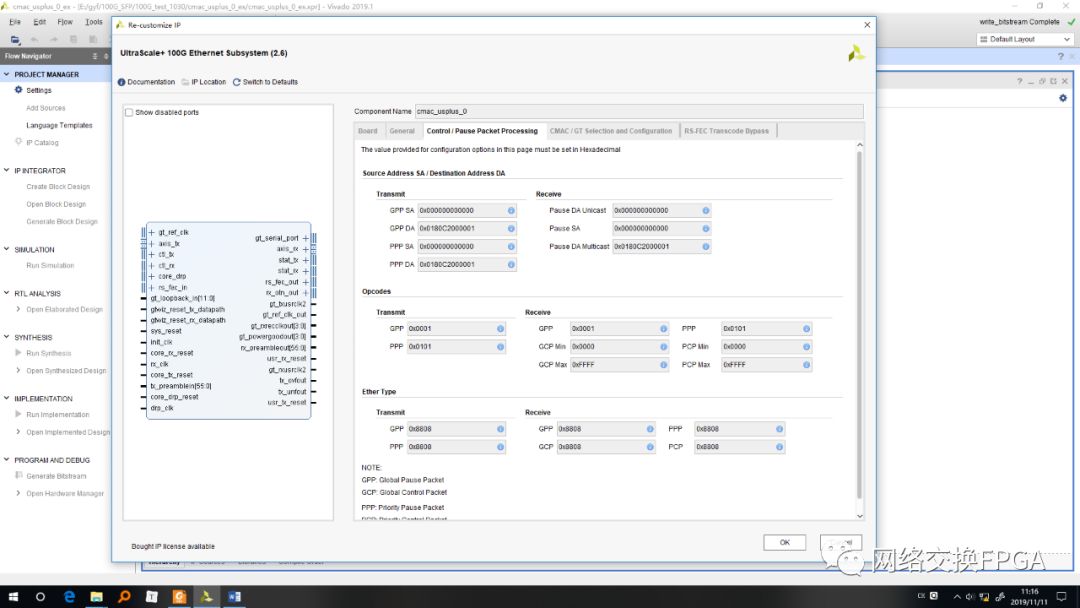

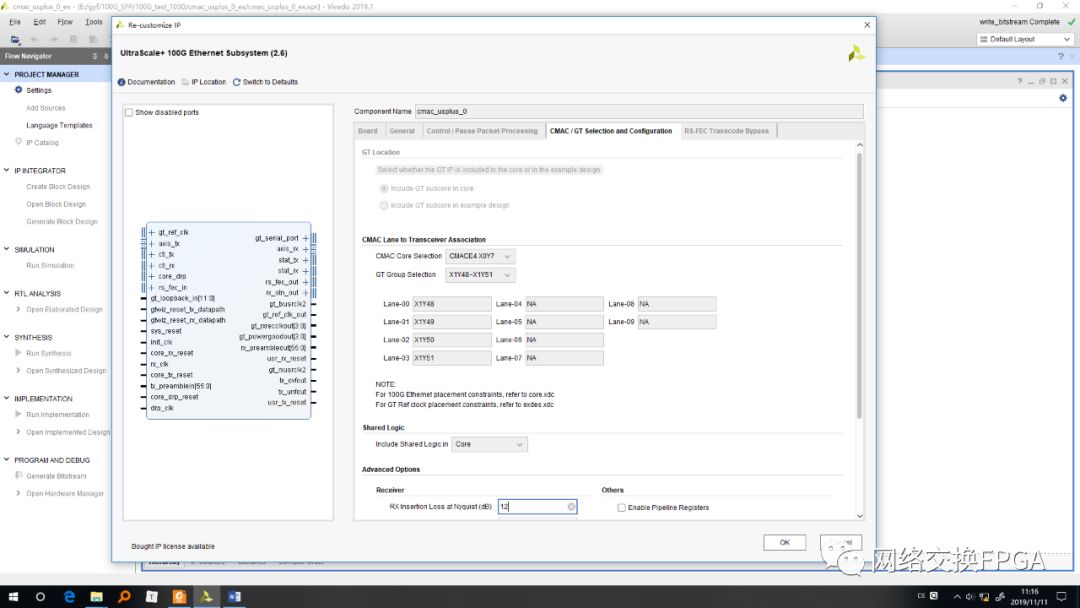

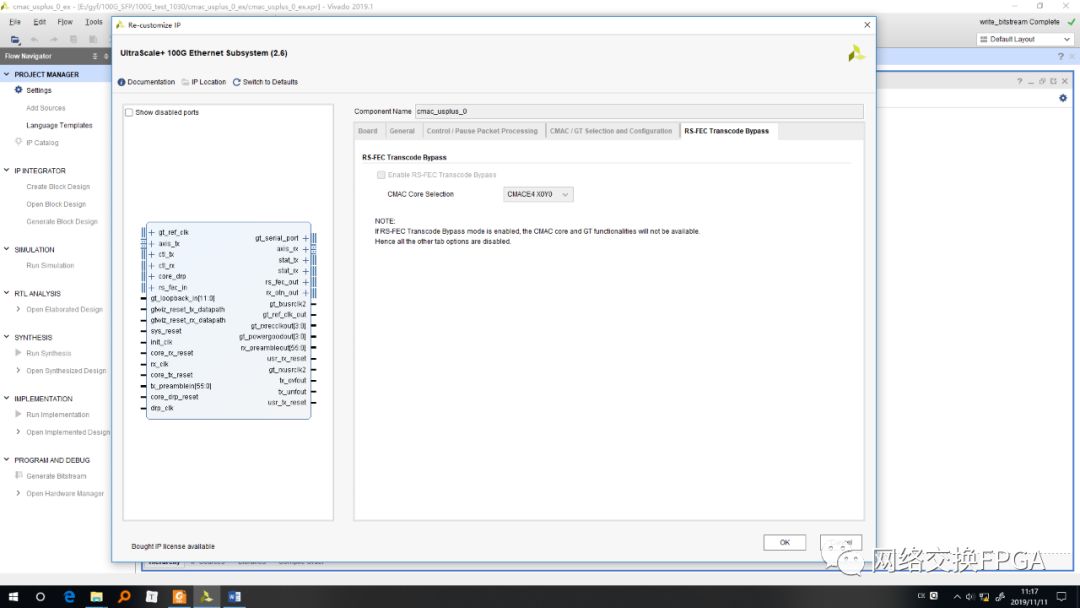

所使用的IP核是UltraScale+ 100G Ethernet subsystem。IP核配置界面如下图所示:

因环境选择的是Xilinx官方开发板,所以此处可以进行选择,参考时钟为全是qsfp1 si570 clock。

选择四通道(CAUI4),线速率默认为4lanes * 25.7812G,GTY参考时钟频率为156.25Mhz(VCU118开发板给出)。发送与接收CRC校验默认开启。

使用前向纠错码(RS-FEC),不开启自适应选项(Auto Negotiation)。若FEC不开启,开发板与网络测试仪无法建立连接;若开启自适应选项,IP核的bit文件无法生成(猜测与VIVADO的Licese文件有关)。

其余选项皆为默认配置,没有进行修改。具体配置如上图所示。3.License文件

License文件主要影响该IP核bit文件的生成,可以在Xilinx官网申请试用版License,但是License的试用期只有一年,而且在申请的时候会绑定申请主机的MAC地址,所以换到其他主机设备时无法使用,需要另外申请License文件。

二、100G工程组成及参数配置

1.工程组成

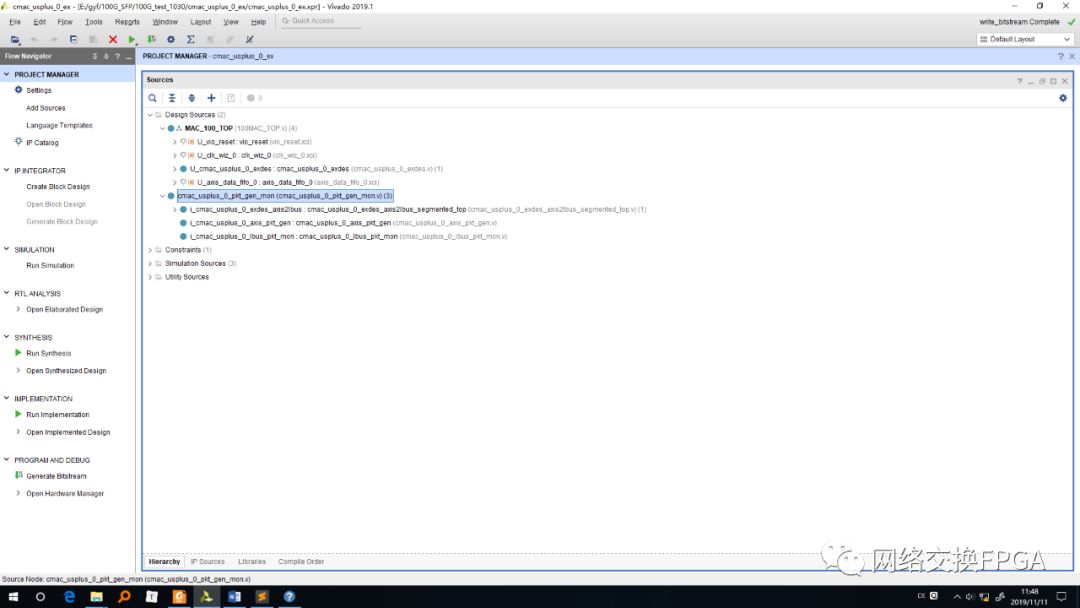

由上文所述的IP核生成example design文件,删去工程中的cmac_usplus_0_pkt_gen_mon模块。(此模块用于生成用户侧数据源,并校验数据接收结果,因为需要使用网络测试仪进行测试,所以不需要此数据源与校验模块)

另外复位选择软复位,通过VIO来实现。时钟生成模块产生IP核所需要的时钟。

为了稳定用户侧数据,在IP核后接一个FIFO,先对用户侧接收到的数据进行缓存处理,然后将数据发往发送端。FIFO的配置如下图所示:

2.参数配置

LBUS总线控制信号(信号具体解释可以参考pg203中表2-6和表2-7)。主要是使能信号(ctrl_rx_enable和ctrl_tx_enable)要赋值为1。

三、测试结果

速率配置为99G(同10G接口一样,配置为100%时会有丢帧产生),帧长为随机帧长(64~1518)。丢帧问题与10G光口测试时的现象一致(详见本公众号之前文章:10G 以太网接口的FPGA实现,你需要的都在这里了),可能是Xilinx的IP核保护吧,也许你花钱购买后就可以跑到满速了。

测试结果如下图所示,帧计数与字节计数均一致,且未出现丢帧与错帧,说明工程工作正常,可以完成数据的收发。

全文完。

基于FPGA的网口通信设计

媒体访问控制(MAC,Media Access Control)

媒体独立接口(MII,Meida Independent Interface)