热门标签

热门文章

- 1一文全面了解word2vec(CBOW、Skip-Gram、层序softmax、负采样)_层序softmax应用连续词袋

- 2<Rust><iced>在iced中显示gif动态图片的一种方法

- 3Python 利用pickle库查看pkl文件实例演示,pkl是什么类型的文件?怎么来打开它?_pkl文件怎么打开

- 4pg 出现视图依赖表,导致字段不能修改_cannot alter type of a column used by a view or ru

- 5基于Java+MySQL+Tomcat+maven+JavaScript+Servlet的个人博客系统_java写博客

- 6Mac M1 安装 iTerm2+Oh My Zsh+zsh-syntax-highlighting 真香!_mac m1配置iterm2

- 7PyTorch实现DCGAN(生成对抗网络)生成新的假名人照片实战(附源码和数据集)_pytorch生成一个假脸模型

- 8AI开源概览及工具使用_开源ai

- 9nodejs中的require,exports使用说明

- 10Redis持久化之RDB_redis-server.exe!rdbsavelzfstringobject

当前位置: article > 正文

前端rtl/netlist,sdc,upf进入后端,我们应该做哪些去check它的质量?_innovus check netlist

作者:小小林熬夜学编程 | 2024-06-15 13:34:43

赞

踩

innovus check netlist

netlist的检查

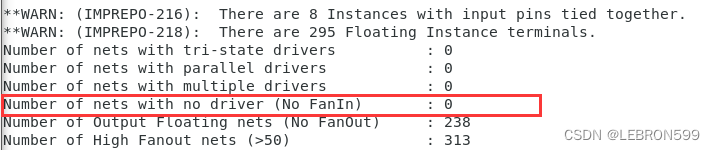

我们在innovus里面输入下面的命令来重点检查是否包含no driver的信号

checkDesign -netlist

上图中的设计不存在有net没有被驱动的情况。若存在,则此时必须反馈给前端,因为这种错误属于设计上的错误。后端做后续的DRC检查以及formal检查都是无法通过的。

时序约束SDC检查

sdc首先检查是否有语法错误,确保每条sdc约束命令都成功读入。然后做以下几方面的检查。

1.时钟周期检查

这里主要检查前端逻辑综合使用的周期是否正确,以及确保我们PR阶段使用的周期是正确的,避免过渡优化或者优化不到位的情况。

2.ideal network检查

需要把除时钟信号外其他的ideal network属性移除掉,否则后续工具做优化时无法解high fanout net。

3.clock uncertainty检查

clock uncertainty是给设计预留margin的一个手段。这个值留的越大timing就越紧张。设置的过大,可能出现overdesign的情况,设置太小会出现优化不到位的情况。最终在PT的timing signoff检查中可能会有timing violation。

4.input/output delay约束值检查

input和output delay的值会影响到模块接口相关的data path优化。对于hierarchical flow的同步设计来说,要格外注意这方面的接口时序。

一般来说input和output d

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小小林熬夜学编程/article/detail/722517

推荐阅读

相关标签