- 1MySQL — InnoDB引擎、MySQL架构、事务原理、MVCC_mysql innodb事务

- 2云原生第3课:Kubernetes 系统快速入门

- 3牛客网专项练习(一)——20道选择题_牛客网-专项练习模块选择自己考试技能

- 4推荐开源项目:FreeCAD中的计算流体动力学(CFD)模块

- 5【实战】学习 Electron:构建跨平台桌面应用_electron桌面开发

- 6迭代器设计模式_迭代器模式

- 7使用HtmlAgilityPack批量抓取网页数据_htmlagility 遍历网络链接

- 82020 大厂研发岗薪酬排名出炉,看完我真的拖后腿了。。。

- 9windows10系统安装docker desktop超常见问题_windows desktop安装提示无法连接domain

- 10推荐必读书籍整理集合_查尔斯·哈奈尔写的所有书

FPGA RTL_fpga中rtl是什么

赞

踩

RTL在电子科学中指的是寄存器转换级电路(Register Transfer Level)的缩写,也叫暂存器转移层次。FPGA设计可以包括为RTC模块设计与组合模块设计,RTL模块又是FPGA设计中的主要难题。分享一下在学习过程中的心得体会。

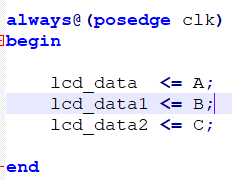

我学了有一段时间的FPGA,刚开始我只知道RTL模块是与时间有关,表面理解为里面的赋值符号要用(<=),而组合逻辑里面的赋值符号要用(=),这是我对FPGA这两大模块的初步影响,并不理解这是什么意思(更不理解教科书上的什么阻塞,很让人头痛),后来随着学习的深入,要真正理解FPGA,还是要从电路上去理解,电路是每时每刻都在通电,那么RTL模块中的(<=),是同时执行的如下:

上段代码的意思是A,B,C在检测到高电平clk时,分别同时赋值给lcd_data、lcd_data1、lcd_data2,这就是所谓的非阻塞,意识就是同时执行;

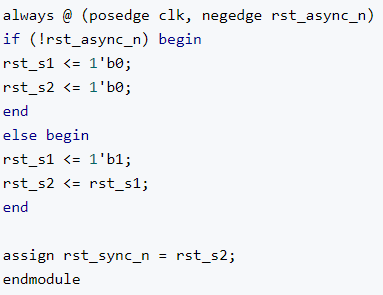

通过这个我们可以去了解同步复位,异步释放:

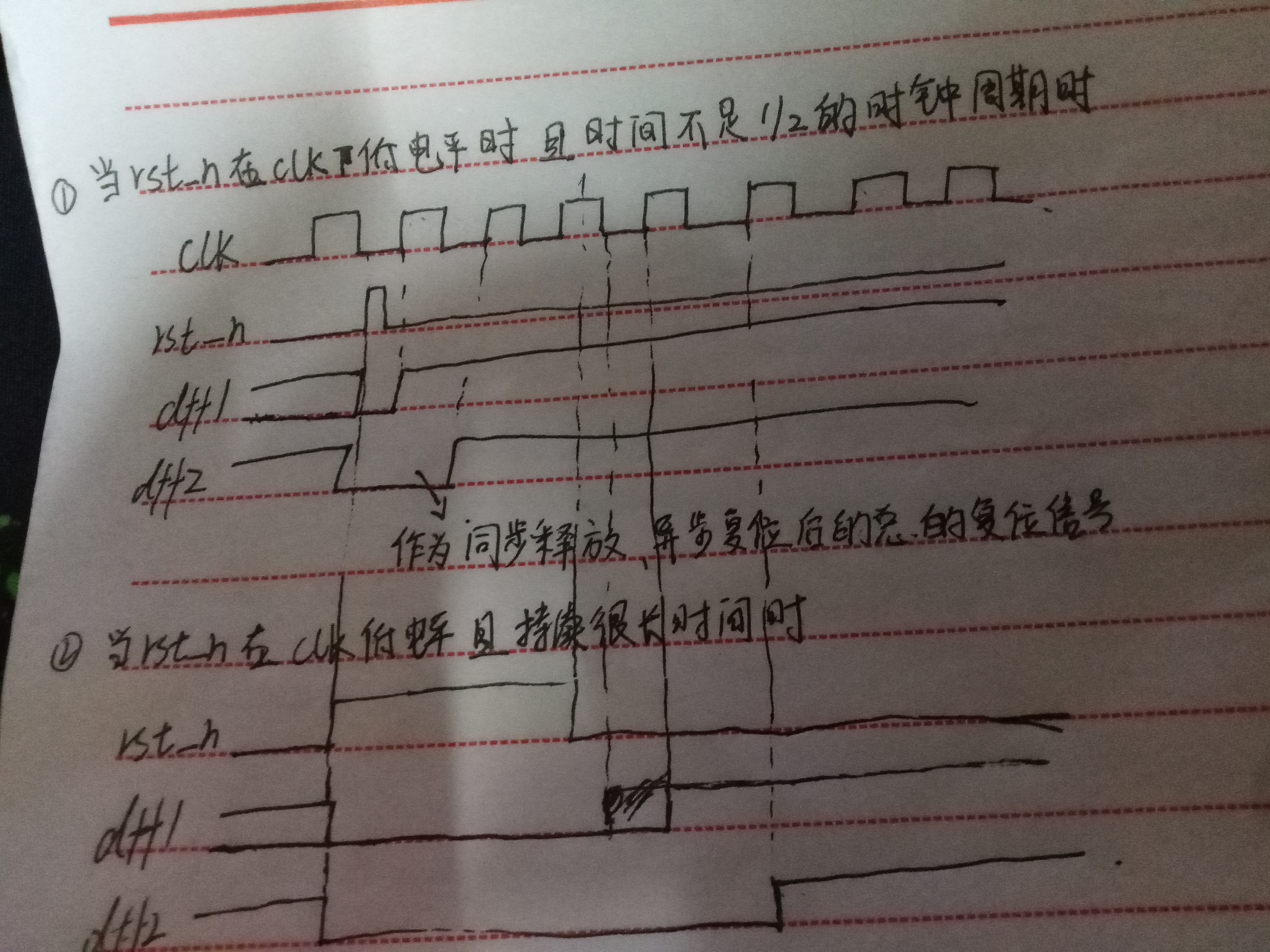

同步复位的缺点是在没在时钟上升沿的时候不能成功复位,而异步复位的缺点是假如持续时间比较短,会产生亚稳态(与D触发器的性质有关,D触发器需满足复位时间才能正常复位。)(说实话,我在没学数字电路之前,完全不能理解同步复位,异步释放)。

而同步复位,异步释放是什么意思呢?异步复位信号在触发的时候,不是立即复位而是等待时钟信号,在下一个下降沿的时候再释放(这样就可以延长持续时间,减少亚稳态的产生)。

所谓的亚稳态:我们大部分芯片在初始化的过程中,都需要一个setup time+hold time的响应去激发它去正常工作,假如我们没有响应那么长时间,那么它就会不知所措,不知道该发送什么数据、还是不发送数据,这就它的亚稳态。我们的D触发器也一样,我们在发送复位信号的时候,假如复位信号响应时间不够长。那么也会不知所措。

上段代码同步复位,异步释放,是兼顾异步复位与同步复位的优点,在非总线的时序设计中常常被使用。

通过这段代码来进一步去了解非阻塞语言:在检测到低电平复位信号的时候,rst_r1与rst_r2分别同时赋值为1'b0、1'b0;在检测到高电平时钟信号的时候rst_r1与rst_r2分别同时赋值为1'b1、rst_r1;

那这段代码为什么可以实现同步复位,异步释放呢?

这是根据异步复位、同步释放这段代码所得的时序图;我们不难发现在dff(D触发器)2,在复位信号出现的时候立即复位(即异步复位)、但是延时了两个时钟周期,dff2才释放(即同步释放)。然后dff2作为新的复位信号,增长了复位信号的时间,减小了复位信号在由于复位时间短可能产生的亚稳态出现的概率。