- 1Springboot教程(二)——过滤器、拦截器_springboot 中使用过滤器 拦截器

- 2WatchAD内网安全态势感知系统搭建_watchad2.0

- 3centos7离线升级gcc8.0_centos7 升级gcc8

- 4优化工具包—无约束非线性优化求解器(fminsearch)_fminsearch函数

- 5网络药理学的操作方法(以中药为例)·1_网络药理学具体步骤

- 6软件测试/测试管理|构建成功的团队成长规划_软件测试团队可设定的目标

- 7SupSLAM:使用SuperPoint用于无人机的鲁棒视觉惯性 SLAM 系统

- 8Futter 更改已有项目的名称和id_flutter 修改项目名字

- 9CTFshow刷题日记-WEB-SSTI(web361-372)_ctfshow ssti 371

- 10Mac技巧之查看苹果电脑 Mac OS X 系统是否开启 64 位运算,以及设置 32/64 位模式的方法_mac64位改32位

手把手教你玩转AD9361数字调制解调系列(三) ----纯PL逻辑实现FM信号的数字调制解调_ad9361配置 纯pl

赞

踩

因最近客户需求,用纯PL实现AD9361的数字信号调制解调,于是就把各种数字调制都在AD9361上都实现了一遍。

优点就是:既可以在zynq系列上配置9361,也可以在纯FPGA系列配置9361。并且理解起来比较简单!!!

制作不易,记得三连哦,给我动力,持续更新中!!!

完整工程文件下载:纯逻辑设计AD9361发射FM工程下载 (点击蓝色文字即可下载)

提取码:19w5

对于之前学习过我文章的小伙伴来说,大家应该都了解如何利用 AD936x Evaluation Software 生成 AD9361 的配置,并在 Vivado 中调用该配置,最后写入 AD9361 芯片。

对于新来的小伙伴而言,我建议你可以先回顾一下我之前的文章内容。在那些文章中,我详细介绍了如何通过软件生成 AD9361 的配置,并在 Vivado 开发环境中使用该配置。这些基础知识对于接下来的内容学习很重要。

在接下来的设计中,我们将在纯逻辑配置 AD9361 的基础上,实现各种数字信号的调制解调功能。这将涉及更多的数字信号处理知识和技术。如果你对这些内容感兴趣,不妨继续关注我的后续文章。我会在这些文章中, 全面地讲解如何基于 AD9361 实现各种数字调制解调功能的具体实现方法。

纯逻辑配置AD9361教程/通过UART串口发送配置文件配置AD9361/通过rom配置AD9361/纯PL配置AD9361_ad9361发送数据代码-CSDN博客

本篇文章将介绍如何通过AD9361发射FM信号以及纯verilog代码实现和讲解。

一、FM原理

基于 FPGA 和 AD9361 实现 FM 数字调制与解调的原理如下:

-

FM 数字调制:

- 利用 FPGA 逻辑电路生成正弦波载波信号。

- 根据输入的数字信号,动态调整载波信号的频率。这就实现了FM调制。

- 将调制后的信号输入到 AD9361 的 TX 端,进行模拟上变频和放大.

-

FM 数字解调:

- AD9361 的 RX 端接收 FM 调制信号,完成下变频和数字化。

- FPGA 接收 AD9361 输出的数字 FM 信号,采用频率判决或相位锁定环等方式实现FM解调。

- 从解调后的数字信号中提取出原始的输入数据。

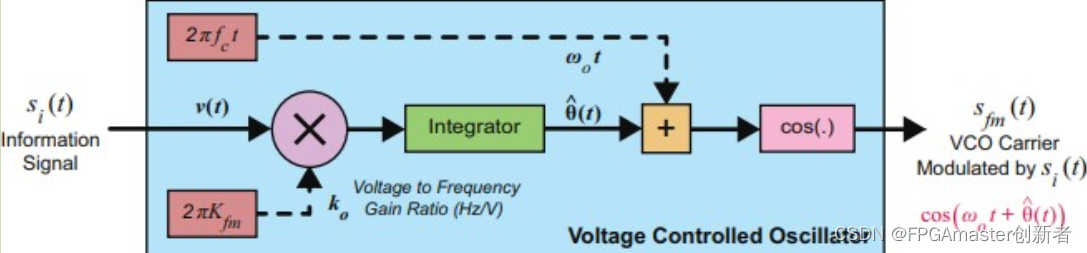

FM 就是频率调制,就是使用载波的频率来承载消息信号,当消息信号的幅值较大的时候,产生的频率比较大,当消息信号较小时,产生的频率比较小。在我们之前介绍过的 VCO 这个结构,就是一个最简单的 FM 的调制器。

控制信号进入了 VCO 之后,首先需要乘上一个增益,这个增益表示电压(消息信号的幅值) 到频率(FM 调制的结果) 的增益值,

Copyright © 2003-2013 www.wpsshop.cn 版权所有,并保留所有权利。