- 1MS Access 教程之如何将 MDB 文件转换为 SQLite 数据库_mdb转sqlite

- 2《花雕学AI》ChatGPT Shortcut Chrome 扩展:让生产力和创造力加倍的 ChatGPT 快捷指令库

- 3用通俗易懂的方式讲解:决策树模型及案例(Python 代码)

- 4ubuntu下使用ollama来运行gemma_ubuntu ollama

- 5Bert几个数据集的概念Cola、MRPC、XNLI、MNLI等_mrpc数据集

- 6小程序实现卡片式设计(又叫原子化设计)_小程序css卡片效果

- 7【Pytorch(七)】基于 PyTorch 实现残差神经网络 ResNet_resnet18.pt

- 8【氮化镓】同质GaN垂直PiN二极管的SEB

- 9oracle镜像装载不到软盘中,Oracle ASM无法识别扩展分区的磁盘设备

- 10Bert基础(一)--自注意力机制_bert中transformer编码器

【一】DDR3基础知识与IMG IP

赞

踩

【一】DDR3基础知识与IMG IP

一、DDR3的基本知识

1、DDR3全称为第三代双倍速率同步动态随机存储器

特点:掉电无法保存数据,需要周期性的刷新;时钟上升沿和下降沿都在传输数据;突发传输,突发长度burtst length一般为8;

2、ddr3中有bank地址、行地址、列地址。数据写入ddr3需要先指定一个bank地址,再指定行地址,最后指定列地址。

3、ddr3容量的计算:bank数量×行数量×列数量×存储单元容量。举个例子:bank address位宽为3,Row address 位宽为14,column address为12,那么容量为:2^3 x 2^14 x 2^12 x 16 bit

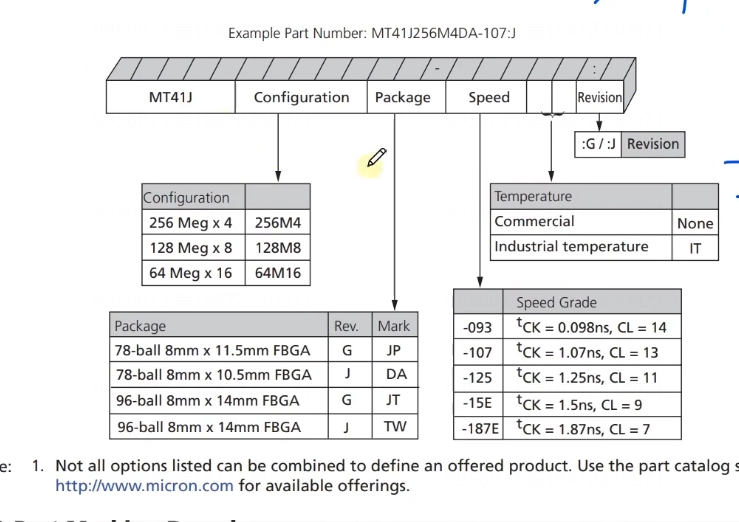

4、ddr3的命名规则:以镁光ddr3作为例子, MT41J256M4DA-107

MT41J:是代号

256M4:是配置参数。其中M4代表数据位宽为4bit。如果是M8代表数据位宽为8.

DA:封装类型

-107:是速度等级

1)ddr3支持的时钟最大的频率计算

如图速度等级为speed=-15E时,tck=1.5ns,那么支持最大的时钟频率为:1/1.5ns*1000=666.6M

speed=-125E时,tck=1.25ns,那么支持最大的时钟频率为:1/1.25ns*1000=800M

2)带宽的计算:时钟频率x数据位宽=带宽

举个例子:MT41J64M16-125,由M16可知数据位宽为16,-125为速度等级:1/1.25*1000=800M。那么带宽=16x800x2=25600M bit/s=25.6G 。其中2是因为双沿采样,上升沿和下降沿。

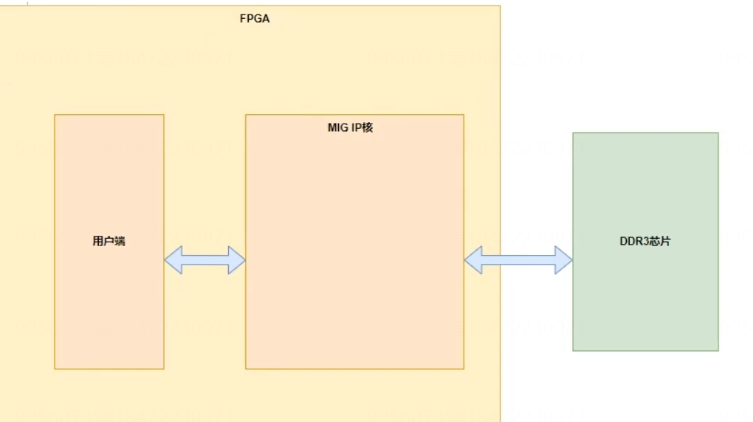

二、Vivado中 mig ip

我们只需要往mig IP写入数据就可以操作ddr3了。MIG IP有很多时钟,需要我们注意区分。

1)系统时钟sys_clk:MIG IP的输入,系统时钟频率没有要求,可以100M、1500M、200M。时钟的来源可以由fpga内部的PLL得到,也可以由外部晶振得到。

2)参考时钟ref_clk:MIG IP的输入,这个时钟频率是有要求的,建议给固定的200M。时钟的来源可以由fpga内部的PLL得到,也可以由外部晶振得到。

3)IMG IP输出一个ddr3芯片工作的时钟(差分信号P、N):这个时钟频率是多少,有两个因素

第一:取决于FPGA A7系列支持的最大时钟频率为400M,K7系列的支持800M

第二:ddr3的最大时钟频率,即根据上面速度等级如-125计算得到的最大时钟频率,如果ddr3的最大时钟频率为400m,那么IMG ip的输出时钟不能大于400M

4)用户端时钟ui_clk:MIG IP输出给用户端的

注意:ddr3的工作时钟和用户时钟ui_clk有一个比例关系,如果ddr3的工作时钟频率设置为400M,那么ui_clk有两种可能,ddr3时钟:用户时钟=2:1,则用户时钟就是200M;还有一种可能就是4:1,即 ddr3时钟:用户时钟=4:1,则用户时钟就是100M

当ddr3的工作频率>=400M时,比例只能为4:1

--晓凡 2024年3月30日于武汉书

- 1