热门标签

热门文章

- 1Android studio教程学习笔记2——线性布局LinearLayout_android linearlayout 三分 左侧压缩

- 2Git使用同一个邮箱生成同一个公钥SSH-Key并配置连接Gitee和GitHub,数次失败并尝试亲测可行!_gitee 本地公钥和knows_hosts里的不一样

- 3百度 谷歌 地图逆地址解析_谷歌地图逆地理解析

- 4[github优秀AI项目]实现4K60帧视频人体实时抠图_tensorflow实现抠图功能

- 5基于SSM实现在线考试系统_基于ssm的在线考试系统

- 6OpenHarmony开发-连接开发板调试应用_no openharmony devices

- 7多模态情感识别-MISA: baseline解读_多模态情感分析

- 8rabbitMQ配置文件

- 9windows10 装docker和docker compose_windows安装docker-compose

- 10基于YOLOv7算法的高精度实时水上漂浮物目标检测识别系统(PyTorch+Pyside6+YOLOv7)_yolo水论文

当前位置: article > 正文

Xilinx FPGA开发环境vivado使用流程_xilinx vivado

作者:小蓝xlanll | 2024-04-16 23:22:46

赞

踩

xilinx vivado

Xilinx FPGA开发环境vivado使用流程

1.启动vivado

2.选择Create New Project

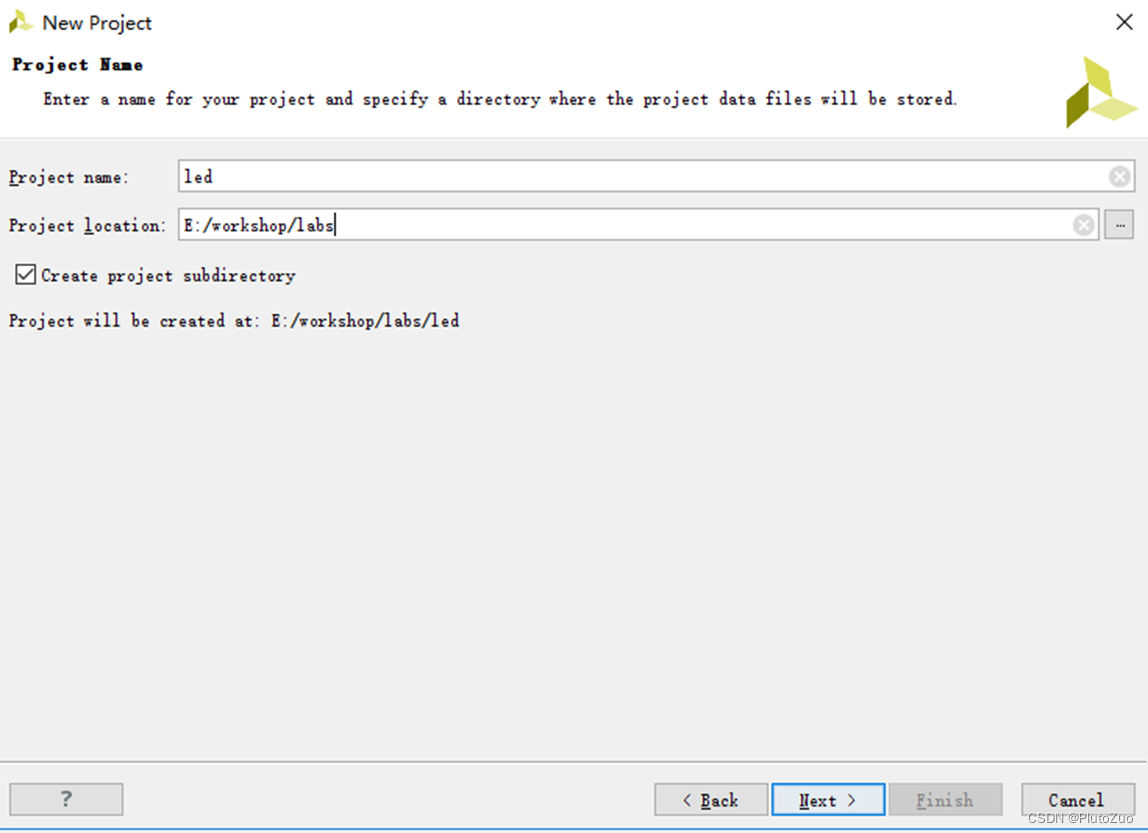

3.指定工程名字和工程存放目录

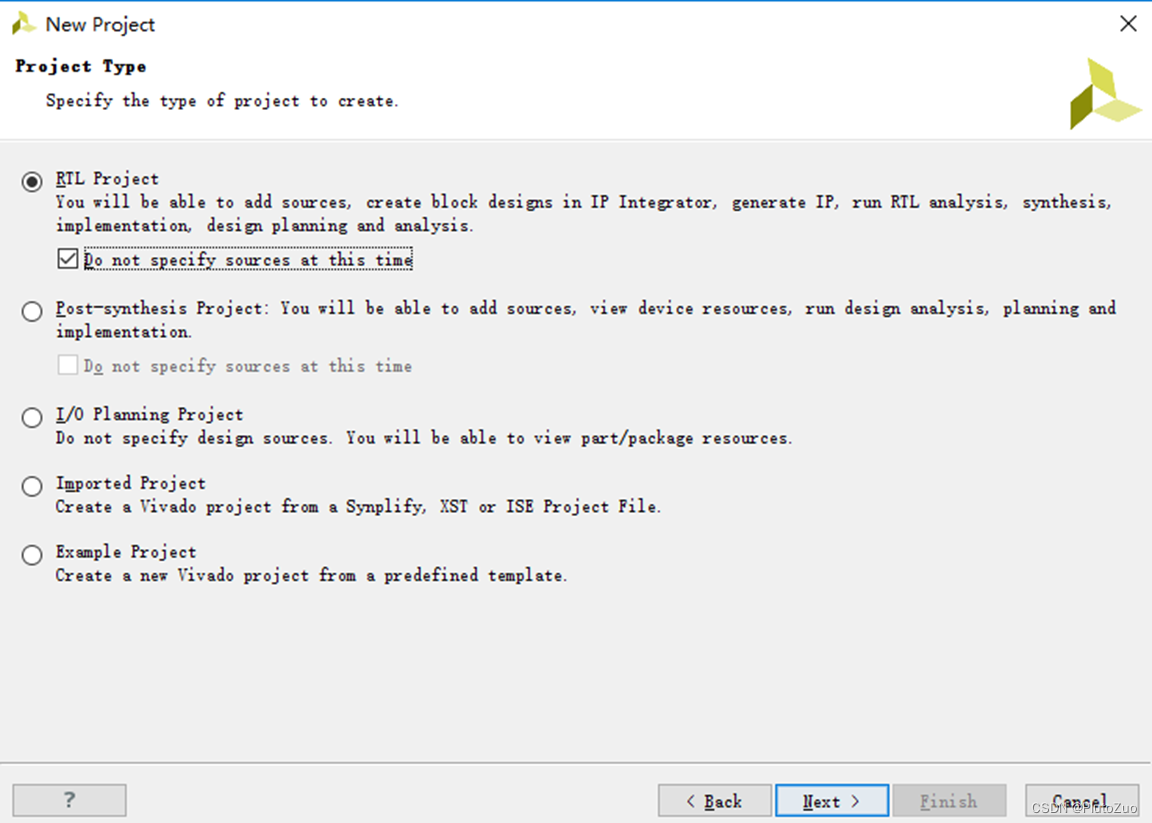

4.选择RTL Project

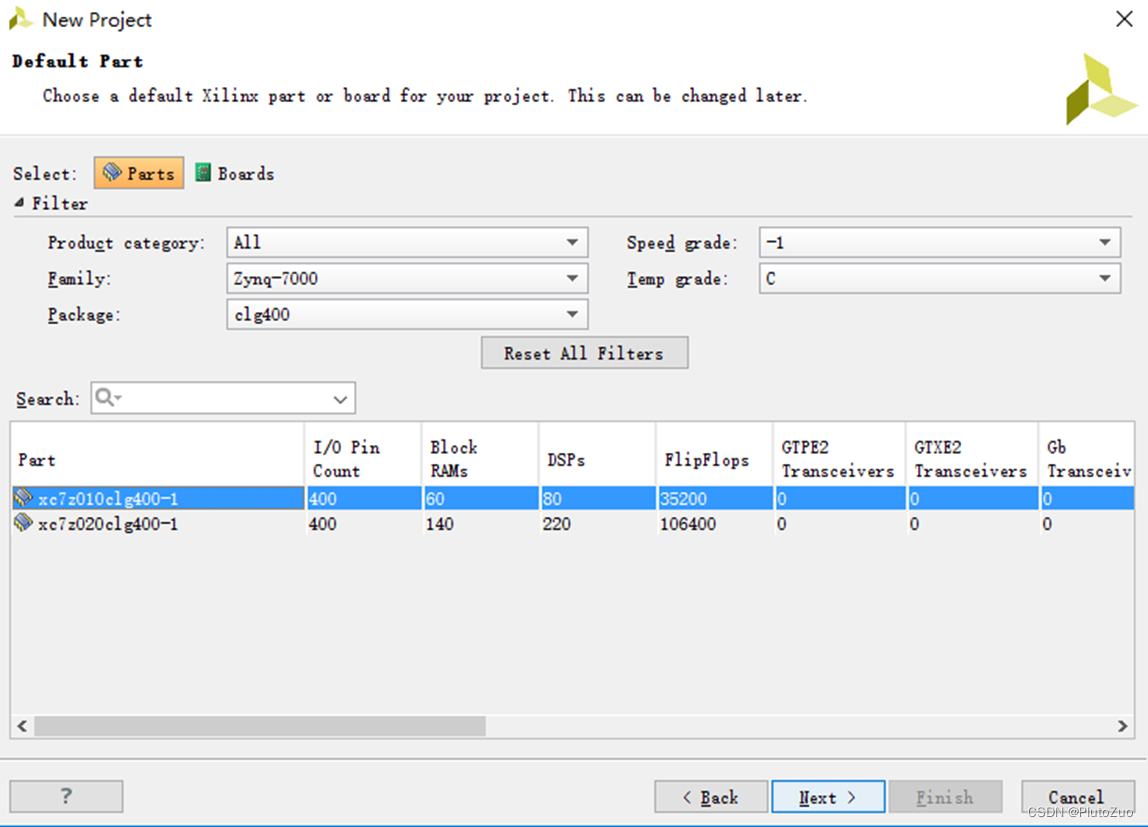

5.选择FPGA设备

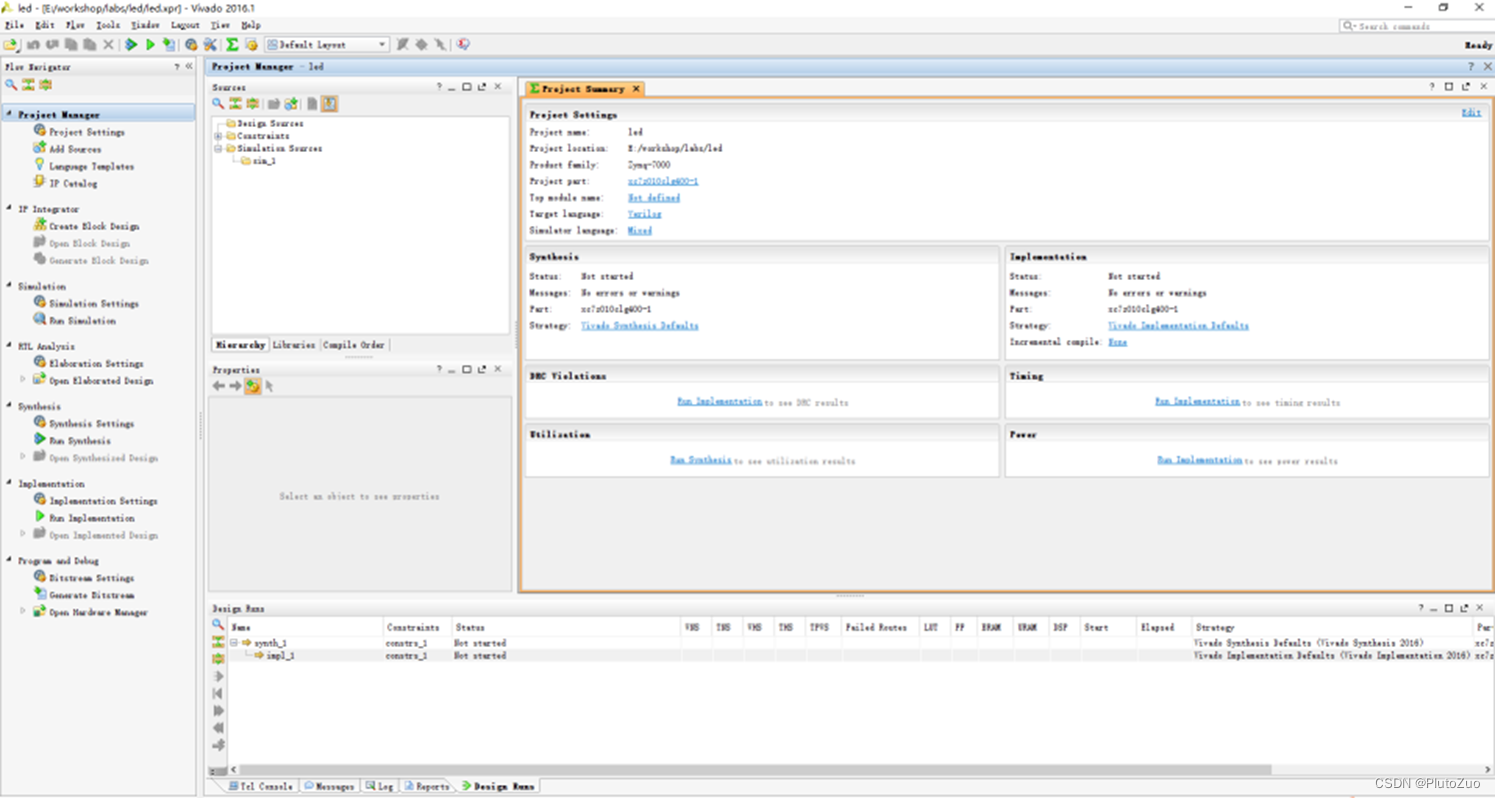

6.工程创建完成后

7.开始编写verilog代码

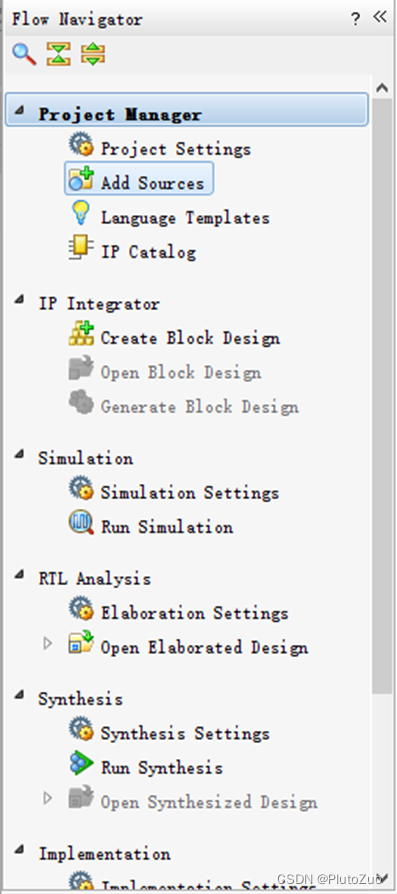

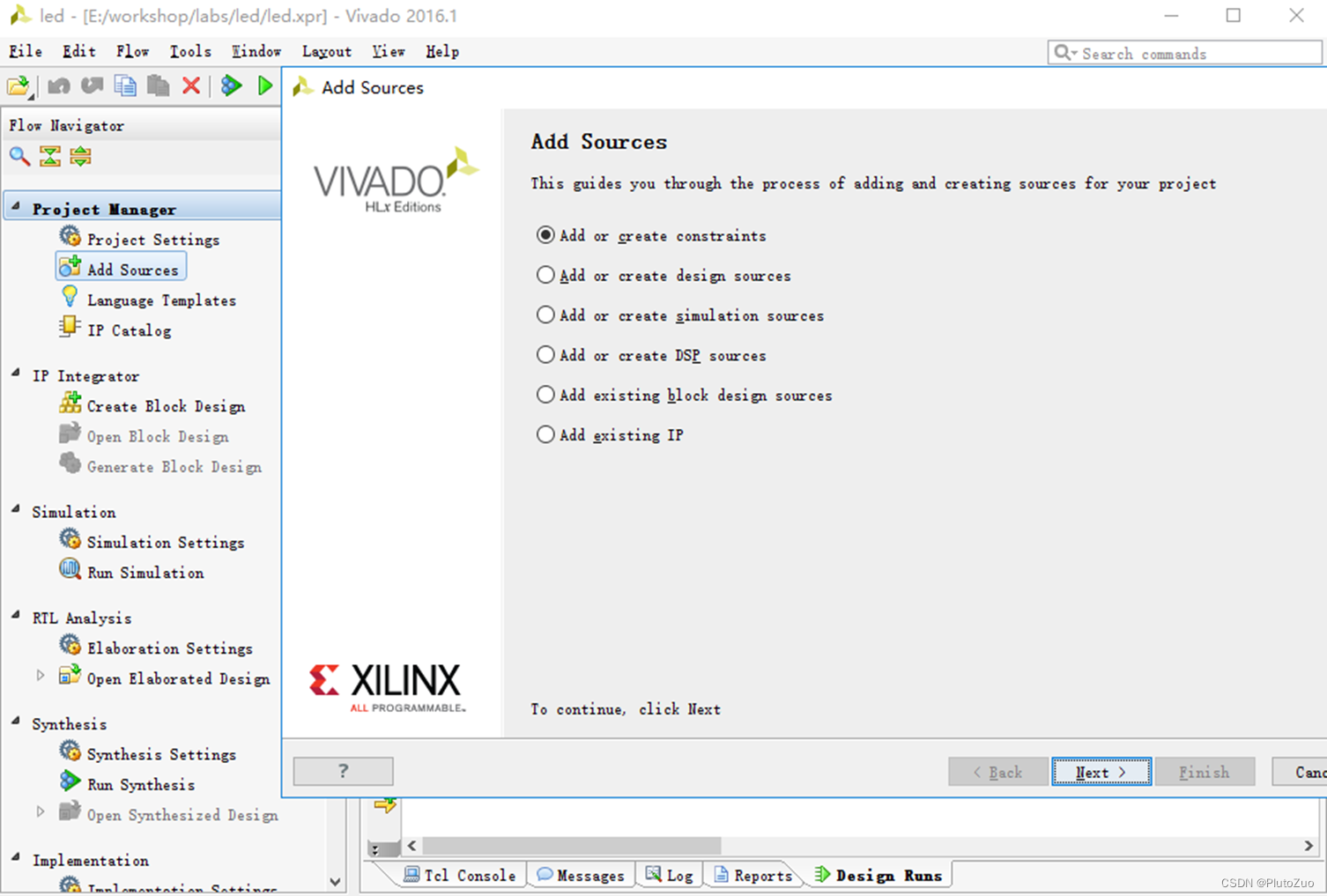

第一步:点击Add Sources按钮

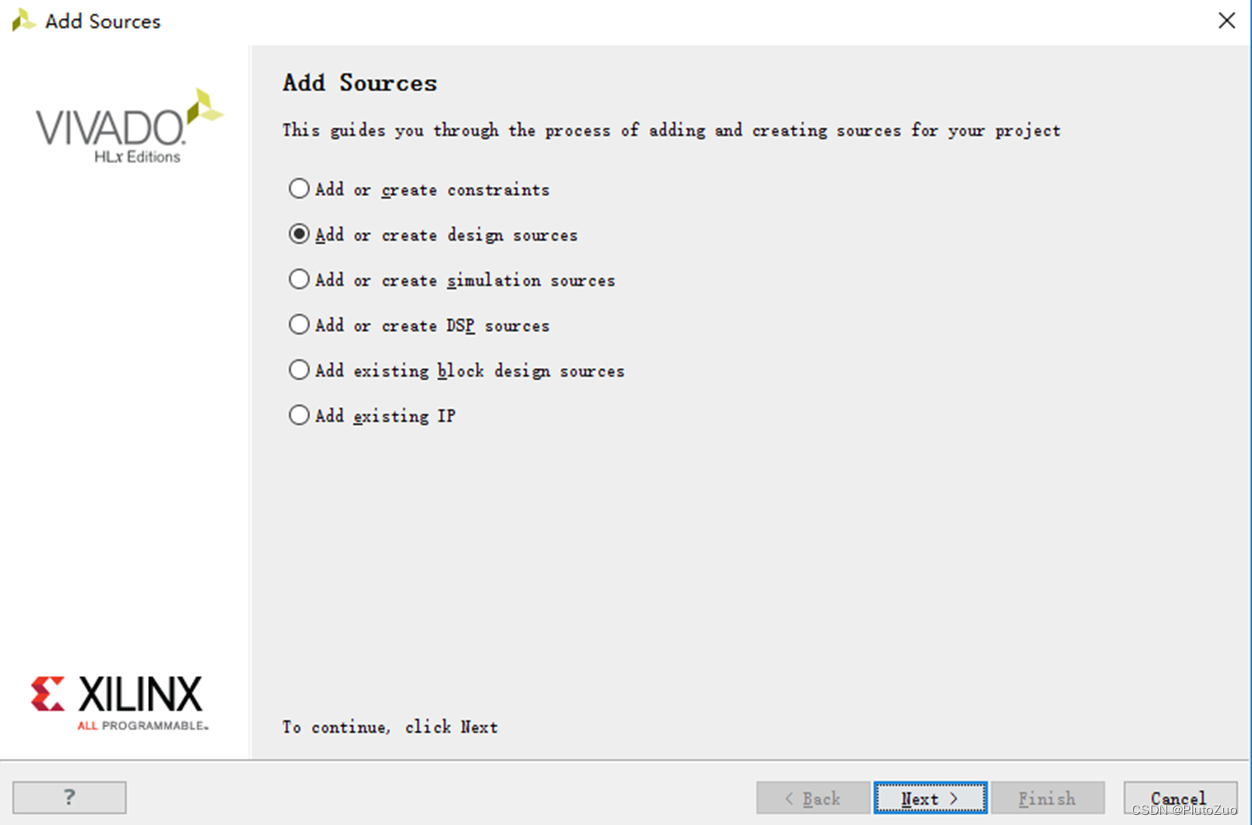

第二步:选择add or create design sources按钮,即添加设计文件

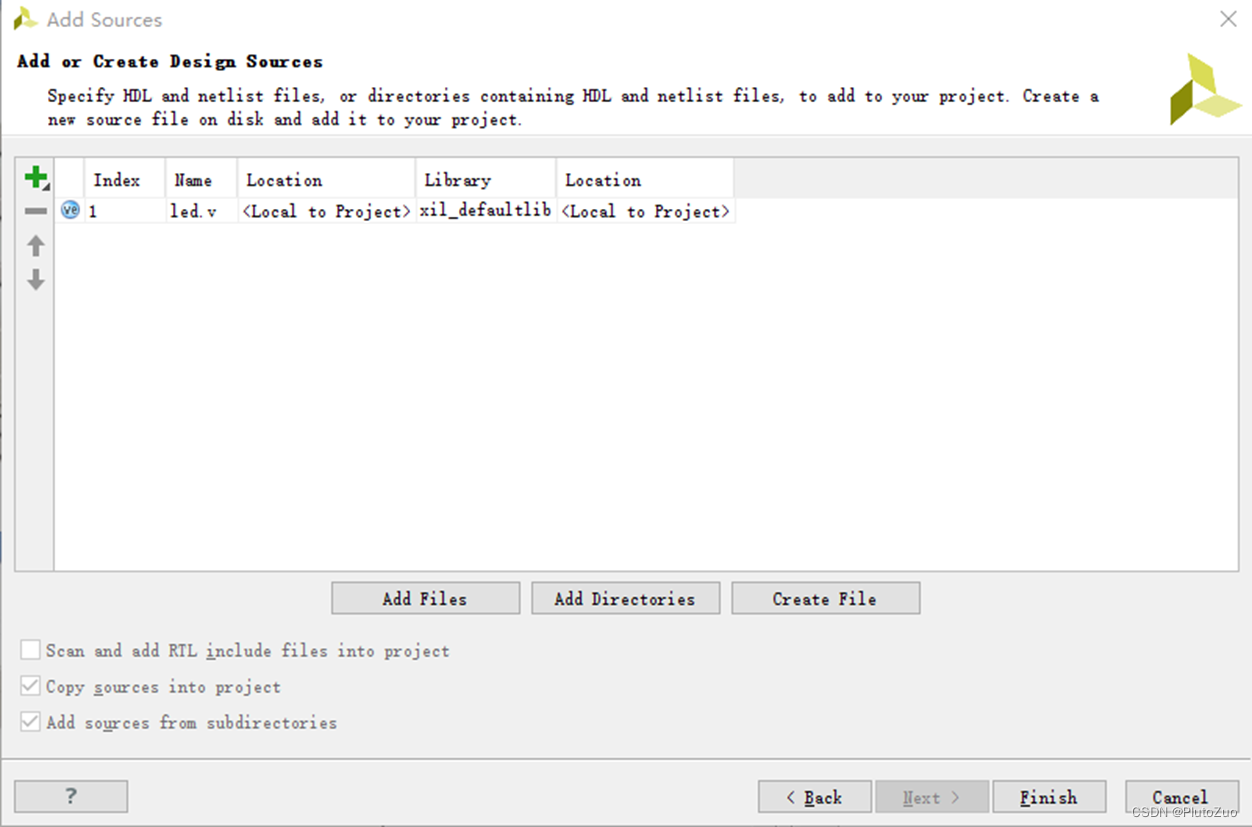

第三步:选择create file

文件新建完成后:

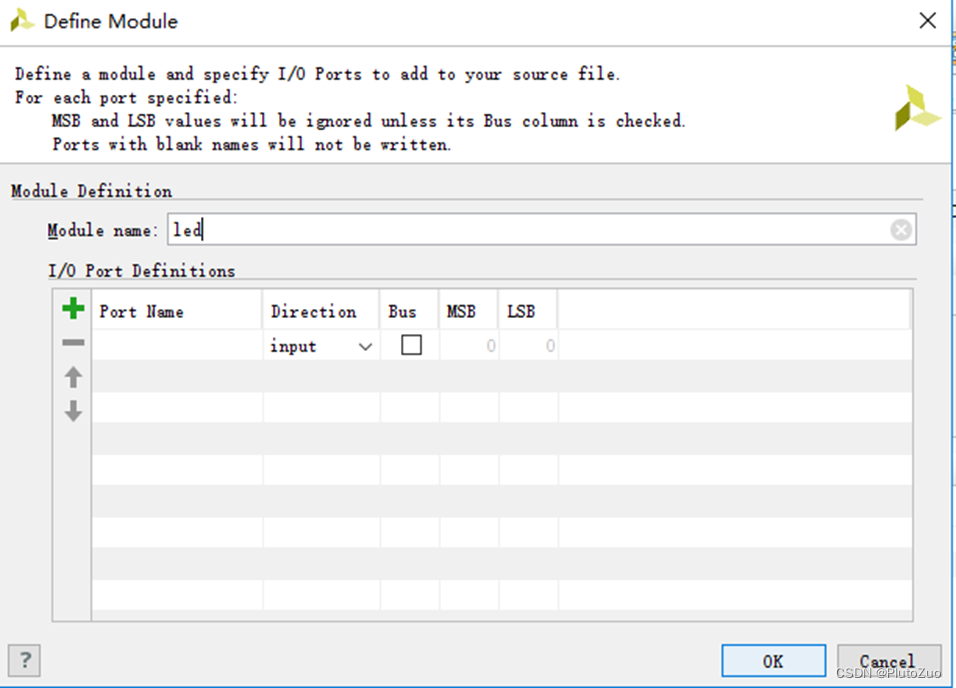

此时可以定义I/O端口,我们选择自己在程序中编写。

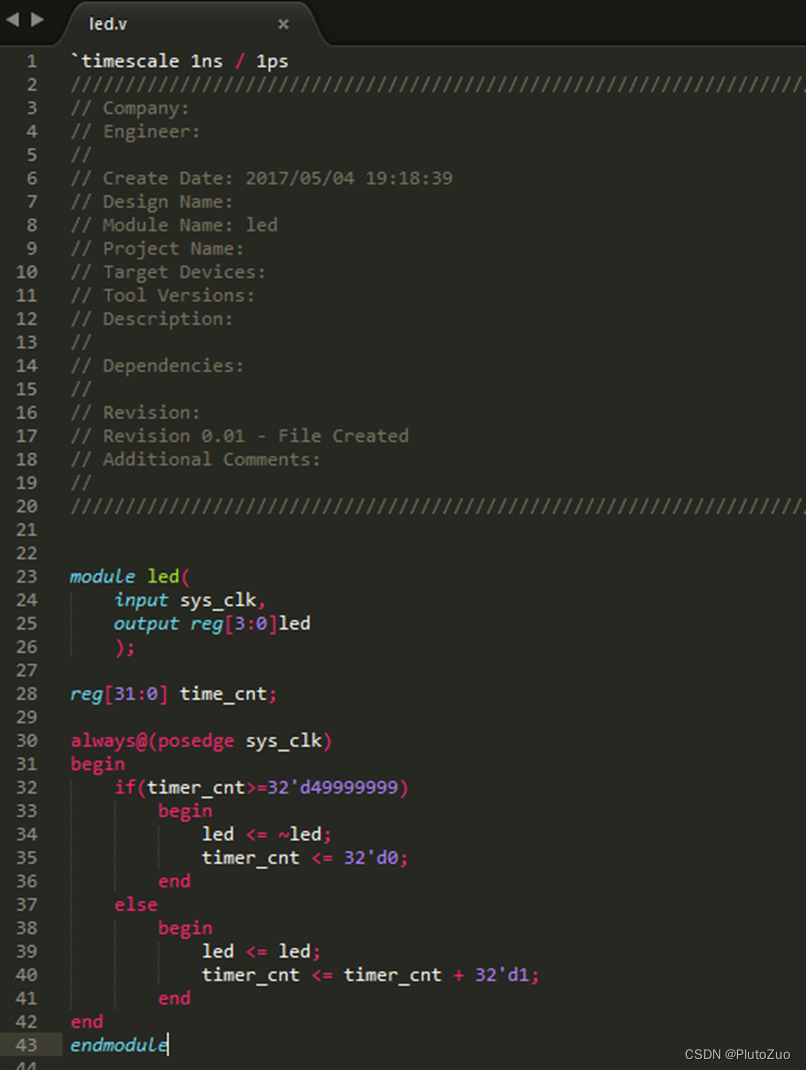

第四步:在编辑器中编写verilog程序

8.添加XDC管脚约束文件

XDC文件里主要是完成管脚的约束,时钟的约束,以及组的约束

第一步:新建约束文件

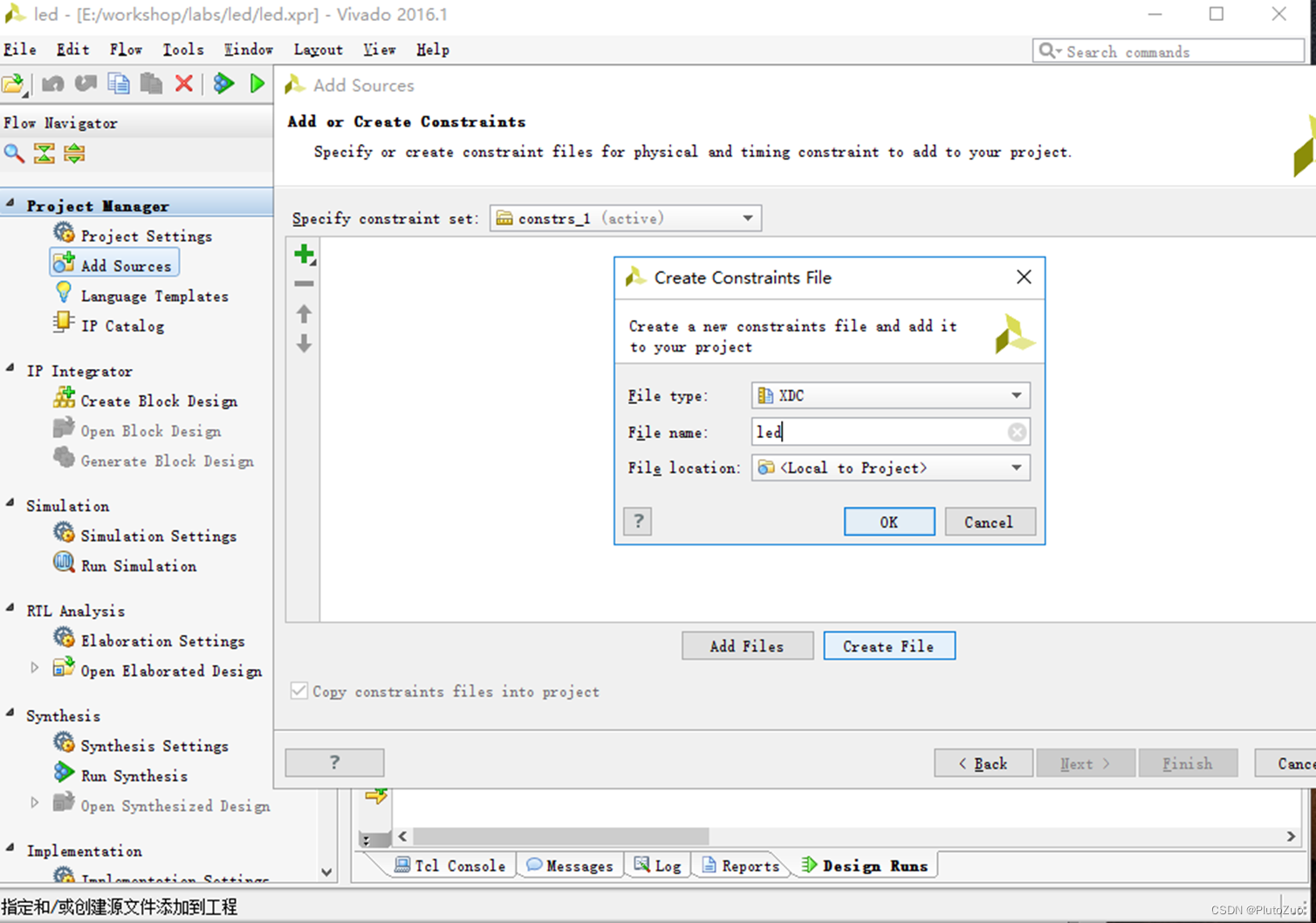

第二步:创造约束文件

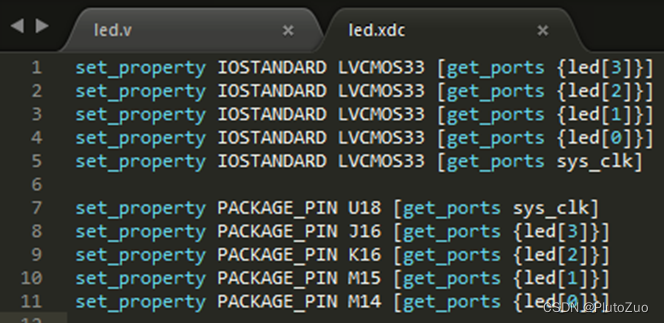

第三步:编辑管脚约束文件

其中,

Set_property PACKAGE_PIN “引脚编号” [get_ports “端口名称”]

Set_property IOSTANDARD “电压” [get_ports “端口名称”]

9.编译

第一步:运行Run Synthesis 综合

第二步:运行Run Implementation 布局布线

第三步:运行Generate Bitstream 生成bit文件

10.下载和调试

运行Hardware Manager。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/436969

推荐阅读

相关标签