- 1【Redis 神秘大陆】008 常见Java客户端

- 2牛客网【测试&测开】面经大全_牛客网测试开发面经

- 3知识图谱与知识图谱的融合与结合

- 4spring-boot-starter-jdbc与数据访问_spring-boot-starter-data-jdbc

- 5C++ 用DEV-C++建一个Windows窗口程序带文本框和命令按钮_dev-c++ windws application教学

- 6关于Unity中天空盒的使用

- 7怎么设置mysql忽略大小写_mysql设置不区分大小写

- 8黑马程序员-C语言-基本介绍和原理_黑马程序员c语言

- 9【消息中间件RabbitMQ 】:简单模式和Work queues_rabbitmq 简单模式和工作队列模式

- 10网络安全浏览器工作原理_安全浏览器密码模块

Verilog刷题[hdlbits] :Always case_verilog always case

赞

踩

题目:Always case

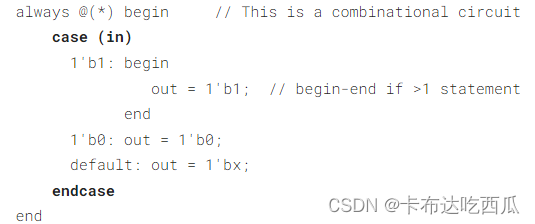

Case statements in Verilog are nearly equivalent to a sequence of if-elseif-else that compares one expression to a list of others. Its syntax and functionality differs from the switch statement in C.

Verilog中的Case语句几乎等同于if-else -else序列,它将一个表达式与其他表达式的列表进行比较。它的语法和功能不同于C中的switch语句。

-

The case statement begins with case and each “case item” ends with a colon. There is no “switch”.

case语句以case开头,每个“case项”以冒号结束。没有“switch”。 -

Each case item can execute exactly one statement. This makes the “break” used in C unnecessary. But this means that if you need more than one statement, you must use begin … end.

每个case项只能执行一条语句。这使得C语言中使用的“break”变得不必要。但是这意味着如果你需要多个语句,你必须使用begin…结束。 -

Duplicate (and partially overlapping) case items are permitted. The first one that matches is used. C does not allow duplicate case items.

允许重复(和部分重叠)的case项。使用第一个匹配的。C不允许重复的case项。

A bit of practice

练习

Case statements are more convenient than if statements if there are a large number of cases. So, in this exercise, create a 6-to-1 multiplexer. When sel is between 0 and 5, choose the corresponding data input. Otherwise, output 0. The data inputs and outputs are all 4 bits wide.

如果有大量的情况,Case语句比if语句更方便。因此,在本练习中,创建一个6比1的多路复用器。当sel在0 ~ 5之间时,选择相应的数据输入。否则输出0。数据输入和输出都是4位宽。

Be careful of inferring latches (See.always_if2)

小心推断latches (参见.always_if2)

组合逻辑中,如果case缺少default语句,或是自己赋值给自己的情况就会产生latch。为了避免latch产生,case需要加上default语句,覆盖所有可能。

// synthesis verilog_input_version verilog_2001 module top_module ( input [2:0] sel, input [3:0] data0, input [3:0] data1, input [3:0] data2, input [3:0] data3, input [3:0] data4, input [3:0] data5, output reg [3:0] out );// always@(*) begin // This is a combinational circuit case(sel) 3'b000: out=data0; 3'b001: out=data1; 3'b010: out=data2; 3'b011: out=data3; 3'b100: out=data4; 3'b101: out=data5; default:out=4'b0000; endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25